Fターム[5J055AX65]の内容

Fターム[5J055AX65]に分類される特許

1 - 20 / 33

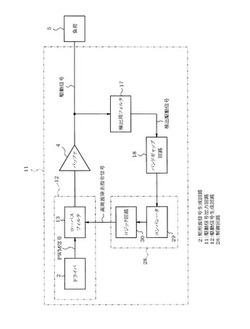

負荷駆動装置

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

電界吸収型光変調器の駆動回路

【課題】電界吸収型光変調器に供給する駆動信号の直流電圧可変に伴う駆動信号波形の劣化を防止する。

【解決手段】電圧連動可変手段30は、ドライバ回路25の終段トランジスタTRの出力用の特定端子の直流電圧と他の端子の直流電圧とを、同一方向に連動可変させて、終段トランジスタTRの動作点の変動を抑制しつつ、電界吸収型光変調器1に与える駆動信号Dの直流電圧を変化させて、駆動信号Dの直流電圧可変に伴う駆動信号波形の劣化を防止し、波形劣化の無い変調光を出力させる。

(もっと読む)

過電流検出装置

【課題】駆動に適した推奨値からずれた電気的特性を持つ負荷を駆動した場合でも誤検出を極力防止する。

【解決手段】しきい値生成回路11は、抵抗13、14にしきい値生成電流ITH、ITLを流してしきい値電圧VTH、VTLを生成し、コンパレータ12はシャント抵抗7の検出電圧Vaと比較して過電流検出信号Scを得る。しきい値補正回路17は、平均負荷電流、負荷電流の交流変化分、電源電圧VBが大きいほどしきい値電圧VTH、VTLを増やし、負荷4の温度が低いほどしきい値電圧VTH、VTLを増やす。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】スイッチ部と、駆動回路と、電源回路と、を備えた半導体スイッチが供給される。前記スイッチ部は、共通端子と複数の高周波端子との接続を切り替える。前記駆動回路は、端子切替信号に基づいて前記スイッチ部に制御信号を出力する。前記電源回路は、温度に応じて変化する基準電位基づいて、前記制御信号の電位であって温度制御された第1の電位を生成して前記駆動回路に出力する。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

適応型優先順位スキームを適用するためのクロスバー回路、およびそのようなクロスバー回路の動作方法

【課題】クロスバー回路のコンフリクトを解決する。

【解決手段】クロスバー回路はデータ入力経路12およびデータ出力経路50のアレイを有し、各交差点にはルーティング値を記憶するようにプログラム可能な構成記憶回路と、伝送回路と、アービトレーション回路とを備えるクロスバーセル20が提供される。アービトレーション回路は、適応型優先順位スキームを適用するために、同じデータ出力経路と関連する他のクロスバーセルのアービトレーション回路と組み合わせて動作して、該複数のビット線上の電圧を選択的に修正するように動作可能である。同じデータ出力経路に複数の伝送要求がある場合、同じデータ出力経路と関連する唯一のクロスバーセルの構成記憶回路は、第1の値にプログラムされるルーティング値を有し、適応型優先順位スキームに従い複数の伝送要求間のコンフリクトを解決する。さらに、各クロスバーセルは優先順位記憶回路を備える。

(もっと読む)

スイッチングゲートドライバ

【課題】スイッチングゲートドライバにおいて、スイッチング時間を短くして、スイッチング損失を低減すること。

【解決手段】本発明は、IGBT素子のスイッチングゲートドライバであって、IGBT素子のゲート電流を制御するための抵抗部、及び、前記IGBT素子のコレクタ−エミッタ間の電圧に応じて、前記抵抗部の可変抵抗を制御するための制御信号を前記抵抗部に出力する電圧検針部を含むスイッチングゲートドライバを提供する。

(もっと読む)

スイッチング素子の駆動回路

【課題】ブリッジ回路を構成する高速スイッチング素子を駆動対象とする場合でも、セルフターンオンの発生を防止できる駆動回路を提供する。

【解決手段】SJ−MOSFETであるNチャネルMOSFET3H,3LによりHブリッジ回路1を構成する場合に、駆動回路21を、NチャネルMOSFET3のソースとゲートとの間に磁気結合構造22を設け、NチャネルMOSFET3Hがターンオンした際に、オフ状態に維持されるNチャネルMOSFET3Lの寄生ダイオード5Lに短絡電流が瞬間的に流れると、NチャネルMOSFET3Lのソースに発生する電圧変動に基づいてゲートに誘導される電圧変動を打ち消すため、磁気結合構造22Lを、PNPトランジスタ8LのコレクタとNチャネルMOSFET3のゲートとの間を接続する駆動側配線24Lを、NチャネルMOSFET3Lのソース配線23Lに対して同相で磁気結合させて構成する。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

駆動回路、当該駆動回路を具備する表示装置、及び当該表示装置を具備する電子機器

【課題】チャネルが非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる際、しきい値電圧の変動の程度に応じてしきい値電圧を補正する駆動回路を提供することを課題の一とする。

【解決手段】半導体層の上下に絶縁層を介して配置された第1のゲート及び第2のゲートを有する単極性のトランジスタで構成される駆動回路において、第1のゲートには、トランジスタのスイッチングを制御するための第1の信号が入力され、第2のゲートには、トランジスタのしきい値電圧を制御するための第2の信号が入力され、第2の信号は、トランジスタのソースとドレインとの間を流れる電流を含む、駆動回路の消費電流の値に応じて制御されるものとする。

(もっと読む)

負荷駆動制御装置及び負荷駆動制御方法

【課題】負荷を駆動するスイッチング素子を適正な温度範囲で駆動させる技術を提供する。

【解決手段】通常制御状態では、MCS20は、電源電圧や指示値等に基づき、モータ60の動作状態をPWM駆動、DC駆動及び出力停止に遷移させる。MCS20は、自己診断出力回路40の出力や温度検出回路70の出力のモニタリングの結果、異常が発生していると判断した場合、MCS20はモータ60のモータ制御状態を、フェイルセーフ制御Iに遷移させる。ここで、PWM駆動中であれば、MCS20は、温度検出回路70の出力に基づいてIPS30の温度を算出し、所定温度以上、例えば110度以上であると判断すると、モータの駆動態様をPWM駆動からDC駆動へと遷移させる。

(もっと読む)

ゲート駆動回路

【課題】主スイッチング素子のターンオフ,ターンオン動作を、コンデンサを用いることで高速化しスイッチング損失を低減させる。

【解決手段】主スイッチング素子1の例えばオン期間中に、電源電圧11によりコンデンサ15を充電し、このコンデンサ15に蓄積された電圧を、主スイッチング素子1がオフする際の逆バイアス電源として用いることより、特に負電圧用の電源を用いることなく高速なターンオフ動作を可能にし、スイッチング損失の低減化を図る。

(もっと読む)

電圧増幅出力回路およびこれを使用した表示装置の駆動装置

【課題】

本発明は、電圧増幅出力回路およびこれを使用した液晶表示装置の駆動装置に関する。 本発明によって、発熱特性およびスルーレート(Slewrate)が優れた電圧増幅出力回路およびこれを使用した液晶表示装置の駆動装置を実現することができる。

【解決手段】

本発明は、第1入力端に入力される階調電圧および第2入力端に入力されるフィードバック信号に対応する第1および第2信号を生成して、第1および第2信号によってオン/オフ駆動される第1および第2スイッチを使用して第1電圧を出力する増幅部、第1および第2信号に対応してオン/オフ駆動される第3および第4スイッチを使用して生成されるデータ信号を前記画素に印加する出力部、第1および第2信号を第3および第4スイッチに選択的に供給する出力マルチプレクサ、および第1電圧またはデータ信号のうちのいずれか一つを選択的に第2入力端に供給するフィードバック回路部を含む電圧増幅出力回路を提供する。

(もっと読む)

1 - 20 / 33

[ Back to top ]