Fターム[5J055CX24]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 負荷・用途 (2,057) | 信号用、通信用 (591)

Fターム[5J055CX24]の下位に属するFターム

外部信号伝送用、同軸ライン駆動等 (24)

内部信号伝送用、バス駆動等 (43)

Fターム[5J055CX24]に分類される特許

1 - 20 / 524

信号切替回路およびA/D変換装置

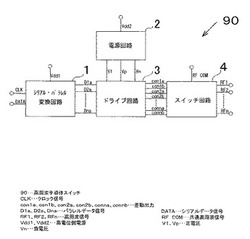

高周波半導体スイッチ、端末装置

【課題】スイッチ回路の誤動作の発生を防止する。

【解決手段】一つの実施形態によれば、シリアル・パラレル変換回路は、第一の高電位側電源が供給され、シリアルデータ信号が入力され、パラレルデータ信号を生成する。電源回路は、第二の高電位側電源が供給され、第二の高電位側電源に基づいて第一の正電圧、第二の正電圧、及び負電圧を生成する。ドライブ回路は、第一の正電圧が電源として供給され、パラレルデータ信号が入力されるインバータと、第二の正電圧及び負電圧が電源として供給され、パラレルデータ信号及びインバータの出力信号が入力される差動型レベルシフタを含むレベルシフト回路が設けられ、第二の正電圧をハイレベルの信号としてスイッチ回路に出力し、負電圧をローレベルの信号としてスイッチ回路に出力する。

(もっと読む)

電界吸収型光変調器の駆動回路

【課題】電界吸収型光変調器に供給する駆動信号の直流電圧可変に伴う駆動信号波形の劣化を防止する。

【解決手段】電圧連動可変手段30は、ドライバ回路25の終段トランジスタTRの出力用の特定端子の直流電圧と他の端子の直流電圧とを、同一方向に連動可変させて、終段トランジスタTRの動作点の変動を抑制しつつ、電界吸収型光変調器1に与える駆動信号Dの直流電圧を変化させて、駆動信号Dの直流電圧可変に伴う駆動信号波形の劣化を防止し、波形劣化の無い変調光を出力させる。

(もっと読む)

スイッチ

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

モード選択回路

【課題】設定に用いる端子数を減らすことができ、且つ回路規模の小型化を図りうるモード選択回路を提供する。

【解決手段】モード選択回路1には、通電経路5の電流状態に応じた定電流を複数の電流比較経路7に流す定電流生成回路9が設けられている。更に、複数の電流比較経路7に対してそれぞれ比較電流を流す定電流源40が設けられ、定電流源40によって複数の電流比較経路7に流される比較電流が互いに異なる電流値となるように構成されている。更に、電流比較部20は、それら複数の各比較電流と前記定電流とを比較したときの比較結果をモード判定部30に出力しており、モード判定部30はこのような比較結果を得ることで通電経路5の状態に応じたモードに設定している。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

駆動回路および宅側装置

【課題】光信号を送信するための発光素子の駆動に寄与しない無効電流を低減することが可能な駆動回路および宅側装置を提供する。

【解決手段】駆動回路52は、光信号を送信するための発光素子LDを含む発光回路75における発光素子LDにバイアス電流を供給するためのバイアス電流供給回路68と、送信すべきデータの論理値に応じた大きさの変調電流を発光素子LDに供給するための変調電流供給回路63とを備える。変調電流供給回路63は、データの論理値に応じて、発光素子LDに電流を供給するか否かを切り替えるための差動駆動回路41と、差動駆動回路41の差動出力間に接続された終端抵抗とを含む。差動駆動回路41および発光回路75は直流結合されており、差動駆動回路41が発光素子LDに供給する上記電流の電源は発光回路75から供給される。

(もっと読む)

半導体スイッチ回路

【課題】簡易な構成によりスイッチ切替時間のさらなる高速化を図る。

【解決手段】外部から供給される外部制御信号に応じて、高周波スイッチ回路101のFET1,2のオン、オフ状態を制御する駆動制御信号を出力する論理制御回路104と、FET1,2が論理制御回路104によりオフ状態からオン状態とされる際にパルス電圧を出力する切替加速回路102,103とは、それぞれの出力信号が共にFET1,2の駆動制御信号として、それぞれへ印加可能に設けられ、論理制御回路104は、定常状態においてFET1,2をオン状態とする電源電圧とほぼ等しい駆動制御信号を出力するよう構成され、切替加速回路102,103は、ピークが電源電圧を超えるパルス電圧を出力する一方、そのパルス電圧が論理制御回路104の出力信号の電圧レベルを下回った際には、その出力が遮断されるよう構成されたものとなっている。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

接点入力回路

【課題】閾値電圧設定回路の抵抗器の開放故障に対するフェールセーフ性を確保し、且つ、検査信号がオフ制御されたときの消費電力を低減できる接点入力回路の実現。

【解決手段】接点入力回路10は、接点の開閉状態を示す入力信号が入力される正入力端子11と負入力端子12との間に、第1抵抗器R1、第3抵抗器R3及び第4抵抗器R4が直列接続されている。そして、直列接続された第3抵抗器R3及び第4抵抗器R4に対して、第2抵抗器R2、第1フォトカプラP1のフォトダイオードPd1及び第2フォトカプラP2のフォトトランジスタPt2が順方向に直列接続されてなる第2回路部16が並列接続されている。また、第4抵抗器R4に対して、第2フォトカプラP2のフォトダイオードPd2及び第3フォトカプラP3のフォトトランジスタPt3が順方向に直列接続されてなる第1回路部15が並列接続されている。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

RFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器

【課題】スイッチング素子の個数を減らし、スイッチング素子を送受信時共有して、RFアンテナスイッチのサイズを減らすと共に、小型化及びワンチップ化にさらに応じるRFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器を提供する。

【解決手段】アンテナ1と、少なくとも一つの送信段2及び少なくとも一つの受信段3を備える複数の入出力段と、少なくとも一つの送信段2とアンテナ1側の共通ノード4、5との間の送信経路上に配置され、制御信号によって信号を伝達する少なくとも一つの送信スイッチブロック10と、受信段3と共通ノード4、5との間の受信経路上に配置され、制御信号によって伝達する少なくとも一つの受信スイッチブロック30、30a、30bと、スイッチング素子を共有して各々の送信及び受信動作と同期してオン動作する共用送受信スイッチブロック50とを含む。

(もっと読む)

半導体スイッチ回路

【課題】高いESD保護耐圧を確保しつつ、ESD保護素子の静電容量を極力小さくし、しかも、集積化の際における占有サイズを小さくする。

【解決手段】ESD保護回路103は、共通端子41とグランドとの間に設けられており、共通端子41側から順に、ESD保護スイッチ素子としての複数の直列接続された電界効果トランジスタ31−1〜31−4と、逆接続された一組のESD保護素子としてのダイオード32−1,32−2が直列接続されると共に、電界効果トランジスタ31−1〜31−4は、ゲートが相互に接続されてグランドに接続されており、ESD保護素子のダイオード32−1,32−2による静電容量を低減し、高いESD保護耐圧の確保が可能となっている。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

自動補正機能付き周期タイマ

【課題】 衛星搭載コンポーネントのうち、衛星内部に配信される基準タイミングに同期して周期動作を行うようなコンポーネントでは、オシレータが有するクロック精度誤差のため、周期タイミングにずれが生じることがあり、これを回避する自動補正機能付き周期タイマを得る。

【解決手段】 基準タイミングの間隔を内部クロックによりカウントし、カウント値に従ってコンポーネントの周期タイミングを生成する。ユーザは予め周期タイミングの設定を「基準タイミングに対する分割数」として2の冪乗の値で与えて与えておき、基準タイミングの間隔のカウント値を分割数に従いビットシフトすることで周期タイマのカウント値を算出し、周期タイミングを生成する。

(もっと読む)

1 - 20 / 524

[ Back to top ]