Fターム[5J055EY02]の内容

Fターム[5J055EY02]に分類される特許

1 - 20 / 33

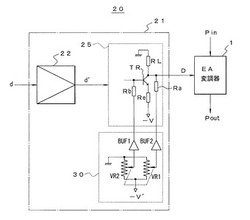

電界吸収型光変調器の駆動回路

【課題】電界吸収型光変調器に供給する駆動信号の直流電圧可変に伴う駆動信号波形の劣化を防止する。

【解決手段】電圧連動可変手段30は、ドライバ回路25の終段トランジスタTRの出力用の特定端子の直流電圧と他の端子の直流電圧とを、同一方向に連動可変させて、終段トランジスタTRの動作点の変動を抑制しつつ、電界吸収型光変調器1に与える駆動信号Dの直流電圧を変化させて、駆動信号Dの直流電圧可変に伴う駆動信号波形の劣化を防止し、波形劣化の無い変調光を出力させる。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

負荷駆動装置

【課題】スイッチング素子の立ち上がりの速度を高速に維持しつつ、スイッチング素子を駆動するドライバ回路の消費電流を削減することができる負荷駆動装置を提供する。

【解決手段】負荷10に接続されるスイッチング素子50と、定電流を生成する定電流生成部30と、定電流生成部30から流れ込む定電流の大きさに応じたオン時間でスイッチング素子50をオンするドライバ回路40と、を備えた構成とする。そして、定電流生成部30は、スイッチング素子50がオンするオン時間に達するまではドライバ回路40に第1電流量の大きさの定電流を流すことでスイッチング素子50の立ち上がりの速度を高速に維持する。また、定電流生成部30は、スイッチング素子50がオンするオン時間が経過した後はドライバ回路40に第1電流量よりも小さい第2電流量の定電流を流すことでドライバ回路40の消費電流を削減する。

(もっと読む)

センス機能付きパワー半導体デバイス

【課題】センス機能付きパワー半導体デバイスのメイン領域とセンス領域の電流スイッチタイミングや過渡特性のずれを小さくするようゲート駆動回路で補正して電流検出の精度を向上させるセンス機能付きパワー半導体デバイスを提供する。

【解決手段】ゲートパルス発生回路(21)から出力されるゲート駆動信号が、ゲート抵抗値補正回路1(22)及びゲート抵抗値補正回路2(23)の各補正抵抗を経由してセンスゲート端子Gs 及びメインゲート端子Gm 並びにMPU(24)の入力端へ出力される。各ゲート抵抗値補正回路(22,23)の補正抵抗値は、駆動時の負荷電流値、各ゲート電圧値以外に、電源電圧値および素子温度値のうちいずれかの条件を測定し、測定した条件に応じてMPU(24)で最適な補正抵抗値を計算、または内蔵するメモリから最適な補正抵抗値を呼び出し、各ゲート抵抗値を補正する。

(もっと読む)

入力セレクタおよび信号処理回路

【課題】さまざまな入力形式の信号に柔軟に適応可能な汎用性の高い入力セレクタを提供する。

【解決手段】第1抵抗R1〜第4抵抗R4は、それぞれの第1端子が対応する入力ポートPi1〜Pi4に接続される。第1スイッチSW1〜第4スイッチSW4はそれぞれ、対応する抵抗と第1演算増幅器10の反転入力端子の間に設けられる。第5スイッチSW5、第6スイッチSW6はそれぞれ、対応する抵抗と、第2演算増幅器12の反転入力端子の間に設けられる。第5抵抗R5および第7スイッチSW7は第1演算増幅器10の出力端子と第2演算増幅器12の反転入力端子の間に直列に設けられる。第6抵抗R6は第1演算増幅器10の出力端子と反転入力端子の間に設けられ、第7抵抗R7は第2演算増幅器12の出力端子と反転入力端子の間に設けられる。

(もっと読む)

半導体集積回路装置

【課題】出力トランジスタの過電流を簡略な回路構成で抑制する。

【解決手段】半導体集積回路装置70の過電流保護回路30には、過電流検出部1と過電流制御部2が設けられる。過電流検出部1には、電流源11乃至13、NPNトランジスタQ1乃至Q3が設けられる。NPNトランジスタQ1及びNPNトランジスタQ2は第1のカレントミラー回路を構成し、NPNトランジスタQ2のコレクタ側から過電流検出信号Skkを出力する。NPNトランジスタQ1及びNPNトランジスタQ3は、第2のカレントミラー回路を構成し、NPNトランジスタQ3のコレクタ側から過電流制御信号Sksを過電流制御部2に出力する。過電流保護回路30は、出力トランジスタMDT1に流れる過電流を出力トランジスタMDT1のソースと抵抗R1の間で検出して、過電流を抑制する。

(もっと読む)

スイッチングゲートドライバ

【課題】スイッチングゲートドライバにおいて、スイッチング時間を短くして、スイッチング損失を低減すること。

【解決手段】本発明は、IGBT素子のスイッチングゲートドライバであって、IGBT素子のゲート電流を制御するための抵抗部、及び、前記IGBT素子のコレクタ−エミッタ間の電圧に応じて、前記抵抗部の可変抵抗を制御するための制御信号を前記抵抗部に出力する電圧検針部を含むスイッチングゲートドライバを提供する。

(もっと読む)

プリエンファシス機能を含む出力回路と半導体装置

【課題】プリエンファシス機能を有する出力回路において、デエンファシス時における差動出力信号のコモンモード電圧のプリエンファシス時のコモンモード電圧からの変動を抑制する。

【解決手段】入力信号とその相補信号とを差動入力して差動出力し、差動出力信号のうち高電位側の出力信号にデエンファシスをかける際に、当該デエンファシス電流を供給するトランジスタ(N3、N4)に流れる電流を絞る回路(N5、N6、R3)を備え、デエンファシス時の前記出力信号のハイレベルの前記出力信号のプリエンファシス時のハイレベルからの変化量を縮減させ、デエンファシス時の前記差動出力信号のコモンモード電圧をプリエンファシス時のコモンモード電圧に近づける。

(もっと読む)

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

スイッチング回路およびスイッチング回路の制御方法

【課題】 スイッチング損失を抑制しつつ、広い帯域に存在する高調波周波数成分を低減できるスイッチング回路およびスイッチング回路の制御方法の提供。

【解決手段】 スイッチング回路1は、狙いとするノイズ低減帯域を2つの帯域に分割して両帯域の高調波周波数成分を小さくする最適波形をそれぞれ生成し、生成した2つの最適波形を1パルス毎に切り替えてパワートランジスタM1を駆動する規範電圧波形生成部3を備える。

(もっと読む)

スイッチング回路

【課題】 入力した規範電圧波形に対する出力電圧波形の追従性をさらに向上させることができるスイッチング回路を提供すること。

【解決手段】 規範電圧波形追従駆動部4へ入力する信号波形を、予めノイズ特性と損失特性を設定した波形にして出力する規範電圧波形生成部31と、規範電圧波形追従駆動部4に設けられ、カレントミラーの回路構成によりフィードバックの差動処理を行う比較部41と、規範電圧波形生成部31による規範電圧波形に対して補償を行うカレントミラー誤差補償部32を備えた。

(もっと読む)

駆動回路

【課題】電力ロスを低減しつつセンサ回路に供給される電圧の安定化を図ることができるセンサ駆動回路を安価に提供する。

【解決手段】ブリッジ回路Bに対して正電圧を供給する方向に導通するトランジスタQ1が、ブリッジ回路Bと図示しない交流電圧源との間に設けられている。ダイオードブリッジ12が、ブリッジ回路Bと図示しない交流電圧源との間に設けられ、ブリッジ回路Bに供給される交流電圧を全波整流する。比較回路13が、ブリッジ回路Bに供給された交流電圧と電圧Vthとを比較して、ブリッジ回路Bに供給される交流電圧の大きさが電圧Vthを越えないようにトランジスタQ1を制御する。

(もっと読む)

高周波回路のスイッチング方法及び高周波回路

【課題】休止時のゲート−ドレイン間の電圧が小さくなるようにし、また運転/休止の切替え時に低ドレイン電圧領域を通過させないようにする。

【解決手段】高周波回路に含まれる能動素子に対し駆動電圧を与えることにより、この能動素子の運転と休止を切り替える高周波回路及びそのスイッチング方法で、休止状態の能動素子のドレインに、定常運転レベルの電圧Vdを印加し、その後、能動素子のゲートに、定常運転レベルの電圧Vgを印加することにより運転に切り替え、一方、運転状態の能動素子のゲートに、定常運転レベルの電圧Vgに換えてピンチオフ電圧Vpを印加し、その後、能動素子のドレインに印加されている定常運転レベルの電圧Vdを切断することにより、休止に切り替える。

(もっと読む)

半導体集積回路及びLSIシステム

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

ヒューズ装置

【課題】切断したヒューズにグローバックが発生した場合にも、正確なヒューズデータを生成し得るヒューズ装置を提供する。

【解決手段】切断したグローバック検出用ヒューズf0の抵抗値と、第一の基準抵抗R0の抵抗値の差に基づく検出信号Xを生成するグローバック検出部11と、検出信号Xに基づいて抵抗値が変化する第二の基準抵抗TN9の抵抗値と、ヒューズデータ生成用ヒューズf1,f2,fnの抵抗値との比較結果をヒューズデータDAとして出力するヒューズ部13aとを備えた。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

ラダー抵抗回路、基準電圧生成回路、ドライバ、電気光学装置及び電子機器

【課題】高精度な抵抗分割を小規模な回路面積で実現できるラダー抵抗回路、基準電圧生成回路、ドライバ、電気光学装置及び電子機器を提供すること。

【解決手段】ラダー抵抗回路は、複数の抵抗ユニットRA1〜RAmn(m、nは2以上の整数)と複数の選択ユニットSLA1〜SLAmnを含む。直列に接続された抵抗ユニットRA1〜RAnは方向D1に沿って配置され、方向D1の反対方向を方向D3とする場合に、直列に接続された抵抗ユニットRAn+1〜RA2nは方向D3に沿って配置される。方向D1に直交する方向を方向D2とする場合に、抵抗ユニットRAn+1は抵抗ユニットRAnの方向D2に配置される。選択ユニットSLAiは、抵抗ユニットRAiの方向D2に配置され、抵抗ユニットRAiに対応するタップに接続される。

(もっと読む)

出力バッファ回路、差動出力バッファ回路、調整回路及び調整機能付き出力バッファ回路並びに伝送方法

【課題】消費電力、回路面積を増やすことなく、プリエンファシス量の分解能を向上することが可能な出力バッファ回路、差動出力バッファ回路、調整回路及び調整機能付き出力バッファ回路、並びに伝送方法を提供する。

【解決手段】遅延回路23と、反転回路22と、出力バッファ3〜7とを備え、伝送線路2に論理信号を送信し、伝送線路2の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路10であって、出力バッファ3はオン抵抗に可変抵抗部分12を有し、可変抵抗値の変更によりプリエンファシス量が変更される。出力バッファ3は、前段にセクレタ20を有し、オン抵抗に可変抵抗部分12を有しており、反転回路22は、セレクタ論理により出力バッファ6に入力する信号を選択可能で、データ信号を反転し、そして、セレクタ論理のセレクト信号により、タップのプリエンファシス量を調整する。

(もっと読む)

半導体集積回路装置及び半導体集積回路装置の試験方法

【課題】配線領域の増大を抑制しつつも、電源遮断回路が正常に機能しているかを試験することのできる半導体集積回路装置を提供する。

【解決手段】内部回路10と電源遮断回路20との間のノードAの仮想電源電圧VD1を比較電圧Vnに変換する電圧シフト回路40と、電源遮断回路20の電源通電動作時に高電位基準電圧を生成し、電源遮断動作時に低電位基準電圧を生成する基準電圧生成回路50が備えられる。また、電圧シフト回路40からの比較電圧Vnと、基準電圧生成回路50からの基準電圧VRとを比較して判定信号JSを生成し、その判定信号JSを出力パッド75に出力する電圧比較回路60が備えられる。

(もっと読む)

1 - 20 / 33

[ Back to top ]