Fターム[5J055FX31]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 最初に動作する検出回路の素子、回路 (2,393)

Fターム[5J055FX31]の下位に属するFターム

抵抗、分圧抵抗 (438)

ダイオード (316)

FETで構成された2端子素子 (300)

BiTrで構成された2端子素子 (40)

FET、BiTrの閾値を利用 (731)

比較器(デジタル、アナログ) (291)

Fターム[5J055FX31]に分類される特許

1 - 20 / 277

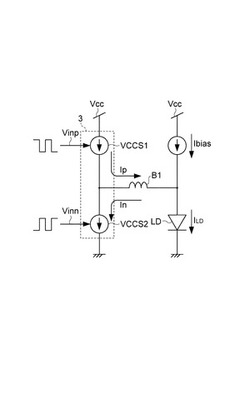

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

ソレノイドの通電制御装置

【課題】ソレノイドに流れる電流を検出するタイミングと、PWM信号を出力するタイミングとのずれを抑制可能なソレノイドの通電制御装置を提供する。

【解決手段】ソレノイドの通電制御装置100は、ソレノイド50に流れる電流の電流値の取得用の電流取得用タイマ10と、当該電流取得用タイマ10の計数結果に基づいて、ソレノイド50の通電を制御するスイッチング素子51を駆動するPWM信号の1周期内において予め設定された回数だけ電流値を取得する電流値取得部11と、PWM信号の出力用のPWM制御用タイマ20と、1周期内に取得された電流値に基づき、次の1周期にスイッチング素子51に通電する通電時間を設定し、当該設定した通電時間に応じたPWM信号を出力するPWM制御部21と、PWM制御用タイマ20の計時結果に基づき、電流取得用タイマ10の計時値を更新する計時値更新部41と、を備える。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

パワー半導体スイッチの制御回路及びその制御方法

【課題】寄生容量の影響を最少化させることのできる、パワー半導体スイッチの改良された制御方法及び制御装置を提供する。

【解決手段】パワー半導体スイッチの制御接続端信号を生成するための信号処理ユニットを備えた、パワー半導体スイッチを制御する制御回路において、少なくとも一つの半導体素子が、定められたパワー半導体スイッチのコレクタ・エミッタ電圧を越えた時に、導通作動され、半導体素子の出力端が導電性の接続線を通じて抵抗直列回路の抵抗の間の接続点と、或いは信号処理ユニットと接続されている抵抗直列回路の出力端と接続されており、半導体素子のブレークダウン電圧が、半導体素子の出力端の電位が、パワー半導体スイッチがスイッチオン状態にある時のパワー半導体スイッチの制御接続端の電位よりも高くなるように選ばれている。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

高周波スイッチモジュール

【課題】マルチバンドパワーアンプへ接続される小型の高周波スイッチモジュールを構成する。

【解決手段】高周波スイッチモジュール10は、アンテナANTに共通端子PIC0が接続する第1スイッチ素子11と、マルチバンドパワーアンプ40に共通入力端子PICt0が接続する第2スイッチ素子30を備える。第2スイッチ素子30の個別出力端子PICt2は、第1のローパスフィルタ12を介して第1スイッチ素子11の個別端子PIC11に接続し、第2のローパスフィルタ13とハイパスフィルタ102の直列回路を介して第1スイッチ素子11の個別端子PIC12に接続する。第2スイッチ素子30の個別出力端子PICt1は位相回路101とSAWデュプレクサ14を介して第1スイッチ素子11の個別端子PIC13に接続し、位相回路101とSAWデュプレクサ15を介して第1スイッチ素子11の個別端子PIC14に接続する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

回路接続性の監視を含む方法及びシステム

【課題】装置内の電流を監視する。

【解決手段】回路保護システムは、論理部108と、第1ノード10及び第2ノード20を有する電流感知装置102と、第1ノード10及び第2ノード20に接続され、電流感知装置102が感知した電流を示す電圧を論理部108に出力するように動作する電流感知回路120と、第1ノード10、第2ノード20、及び論理部108とに接続され、電流感知装置102を通る電流を誘発するように動作する接続確認部と、を含む。

(もっと読む)

半導体装置

【課題】高電位側スイッチ素子の十分な駆動電圧を実現した半導体装置を提供する。

【解決手段】半導体装置は、入力電圧用端子、出力用端子、接地電位用端子、電源電圧用端子、第1端子を有し、入力電圧用端子と出力用端子との間にソースードレイン経路を有する第1MOSを含む第1チップ、出力用端子と接地電位用端子との間にソースードレイン経路を有する第2MOSを含む第2チップ、第1MOSのゲートにその出力が接続された第1駆動回路、第2MOSのゲートにその出力が接続された第2駆動回路、電源電圧用端子に接続されたドレインと、第1端子に接続されたソースとを有するPMOSとを含む第3チップが一つのパッケージ内に封止され、第1端子と出力用端子との間に容量が接続可能とされ、第2MOSがオンとされるとき、PMOSはオンとされ、第2MOSがオフとされるとき、PMOSはオフとされる。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

負荷駆動装置

【課題】スイッチング素子の立ち上がりの速度を高速に維持しつつ、スイッチング素子を駆動するドライバ回路の消費電流を削減することができる負荷駆動装置を提供する。

【解決手段】負荷10に接続されるスイッチング素子50と、定電流を生成する定電流生成部30と、定電流生成部30から流れ込む定電流の大きさに応じたオン時間でスイッチング素子50をオンするドライバ回路40と、を備えた構成とする。そして、定電流生成部30は、スイッチング素子50がオンするオン時間に達するまではドライバ回路40に第1電流量の大きさの定電流を流すことでスイッチング素子50の立ち上がりの速度を高速に維持する。また、定電流生成部30は、スイッチング素子50がオンするオン時間が経過した後はドライバ回路40に第1電流量よりも小さい第2電流量の定電流を流すことでドライバ回路40の消費電流を削減する。

(もっと読む)

負荷駆動装置

【課題】より高速駆動に対応でき、かつ、消費電流を低減することができる負荷駆動装置を提供する。

【解決手段】ダーリントン回路によってスイッチングデバイス2を駆動するようにし、ダーリントン回路を構成する第1PchMOSFET5と第2PchMOSFET6のドレインを共にスイッチングデバイス2を構成するIGBTのゲートに接続する。これにより、第2PchMOSFET6の駆動電流もIGBTの駆動に用いることができるため、消費電流を低減できると共に、より大電流でのIGBT駆動が可能になるため高速駆動を行うことができる。また、第2抵抗4と並列的にスイッチ10を備え、このスイッチ10をプルアップ駆動時にオンさせる。これにより、プルアップ駆動時に第1PchMOSFET5のゲート−ソース間の抵抗値を低下させることが可能となり、駆動スピードが低下することを抑制することが可能となる。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

故障または異常検出機能を有するパルス増幅装置およびパルス増幅器故障検出方法

【課題】小型化が可能な故障または異常検出機能を有するパルス増幅装置を提供すること。

【解決手段】本実施形態に係る故障または異常検出機能を有するパルス増幅装置は、入力されるパルスを増幅して出力するパルス増幅器11と、パルス増幅器11の入力端子に接続され、パルス増幅器11に入力されるパルスに同期したパルス増幅器11を動作させる制御信号を形成して、この制御信号を入力端子に入力するパルス増幅器制御回路12と、パルス増幅器制御回路12に接続され、制御信号を連続波に変換する平均化回路17と、平均化回路17に接続され、平均化回路17から出力された連続波の電圧Vgaveとしきい値電圧Vsとを比較する比較回路18と、比較回路18に接続され、比較回路18から出力される差分電圧(Vgave−Vs)に基づいて、パルス増幅器11の故障、あるいはパルス増幅器制御回路12の異常を検出する警報装置23と、を具備する。

(もっと読む)

1 - 20 / 277

[ Back to top ]