Fターム[5J055GX00]の内容

電子的スイッチ (55,123) | 回路の表現形式 (6,945)

Fターム[5J055GX00]の下位に属するFターム

回路図 (2,498)

ブロック図 (1,507)

流れ図、フローチャート (182)

パルス波形図、デジタル波形図 (1,112)

アナログ波形図 (525)

特性図 (559)

素子の断面図 (252)

素子の平面図、マスク (190)

機器の見取り図 (108)

Fターム[5J055GX00]に分類される特許

1 - 12 / 12

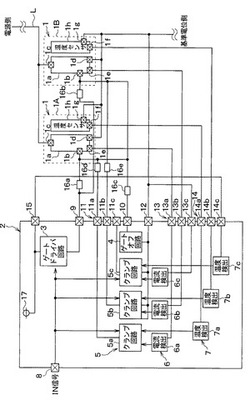

負荷駆動装置

【課題】クランプ回路が未使用状態なのか断線状態なのかを判別する。

【解決手段】温度センサ1hの出力が入力される温度検出端子14a〜14cを利用し、クランプ回路5a〜5cや温度検出回路7a〜7cの一部がパワーモジュール1に接続されないときには温度検出端子14a〜14cの電位に基づいて温度センサ1hが接続されていない断線無効状態を検出する。例えば、温度検出端子14a〜14cのうち温度センサ1hに接続されない端子に断線検出無効化閾値Vth3以上の電圧を印加することで、温度検出端子14a〜14cが温度センサ1hに接続されていないことを検出する。これにより、クランプ回路5a〜5cに接続されるクランプ端子11a〜11cの電位に基づいて断線検出を行う際に、断線状態なのか断線無効状態なのかを温度検出端子14a〜14cの電位に応じて判定できる。

(もっと読む)

出力バッファ回路

【課題】駆動能力が切替可能であると共に、ESD耐性が高い出力バッファ回路。

【解決手段】出力バッファ回路100において、第1の電源電圧と、第1の電源電圧より低い第2の電源電圧との間に直列に接続された第1導電型トランジスタTRA1と第2導電型トランジスタTRB1は、出力トランジスタを構成する。制御回路110は、トランジスタTRA1とトランジスタTRB1を相補的にオン/オフさせ、かつトランジスタTRA1とトランジスタTRB1をオンさせるときに与えるゲート電圧を複数の値間で切替可能である。

(もっと読む)

トレラントバッファ回路及びインターフェース

【課題】出力端子が出力回路の電源電圧より高電位である場合や、出力回路の電源電圧が0Vになっても出力端子から電源電圧へ電流の逆流入は発生しないトレラントバッファ回路及びインターフェースを提供すること。

【解決手段】トレラントバッファ回路100は、電源端子VDD1と出力端子102の間にソースを共有して直列接続されたPチャンネルMOSトランジスタQ111,Q112と、出力端子102と接地端子の間に接続されたNチャンネルMOSトランジスタQ113と、PチャンネルMOSトランジスタQ111のゲートに出力接続されたインバータ121と、PチャンネルMOSトランジスタQ112のゲートに出力接続されたインバータ122と、各MOSトランジスタQ111、Q112、Q113にそれぞれ第1、第2及び第3の制御信号を出力してこれらのMOSトランジスタのオン・オフを制御する制御回路130とを備える。

(もっと読む)

差動増幅装置及び過電流保護装置

【課題】オペアンプが有するオフセット電圧による影響を回避し、高精度に過電流の発生を検出することが可能な差動増幅装置及び過電流保護装置を提供する。

【解決手段】スイッチング用のMOSFET(T1)のドレインとグランドとの間に設けられる、抵抗R3,R4,R5の直列接続回路と、MOSFET(T1)のソースとグランドとの間に設けられる、抵抗R1,抵抗R2,トランジスタ(T2)の直列接続回路とを備える。更に、アンプ(AMP1)の正転入力端子a1と点aとの間に設けられた抵抗R7から電流Ixを引き抜き、且つ、アンプ(AMP1)の反転入力端子b1と点bとの間に設けられた抵抗R8から電流Iyを引き抜くことにより、点aと点bとの間に生じる電圧Vabを低減させる。

(もっと読む)

ショート検出回路及びショート/オープン検出回路並びにこれらの検出方法

【課題】電位給電部とLSI等の内部回路への給電路との短絡、開放の検出等を図る。

【解決手段】外部電源24の電位と大地電位とを抵抗素子28と抵抗素子30とで分圧した電位VR1をLSI22の内部回路へ給電路34を介して給電する。この電位VR1と第1の参照電位源18の電位(VR1+α)とを第1の差動電位比較回路12で比較する一方、電位VR1と第2の参照電位源20の電位(VR1−β)とを第2の差動電位比較回路14で比較する。比較回路12,14の比較出力に基づいて判定回路16が外部電源24又は大地電位のいずか一方が給電路34に短絡しているか否かを判定する。

(もっと読む)

A/D変換用電圧入力回路およびA/D変換用電圧入力方法

【課題】車載用負荷の駆動状態に応じて、A/D変換回路に出力する負荷側の被測定電圧の電圧レベルを変更可能とするA/D変換用電圧入力回路を提供する。

【解決手段】負荷41に対する駆動回路20のON/OFF駆動に応じてA/D変換回路13に出力する例えば接続点Cの被測定電圧の電圧レベルを変更可能とするために、接続点Cの被測定電圧を分圧する分圧用抵抗R1,R2と切替制御用トランジスタTr2,Tr3とを備え、駆動回路20をOFFにした場合、切替制御用トランジスタTr3をONにして、被測定電圧を分圧用抵抗R1,R2により略分圧した電圧をA/D変換回路13に出力し、一方、駆動回路20をONにした場合、切替制御用トランジスタTr3をOFFにして、被測定電圧をそのままA/D変換回路13に出力し、もって、駆動回路20の駆動状態如何により、電圧レベルを変更し、A/D変換回路13におけるA/D分解能を切り替える。

(もっと読む)

トリミング回路

【課題】本発明は、トリミング素子のトリミング状態に依らず、消費電流を低減することが可能なトリミング回路を提供することを目的とする。

【解決手段】本発明に係るトリミング回路は、フューズFと;電源ラインとフューズFとの間に接続されたスイッチTr1と;その出力信号がトリミングデータOUTとして引き出されるラッチ回路FFと;電源ラインとラッチ回路FFのリセット端との間に接続され、フューズFとスイッチTr1との接続ノードに現れる電圧信号aに基づいて開閉制御されるスイッチTr2と;ラッチ回路FFのリセット端と接地ラインとの間に接続され、スイッチTr1と同一の開閉状態に制御されるスイッチTr3と;電源ラインとラッチ回路FFのリセット端との間に接続され、ラッチ回路FFの出力信号gに基づいて開閉制御されるスイッチTr4と;スイッチTr1、Tr3の開閉制御信号b、c及びラッチ回路FFのセット信号dを生成する制御回路CTRLと;を有して成る構成としている。

(もっと読む)

セレクタ回路

【課題】配線面積の増大や信号波形の鈍り、信号伝達の遅延を抑制すること。

【解決手段】入力信号の導通を制御するパストランジスタ回路21a〜21dと、各パストランジスタ回路21a〜21dから出力された出力信号を配線24a,24bを介して受け付けてNAND演算をおこなうNAND回路22と、同一の配線24a,24bに接続されたすべてのパストランジスタ回路21a〜21dにより入力信号の導通が遮断された場合に、当該配線24a,24bの信号レベルを設定するpチャネルトランジスタ回路23a,23bと、導通させる入力信号を1つだけ選択するようパストランジスタ回路21a〜21dを制御する制御信号、および、配線24a,24bの信号レベルを設定するようpチャネルトランジスタ回路23a,23bを制御する制御信号を同一の入力信号に対して論理演算をおこなうことにより生成する制御信号生成回路とを備える。

(もっと読む)

半導体装置および制御方法

【課題】 消費電力を低減することができる半導体装置を提供する。

【解決手段】 半導体装置100は、電源電圧が供給される電源端子5とグランド端子6間に接続され、入力端子41乃至43から入力された信号をデコードするデコーダ103と、電源端子5とデコーダ103間を切断する電源制御回路109とを含む。電源制御回路109は、入力端子41乃至43とデコーダ103間にワイヤボンディングで並列接続される。電源制御回路109は、入力端子41乃至43から入力される信号の組み合わせのうち、デコード時に使用していない信号の組み合わせを用いてドレインスイッチFET91を制御する制御信号を生成するロジック93を含む。

(もっと読む)

出力ドライバ回路及び半導体IC

【課題】出力ドライバ回路における出力レベルの変動に伴って生じる電源線の電位の変動を抑える。

【解決手段】実装配線により外部電源に接続された電源線aと、外部へ信号を出力する出力線xと、該電源線aと該出力線xにそれぞれドレインとソースが接続され、ゲートにはスイッチ12を介して信号が入力される出力トランジスタQ1と、該電源線aの電位の変動を検出する検出器13を備え、該検出器13の出力により該スイッチ12の開閉を制御する。

(もっと読む)

電源回路

【課題】CMOS集積回路を用いた同期整流方式の電源回路などにおいて、電力消費の低減と、部品増や効率低下を伴うことなく負荷変動に対する高速応答が可能な電源回路を提供すること。

【解決手段】PWM信号をゲートに、VIN(=VDD)をソースに接続するPMOS(QP1)のドレインに接続され、VSSをソースに有す、NMOS(QN1)のドレインに接続される中間ノード電圧VMAが、NMOS(QN1)オン時に、アンダーシュートから戻って基準電位VSSレベルを越えたときこれを検出してNMOS(QN1)のゲート電圧をローレベル(オフ)にする。また、NMOS(QN1)オン時に、中間ノード電圧VMAが、アンダーシュートから基準電位VSSレベルに戻ったタイミング(ゼロ点位置)を検出することで、このゼロ点位置検出信号を負荷電流の大小を示す信号としてPWM回路33に帰還してPWM信号のパルス幅を制御し、負荷変化に対応させる。

(もっと読む)

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

1 - 12 / 12

[ Back to top ]