Fターム[5K061JJ00]の内容

受信機の回路一般 (33,509) | 回路要素、素子 (5,027)

Fターム[5K061JJ00]の下位に属するFターム

トランジスタ (120)

スイッチングダイオード (28)

水晶振動子 (22)

CPU (1,271)

メモリ、ROM (2,347)

抵抗、可変抵抗 (125)

コンデンサ、可変コンデンサ (165)

コイル、可変インダクタンス (76)

プリント基板 (34)

シールド材 (13)

液晶 (79)

発光ダイオード (9)

蛍光表示管

CRT (28)

導波管

同軸ケーブル (18)

フィルタ (676)

回路要素の配置に関するもの (14)

Fターム[5K061JJ00]に分類される特許

1 - 2 / 2

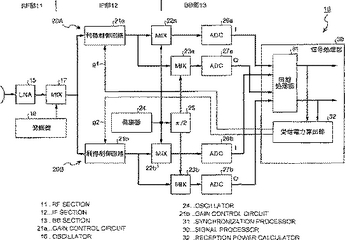

無線受信機および自動利得制御方法

受信したフレームは、共通パイロット信号の利得制御系統(20A)と、個別のデータ信号の利得制御系統(20B)に2分岐される。利得制御系統(20A)は、共通パイロット信号の利得を利得制御し、利得制御系統(20B)は、データ信号の利得を利得制御する。信号処理部(30)は、フレームの同期をとり、共通パイロット信号の利得が一定となる利得制御信号(g1)を共通パイロット信号の利得制御回路(21a)に出力し、また、データ信号の利得が一定となる利得制御信号(g2)をデータ信号の利得制御回路(21b)に出力する。利得が一定に制御されることにより、ADC(26a,26b,27a,27b)の飽和やS/N劣化を防ぐ。  (もっと読む)

(もっと読む)

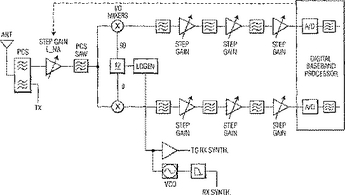

拡張遮断性能を得るため信号および干渉電力を用いる自動利得制御

アナログ部、デジタル部、これらアナログ部とデジタル部の間の少なくとも1つのA/D変換器、および、デジタル部内に少なくとも部分的に実現される無線の選択を備える無線受信機において、広帯域電力見積りが広帯域しきい値を超えたことの決定に基づいて、AGCコントローラが第1可変利得増幅器(VGA)(302)を低利得に設定する。広帯域しきい値は、A/D変換器の飽和の発生を低減させるために選択される。広帯域電力見積りが広帯域しきい値よりも小さい場合、そのとき、アナログ部内のそれぞれのVGA(302)のために、狭帯域電力見積りがそのVGA(302)に対応して狭帯域しきい値にヒステリシス値をプラスした値を超えたか否かについて決定がなされ、この場合、VGA(302)は低利得に設定され;または、狭帯域電力見積りが狭帯域しきい値からヒステリシス値を引いた値であるか否かについて決定がなされ、この場合、VGA(302)は高利得に設定される。  (もっと読む)

(もっと読む)

1 - 2 / 2

[ Back to top ]