Fターム[5L106CC00]の内容

半導体メモリの信頼性技術 (9,959) | 冗長手段 (1,538)

Fターム[5L106CC00]の下位に属するFターム

不良アドレス設定手段 (489)

アドレス、経路切換え手法 (285)

ブロック単位で切り換えるもの (109)

行又は列単位で切り換えるもの (232)

不良部のアクセス禁止 (120)

冗長機能の使用の検出 (21)

電源供給の停止又は切換え (19)

不良部の不使用 (227)

ROMの修正、ROMパッチ (7)

寿命 (17)

Fターム[5L106CC00]に分類される特許

1 - 12 / 12

半導体記憶装置

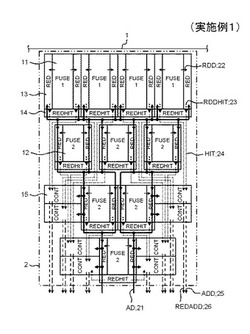

【課題】メモリ容量が大きくなってもヒューズ領域のレイアウト面積の増大を抑えることができる半導体記憶装置を提供すること。

【解決手段】所定の方向に配列した第1ヒューズ群11と、第1ヒューズ群11のヒューズ数よりも少なく第1ヒューズ群11の配列数よりも少ない配列数で所定の方向に配列した第2ヒューズ群12と、第1ヒューズ群11及び第2ヒューズ群12ごとに第1ヒューズ群11及び第2ヒューズ群12に基づく所定の信号を伝送する複数の信号線24と、を備え、第1ヒューズ群11に基づく信号線24は、第1ヒューズ群11付近から第2ヒューズ群12を迂回して第2ヒューズ群12の第1ヒューズ群11側とは反対側に配線され、第2ヒューズ群12に基づく信号線24は、第2ヒューズ群12付近から第2ヒューズ群12の第1ヒューズ群11側とは反対側に配線されている。

(もっと読む)

メモリ及び情報処理方法

【課題】不良が発生した記憶素子から情報を読み出す場合に、書き込まれるべき情報を正しく読み出すこと。

【解決手段】SpRAM1は、1ビットの情報を記憶する記憶素子2と、記憶素子2に書き込まれた情報を読み出すセンスアンプ10を備える。センスアンプ10は、所定の単位数の記憶素子2を有する記憶ブロックの内、特定の1個の記憶素子2を反転フラッグ素子として定める。そして、センスアンプ10は、反転フラッグ素子に書き込まれた1ビットの情報が、“0”又は“1”の内、いずれかを示す第1の値である場合に、他の記憶素子2に書き込まれた所定の単位数−1ビットの情報をビット反転して読み出す。一方、反転フラッグ素子に書き込まれた1ビットの情報が、第1の値とは異なる第2の値である場合に、他の記憶素子2に書き込まれた所定の単位数−1ビットの情報をそのまま読み出す。

(もっと読む)

半導体記憶装置

【課題】SRAM等のメモリにおける、微細化で顕著になるトランジスタ特性のランダムばらつきを抑制する。

【解決手段】メモリセル200と周辺回路201との両方がランダムばらつきによって特性が悪化し、ワースト特性に近い構成要素同士の組み合わせの際に、マクロレベルでの特性不良が発生する。その対策として、セレクタ203を介在させ、特性不良発生箇所にてビット線の正相と逆相とを交換する。あるいは、ビット線とセンスアンプとの組み合わせを隣接のデータ入出力部間で交換する等の施策を実施する。つまり、ワースト同士の組み合わせを解消するように、特性不良に対する救済を実施する。

(もっと読む)

集積回路および試験方法

【課題】実際の動作速度でのFMB取得が可能な集積回路および試験方法の実現。

【解決手段】メモリ18と、メモリを試験するメモリ試験回路20,22-24,41と、入出力ポート11E,11Fと、を備え、メモリ試験回路の収集したメモリの出力を入出力ポートを介して出力する集積回路であって、メモリ試験回路は、メモリの出力をラッチするラッチ回路20を備え、第1クロックPLLに応じて全アドレスをアクセスするように変化させた時のメモリの出力を、第1クロックの整数倍の周期を有するラッチ信号に応じてラッチするスキャン・ラッチ動作を行い、ラッチ信号の1周期中にラッチしたデータを入出力ポートを介して出力する転送動作を行い、ラッチ回路がラッチするメモリセルのアドレス位置を変化させて、スキャン・ラッチ動作および転送動作を繰り返し、全メモリセルの出力を外部に出力する。

(もっと読む)

不揮発性半導体記憶装置のテスト方法

【課題】 冗長部カラムエリアに割り当てられた機能の合否を判定可能な不揮発性半導体記憶装置のテスト方法を提供する。

【解決手段】 不揮発性半導体記憶装置のテスト方法は、ブロックに対する動作を制限するプロテクトフラグを、制限対象とするブロック内部の所定のページに書き込むステップと、プロテクトフラグを含むページのデータを読み出し、データレジスタに転送するステップと、データレジスタに転送されたデータの内、プロテクトフラグ以外のカラムアドレス領域のデータをマスクするステップと、データレジスタ内の不良ビットを一括検知するステップと、データレジスタ内に不良ビットが検知された場合に、不良ブロックとして登録するステップとを具備する。

(もっと読む)

半導体記憶装置、及びメモリセルテスト方法

【課題】短時間で、複数の条件下におけるメモリテストが実行可能な半導体記憶装置を提供する。

【解決手段】本発明による半導体記憶装置10は、複数のメモリセル群C00〜Cnmを有するメモリ部1と、複数の冗長メモリセル群を有する冗長メモリ部2と、メモリ部1へのアクセスを禁止し、メモリ部1内のメモリセル群にアクセスするためのアドレス信号101に応じて、冗長メモリ部2内の冗長メモリセル群を活性化する冗長回路部13とを具備する。冗長回路部13は、冗長回路不活性信号100に応じて、冗長メモリ部2にアクセス可能な通常モードと、冗長メモリ部2へのアクセスを禁止する冗長回路不活性モードとを切り替える。

(もっと読む)

DRAM装置

【課題】データ保持特性が不良なメモリセルを、冗長メモリセル領域を設けることなく救済するDRAMを提供する。

【解決手段】DRAM10は、データ保持特性が不良なメモリセルの救済アドレスを記憶し、データ読出し及び書込みの際に入力される外部アドレスが、記憶された救済アドレスと一致すると、SA救済判定信号S1を出力するセンスアンプ救済判定回路24と、SA救済判定信号S1が発生すると通常のSA選択信号S3に代えて救済用SA選択信号S2を発生するセンスアンプ制御回路25と、救済用SA選択信号S2が発生すると、対応するセンスアンプを通常よりも高い電源電圧に設定するセンスアンプ部12とを備える。

(もっと読む)

リダンダンシ演算方法及び装置並びにメモリ試験装置

【課題】メモリデバイスの不良救済に要する時間を短縮することができるリダンダンシ演算方法及び装置並びに当該装置を備えるメモリ試験装置を提供する。

【解決手段】リダンダンシ演算装置16は、Xアドレス及びYアドレスからなる二次元アドレスにより個々のメモリセルが特定される複数のメモリセルと、複数の予備セルからなる複数のスペアラインとを備えるDUT30の不良救済を行う上で必要なデータを作成する。このリダンダンシ演算装置16は、DUT30の複数のメモリセルに含まれる不良セルに関する不良セル情報を記憶するフェイルバッファ21と、フェイルバッファ21に記憶された一の不良セルと行アドレス又は列アドレスが同一である他の不良セルについて予備セルへの代替を示す確定フラグが設定されていない場合に、上記一の不良セルについての不良セル情報として確定フラグを設定する処理部24とを備える。

(もっと読む)

強誘電体メモリ装置、強誘電体メモリ装置の駆動方法、電子機器および電子機器の駆動方法

【課題】強誘電体メモリ装置のプログラム領域に書き込まれたデータの減極が生じた場合でもデータの救済を可能にする。

【解決手段】プログラム領域11、第1RAM領域13aおよび第2RAM領域13bに、同一のプログラムデータを書き込み、初回電源投入時に、比較回路17により、これらの領域の対応する番地の読み出しデータを比較し、多数決により0又は1の比較データを決定し、プログラム領域に比較データを書き戻す。その結果、プログラム領域11に記録されたデータが、実装時の熱負荷等により減極し、データ不良(不良ビット)が生じていても、当該データを救済することができ、当初プログラムを使用することができる。この後、第1RAM領域13aおよび第2RAM領域13bは、再書き込み可能なRAM領域として使用される。

(もっと読む)

半導体記憶装置

【課題】 チップ面積を増加させることなく、信頼性の向上や歩留まりの向上などの高機能を達成できる半導体記憶装置を提供する。

【解決手段】 データを書込み及び消去可能で、電圧が供給されない間も当該データを保持可能な不揮発性の半導体記憶装置であって、データに対応する静電荷をそれぞれ蓄えることが可能な第1及び第2の電荷局在部を含むメモリセルを備え、第2の電荷局在部は、第1の電荷局在部に蓄えられるべき静電荷に対応する静電荷を蓄えることにより、第1の電荷局在部を補完する。

(もっと読む)

半導体記憶装置

【課題】 高速性能の半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、それぞれ電気的書き換え可能な不揮発性メモリセルが配列され、セルデータを転送するビット線の方向に並んで配置された、互いに物理的に独立した第1及び第2のセルアレイと、前記第1及び第2のセルアレイの間に配置されてそれらにより共有されるセンスアンプ回路と、前記第1及び第2のセルアレイにそれらが論理的に1メモリプレーンとなるように割り付けられたアドレスをデコードして前記第1及び第2のセルアレイのメモリセル選択を行うデコード回路とを有する。

(もっと読む)

半導体集積回路およびそのテスト手法

【課題】 正確な冗長救済を行う。

【解決手段】 参照電圧発生回路13aの入力を電源レベル調整ヒューズ14aと内部レジスタ15aの出力とをセレクタ16aで切り替え可能な構成とする。これによって、ヒューズ14aの切断前に内部レジスタ15aの出力を用いて、ヒューズ14aの切断後と同一の内部電源電圧出力を可能とした。これにより内部電源を用いた冗長救済判定テストが可能となり、かつBISTを用いて実動作と同速のテストを実行することで、テスト時と実動作時の内部電圧誤差を解消し、マージナルビットの高精度冗長救済判定を実現する。

(もっと読む)

1 - 12 / 12

[ Back to top ]