Fターム[5L106FF00]の内容

半導体メモリの信頼性技術 (9,959) | 時期 (1,298)

Fターム[5L106FF00]の下位に属するFターム

Fターム[5L106FF00]に分類される特許

1 - 4 / 4

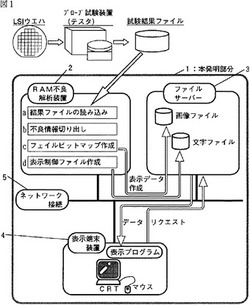

メモリ不良解析システム

【課題】簡単な操作によりより不特定多数者に対してフェイルビットマップ等の不良情報の開示を可能とする。

【解決手段】上記ネットワークを介してファイルサーバに接続される複数の表示端末装置のそれぞれは、半導体ウェハ上に形成されたメモリチップの少なくとも開発及び設計を含む複数の関係者に利用可能に配置され、表示を行うディスプレイ装置と、表示動作の制御を行うための入出力装置と、webブラウザが動作するためのCPU及びメモリを備えたパーソナルコンピュータにより構成される。上記ネットワークとwebブラウザにより上記ファイルサーバにアクセスし、上記ファイルサーバに格納されている複数のフェイルビットマップの中から目的のものを上記表示制御ファイルを用いて選択して上記メモリに取り込んで、上記メモリチップの不良解析結果を上記ディスプレイ装置に表示させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 デバイス出荷後に進行性不良が発生した場合に、不良ブロックと冗長ブロックとを対応付けることで不良ブロックを救済し、スクリーニングにかかる時間を増大させることなく、デバイスの寿命を延ばすことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 不良ブロックと冗長ブロック15bとを対応付ける対応付け手段11と、メモリブロック15aが冗長ブロック15bと対応付けられている場合に、対応する冗長ブロック15bを選択するブロック切替回路14とを備え、メモリブロック15aへのアクセス動作におけるエラーを検出するエラー検出回路13aと、エラーが検出されたときに、エラーが検出されたメモリブロック15aを不良ブロックと特定し、不良ブロックと対応付けられていない冗長ブロック15bがある場合に、前記不良ブロックを冗長ブロック15bと対応付ける不良ブロック特定回路13bとを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】市場において不良セルが発生しても、装置自身がその不良を冗長セルに自動的に置き換えることができる不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルアレイは、複数のメモリセルを有する本体セルアレイ11と、メモリセルと置き換え可能な複数の冗長セルを有するリダンダンシアレイ12とを有する。消去回路22は、メモリセル及び冗長セルのいずれかを含む対象セルに対して消去動作を行い、対象セルに対する消去動作の開始からの経過時間がタイマ14により計測される。制御回路13は、タイマ14による経過時間の計測により、消去動作の開始から所定時間が経過したことを認知したとき、消去動作を停止させ、対象セルを冗長セルへ置き換える。

(もっと読む)

半導体記憶装置及びその読み書き制御方法

【課題】信頼性を向上させることができる半導体記憶装置及びその読み書き制御方法を提供する。

【解決手段】データを記憶する記憶素子と、不良記憶素子を救済するためのリダンダンシー用記憶素子が所定方向に沿って複数配置された記憶部20と、記憶部20のデータ領域20Bから読み出された読み出しデータS30と所定の参照データS10とを比較することにより、不良記憶素子を特定し、不良記憶素子の位置を表すリダンダンシー情報S80を出力する比較部100と、データの書き込み及び読み出し時、不良記憶素子が存在する不良記憶素子列及び不良記憶素子列よりリダンダンシー領域20C側に位置する記憶素子列に対して、リダンダンシー領域20C側に隣接する記憶素子列又はリダンダンシー領域20Cに移動させるリダンダンシー部50とを備える。

(もっと読む)

1 - 4 / 4

[ Back to top ]