国際特許分類[H01G2/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | コンデンサ;電解型のコンデンサ,整流器,検波器,開閉装置,感光装置また感温装置 (21,977) | グループ4/00から9/00までの二つ以上に適用される細部 (573)

国際特許分類[H01G2/00]の下位に属する分類

取り付け (342)

冷却装置;加熱装置;通気装置 (95)

容器;外装 (42)

腐食に対する保護 (1)

電気的または熱的過負荷に対する保護 (24)

電極の端部から放電を防ぐための装置 (1)

静電遮蔽または磁気遮蔽 (3)

表示マーク,例.カラーコード (27)

国際特許分類[H01G2/00]に分類される特許

1 - 10 / 38

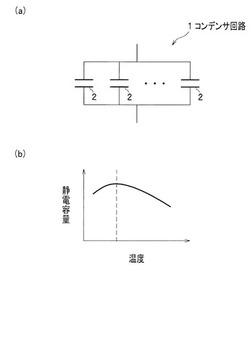

コンデンサ回路および電力変換装置

【課題】並列接続されたコンデンサの電流バランスを調節することを課題とする。

【解決手段】温度が上昇するにつれて、静電容量が小さくなる、規格容量の同じコンデンサ2が、複数並列に接続されていることを特徴とするコンデンサ回路1を提供する。また、このコンデンサ回路を、直流電源から供給される電流量の変動を平滑化するための直流コンデンサ回路や、特定の周波数に対し帯域制限をかけるためのフィルタコンデンサ回路や、電流の遮断時に生じる過渡的な高電圧を吸収するためのスナバコンデンサ回路に用いている電力変換装置を提供する。

(もっと読む)

可変容量装置

【課題】 3つ以上のキャパシタンス値が得られると共に、装置の小型化と信号損失の低減が可能な可変容量装置を提供する。

【解決手段】 可変容量素子2の駆動容量C1は、駆動電圧制御回路31から出力される駆動電圧Vdに応じて変化する。駆動電圧制御回路31は、駆動容量C1の検出値と目標値とを比較する比較器32と、比較器32の比較結果に応じた駆動電圧Vdを発生させる駆動電圧発生回路34とを備える。駆動電圧発生回路34の電流出力型レベル変換回路35は、比較器32の比較結果に応じて平滑化容量45にソース電流i10またはシンク電流i20を流し、駆動電圧Vdを昇圧または降圧する。また、電流出力型レベル変換回路35は、過渡状態から定常状態に移行するときに、ソース電流i10またはシンク電流i20の電流値を徐々に小さくする。

(もっと読む)

コンデンサ装置

【課題】コンデンサの大容量化に伴って導体上に設置するコンデンサ数が増えると導体上でのコンデンサ取付け面積が増大してコンデンサ装置が大型化することを解消するとともに、インダクタンス及び抵抗、ひいては各コンデンサへの流入電流や発熱のアンバランスを解消できるコンデンサ装置を提供する。

【解決手段】コンデンサ端子が接続されるP側導体とN側導体の積み重ねを第1のP側導体,第2のN側導体,第2のP側導体,第1のN側導体の順の四層とする。第1のP側導体と第1のN側導体にそれぞれ前記コンデンサを載置すると共に、第1のP側導体及び第1のN側導体の同一方向に外部端子を設け、この外部端子とは異なる側の第1,2のP側導体間、及び第1,2のN側導体間を連結部材にて連結して構成した。さらにP側及びN側導体の任意部にインピーダンス調整用孔を設ける。

(もっと読む)

コンデンサ装置

【課題】電流源に対して並列に接続される複数のコンデンサ素子を備えるコンデンサ装置において、複数のコンデンサ素子に流れる電流のバラツキを抑制する。

【解決手段】コンデンサ装置100は、交流電流源200に並列接続される8個のコンデンサ素子11〜18を備える。接続端子22から見て(j+1)番目(jは、1〜6)のコンデンサ素子と(j+2)番目のコンデンサ素子との間のバスバー20のインピーダンスを、接続端子22から見て1番目のコンデンサ素子11と2番目のコンデンサ素子12との間のバスバー20のインピーダンスZL11の(j+1)倍とし、接続端子32から見て(j+1)番目のコンデンサ素子と(j+2)番目のコンデンサ素子との間のバスバー30のインピーダンスは、接続端子32から見て1番目のコンデンサ素子18と2番目のコンデンサ素子17との間のバスバー30のインピーダンスZL72の(j+1)倍とする。

(もっと読む)

回路装置における鳴動抑制方法、および鳴動抑制機能を備えた回路装置

【課題】周期的に充放電されるセラミックコンデンサーを含む回路装置において、セラミックコンデンサーの充放電に伴う圧電現象に起因する鳴動を、セラミックコンデンサーの実装構造を変更することなく、効果的に抑制する。

【解決手段】可聴周波数範囲に対応する1周期24に充電期間24cと放電期間24dとが設けられて、周期的に充放電されるセラミックコンデンサー16を含む回路装置11において、前記セラミックコンデンサーの充放電に伴う圧電現象によって発生する鳴動を抑制するための方法であって、前記充電期間終了時点Teにおける前記セラミックコンデンサーの端子間電圧が前記放電期間で所定電圧値v2まで降下した場合、次の充電期間まで当該所定電圧値を維持するように前記セラミックコンデンサーを充電する回路装置における鳴動抑制方法としている。

(もっと読む)

プレヒーリング装置及びフィルムコンデンサの製造方法

【課題】比較的簡単な構成で、両面に金属膜が形成されたフィルムコンデンサに存在する絶縁欠陥部周辺の蒸着金属を除去する。

【解決手段】導通検出ユニット(35)により、電圧が印加される第1の分割電極(21a)と、残りの第1の分割電極(21a)とが電気的に絶縁されているかを検出し、この検出結果に基づいて、電圧印加ユニット(32)により第1の分割電極(21a)同士が絶縁状態であるときにのみ、第1の分割電極(21a)に対して電圧を印加する。

(もっと読む)

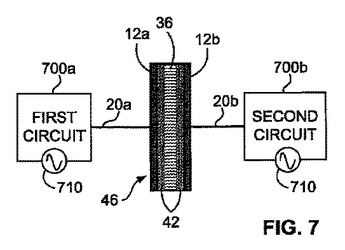

信号結合及び直流阻止のための方法及びシステム

他の電子部品と組み合わされた複数の対称2重層キャパシタを用いることで、電子機器の1の段から他の段に、外部世界からそのような段に、又は、そのような段から外部世界に、低周波信号を結合させるための回路構成の方法及びクラス。キャパシタはエネルギーの貯蔵ではなく、直流電流を阻止しつつ信号の伝送に用いられる。より在来的なキャパシタの代わりに2重層キャパシタを用いることで、非常に少ない歪みをもって非常に広い範囲の信号の伝送が可能になる。この技術は、在来的な部品が使用されたときに起こり得る許容できないレベルの歪みが生じうるところ、単一の部品の故障の場合の安全のために冗長デバイスが必要とされる生体電子刺激を含む医療装置での使用に特に適合する。  (もっと読む)

(もっと読む)

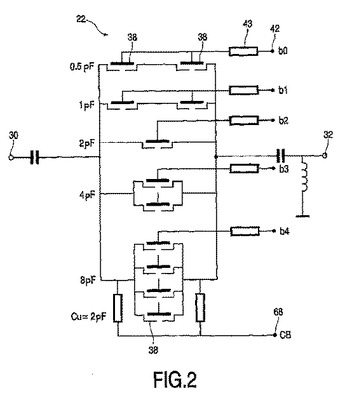

切替可能なキャパシタアレイ

切替可能なキャパシタアレイ(22)は、制御可能な静電容量を得るために、入力(30)と出力(32)との間に並列に配置された複数のセルを有する。切替式キャパシタは、容量型MEMSスイッチ(38)により実現される。低静電容量値セルは、直列接続された1より多いMEMSスイッチを含み、それによって、各々の低静電容量値MEMSスイッチにかかる電圧を低減する。  (もっと読む)

(もっと読む)

積層コンデンサ

【課題】設計の自由度が高く、経済的で、構造欠陥が発生しにくい、低ESL化が図られた積層コンデンサを提供する。

【解決手段】第1および第2の内部電極42および43の各々の引出し部52および53、ならびに第3および第4の内部電極44および45の各々の引出し部54および55を、側面36,37の長さ方向に関して交互に露出するように配置する。第1および第3の内部電極ならびに第2および第4の内部電極43および45の各々を、好ましくは、同一面内において、側面36,37の長さ方向に並びかつ互いの間に所定の間隔を隔てて配置する。誘電体層32の積層方向で見たとき、第1および第4の内部電極42および45の各々の容量形成部48および51が重なり合わず、第2および第3の内部電極43および44の各々の容量形成部49および50が重なり合わない。

(もっと読む)

積層コンデンサ、および積層コンデンサの製造方法

【課題】ESLを大幅に低減することができる積層コンデンサと、その製造方法を提供する。

【解決手段】積層コンデンサ10は、複数の誘電体層12a,12bが積層されて形成される誘電体素体12と,複数の第1内層用導体層および第2内層用導体層が誘電体層を介して交互に積層されている内層部17と、内層部17の両端面に隣接し、複数の第1外層用導体層および第2外層用導体層が誘電体層12bを介して積層されている外層部19a,19bと、側面に形成される複数の第1端子電極および第2端子電極と、を有する。第1端子電極が第1内層用導体層と第1外層用導体層とに接続され、第2端子電極が第2内層用導体層と第2外層用導体層とに接続される。外層部19a,19bの誘電体層12bが一対の第1外層用導体層あるいは一対の第2外層用導体層において、各々の外層用導体層同士を互いに接続させる複数のピンホール導体部20を有する。

(もっと読む)

1 - 10 / 38

[ Back to top ]