アナログ デバイシス, インコーポレイテッドにより出願された特許

1 - 10 / 40

クロスした4個の縦方向に連結された慣性センサ

【課題】慣性センサを提供する。

【解決手段】慣性センサは、クロスした4個の構成の4つの相互接続されたセンサ素子50A、50B、50C、50Dを含んでいる。各センサ素子は、フレーム、52A,52B、52C、52Dおよびフレーム内にサスペンドされている共振器54A、54B、54C、54Dを含んでいる。隣接するセンサ素子のフレームが、互いに逆位相で動くことを可能にするが、互いに同位相で動くことを実質的に防止するように、センサ素子は配置されている。センサ素子は、横方向に連結された配置、縦方向に連結された配置、または完全に連結された配置で構成されている。一組の対のセンサ素子は、縦方向に連結され得る。

(もっと読む)

サポート部材を用いてマイクロフォンを形成するためのプロセス

【課題】サポート部材を用いてマイクロフォンを形成するためのプロセスを提供すること。

【解決手段】マイクロフォンを形成するための方法は、バックプレート、およびウェットエッチングの犠牲層の少なくとも一部分の上の可撓性の振動板を形成する。この方法は、ウェットエッチングのレジスト材料を追加し、ウェットエッチングのレジスト材料は、振動板を支持するように、振動板とバックプレートとの間に配置される。ウェットエッチングのレジスト材料の一部は、振動板とバックプレートとの間には配置されない。方法はその後、上述の追加の間に追加されたウェットエッチングのレジスト材料の一部を除去する前に、犠牲材料を除去する。その後、ウェットエッチングのレジスト材料は、犠牲材料の少なくとも一部が除去された後に、実質的にその全体が除去される。

(もっと読む)

金属酸化物半導体出力回路およびそれを形成する方法

【課題】金属酸化物半導体(MOS)出力回路とその形成方法の提供。

【解決手段】第一パッド61と、ゲート、第一の供給電圧に電気的接続のソース、ドレインを含む基板で第一型の第一MOSトランジスタ62と、ゲート、制御信号を受信する構成のソース、第一MOSトランジスタのゲートに電気的接続のドレイン、本体を含む基板で第一型と反対の第二型の第二MOSトランジスタ65と、バイアス信号を受信する構成のゲート、第二供給電圧に電気的接続のドレイン、第二MOSトランジスタのソースに電気的接続のソース、第一参照電圧に電気的接続の本体を含む基板で第一型の第三MOSトランジスタ66とを含み、第二MOSトランジスタの本体は第三MOSトランジスタのソースに電気的接続、一時的な信号イベントの第一パッド上の受信の場合、第二MOSトランジスタのドレインから第二供給電圧まで第二MOSトランジスタの本体を流れる電流を妨げる集積回路。

(もっと読む)

アナログ映像信号のサンプリング位相の自動化決定のための装置および方法

【課題】アナログ映像信号のサンプリング位相の自動化決定のための装置および方法

の提供。

【解決手段】方法および装置は、アナログ信号からデータの抽出を提供する。方法は、アナログ信号の振幅遷移の位相を識別する振幅遷移を有するデータ配置信号を引き出すことと、データ配置信号に応答して、アナログ信号の振幅遷移の位相と異なる位相を有するサンプリングクロック信号を選択することとを含む。装置は、アナログ信号からデータ配置信号を引き出す信号生成器と、アナログ信号の振幅遷移の位相と異なる位相を有するサンプリングクロック信号を選択する選択器を含む。

(もっと読む)

マイクロ機械加工されたマイクロフォンおよびマルチセンサ、ならびにそれらを生産する方法

【課題】好適なマイクロフォンを提供すること。

【解決手段】マイクロフォンを形成する方法であって、該方法は、少なくとも1つのトレンチを基板にエッチングすることと、少なくとも1つのトレンチを少なくとも1つの犠牲材料で少なくとも部分的に充填することとによって、バックプレートを形成することと、液体エッチ除去可能層の少なくとも一部の上に可撓性のダイヤフラムを形成することと、フォトレジストの層を追加することであって、該フォトレジストの一部分は、該ダイヤフラムを支持するために、該ダイヤフラムと該バックプレートとの間にペダスタルを形成する、ことと、該フォトレジストを除去する前に、該少なくとも1つのトレンチを介して、該基板の裏側から、該液体エッチ除去可能材料を除去することと、該液体エッチ除去可能材料の少なくとも一部を除去した後、該ペダスタルを除去することとを包含する、方法。

(もっと読む)

二次導関数エッジ検出方法のためのエッジオリエンテーション

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

画素速度での画像処理のための方法および装置

本発明の実施形態は、処理演算が、画素の新しいラインまたはフレームに移行するときでも、メモリフェッチおよび画素出力の一定速度を維持するために、2−D画像処理において、改良されたタイミング制御を提供する。本発明に従って改良されたタイミング制御は、現在のライン上のエッジ画素ブロックの新しい列が、複製される、またはゼロに設定される間に、次のラインまたはフレームの第1の画素ブロック内の画素データの新しい列をプリフェッチすることによって、アイドルメモリ帯域幅を利用するため、着信画素速度と発信画素速度との間の1対1関係は、付加的なクロックサイクルまたはメモリ帯域幅を伴うことなく維持される。現在のライン上のエッジ画素ブロックが、処理されることに伴って、次のラインまたはフレームの第1の画素ブロック内のデータは、余剰クロックサイクルまたは余剰メモリ帯域幅を伴わずに、計算のための準備ができる。  (もっと読む)

(もっと読む)

接合型電界効果トランジスタおよびその製造方法

本願は、ドレイン(140)と、ゲート(160)と、ソース(130)と、を有し、ドレイン(140)およびソース(130)が、第1の型の半導体領域によって形成される、電界効果トランジスタに関する。一局面では、電界効果トランジスタはまた、ゲート(160)とドレイン(140)の中間のさらなるN+領域(410)等のさらにドープされた領域を含む。さらにドープされた領域は、電界効果トランジスタの中間ドレインとして見なすことができる。いくつかの実装では、さらにドープされた領域は、高濃度にドープすることができる。さらにドープされた領域によって、ドレイン(140)周囲の電界勾配を減少させることができる。  (もっと読む)

(もっと読む)

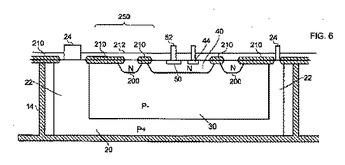

バイポーラトランジスタ

エミッタ領域(50)と、ベース領域(40)と、コレクタ領域(20)と、ベース領域(40)から離間し、それを囲む、保護領域(200)とを備える、バイポーラトランジスタ。保護領域(200)は、ベース領域(40)を形成するために使用される同一ドーピングマスクを使用して形成することができ、動作中には、空乏層を展開する役割を果たすことができる。また、本発明は、上記バイポーラトランジスタを製造する方法であって、エミッタ領域と、ベース領域と、コレクタ領域とを形成することと、該ベース領域を囲む保護領域を形成することとを含む、方法も提供する。  (もっと読む)

(もっと読む)

1 - 10 / 40

[ Back to top ]