Fターム[5F082EA11]の内容

Fターム[5F082EA11]の下位に属するFターム

エッチング (140)

リフトオフ

Fターム[5F082EA11]に分類される特許

1 - 3 / 3

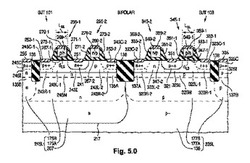

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】金属膜を必要以上に薄く形成しなくても、LOCOSエッジ付近での金属膜とベース絶縁膜との過度な合金化を防止できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】エミッタ領域の基板1上からLOCOS層15B上にかけてシリコンゲルマニウム層51を連続して形成する。次に、エミッタ59領域のシリコンゲルマニウム層51上にエミッタ59を形成する。そして、エミッタ59が形成された基板1上にシリコン酸化膜を形成し、次に当該シリコン酸化膜をエッチバックすることによって、エミッタ59の側面にサイドウォール61Aを形成する。その後、基板1上にTiを形成し熱処理を施して、チタンシリサイド膜67を形成する。サイドウォール61Aを形成する工程では、LOCOSエッジ90上にサイドウォール61Bを付随的に形成する。

(もっと読む)

バイポーラトランジスタ

【課題】容量を自由に調整することができ、さらなる高周波領域での要求に耐えうるバイポーラトランジスタを提供する。

【解決手段】本発明のバイポーラトランジスタは、半導体基板と、前記半導体基板内に形成されたトランジスタ動作領域と、前記半導体基板表面を覆うように形成された絶縁膜と、前記トランジスタ動作領域から前記絶縁膜を貫通し、コレクタ、ベース、エミッタのうちの少なくとも2つにそれぞれ接続され、前記絶縁膜上まで引き出された第1および第2の引出配線と、前記第1および第2の引出配線にそれぞれ接続されるボンディング用の第1および第2のパッドと、前記第1および第2のパッドにそれぞれ接続された第1および第2の容量調整用配線とを備え、第1および第2の容量調整用配線が互いに異なる層で構成される。

(もっと読む)

1 - 3 / 3

[ Back to top ]