Fターム[5K018JA00]の内容

双方向デジタル伝送 (547) | その他 (4)

Fターム[5K018JA00]の下位に属するFターム

Fターム[5K018JA00]に分類される特許

1 - 2 / 2

デュプレックスモード整合方法およびLAN通信装置

【課題】 PHYとMACのデュプレックスモードの整合をとるための簡易な手法を提供する。

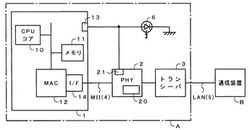

【解決手段】 PHY2にはリンク状態および非リンク状態を識別できるようにLED端子21が設けられる。LED端子21はLED6に接続され、LED端子21に現れる出力の変化に応じてLED6は点灯・消灯する。さらにLED端子21はMAC12を収容するCPU1の割り込み端子13に接続される。CPUコア10は、非リンク状態からリンク状態に切り替わったときに生じる割り込み信号に応答してPHY2のレジスタ20の内容、つまりリンクパートナーBとの自動ネゴシエーションで決定したデュプレックスモードを読み込む。CPUコア10によって読み込まれたデュプレックスモードは、MAC12のデュプレックスモードとしてメモリ11に記憶される。

(もっと読む)

通信リンク間の遅延トレードオフ

本発明では、全二重通信に利用可能な遅延量が、各リンク間で、それらのアクティブ状態、現在および最近の履歴に応じて分配される。全二重通信システム内のリンクがアクティブであるか非アクティブであるか追跡すること、すなわち、転送されるデータの情報値を知ることにより、逆方向のリンクが同時に非アクティブである場合には、通常許容されるものより大きい符号化遅延を持つ符号化手順をアクティブリンクに使用することができる。ユーザの遅延に対する敏感さはリンクがアクティブになる時に最大になるので、リンクがアクティブになる瞬間には通常使用されるものより小さい符号化遅延を持つ符号化手順が割り当てられる。符号化遅延はその後増大される。好ましくは、往復遅延は要求される最大値よりも小さく保たれるように制御される。  (もっと読む)

(もっと読む)

1 - 2 / 2

[ Back to top ]