Fターム[5F082EA31]の内容

Fターム[5F082EA31]の下位に属するFターム

Fターム[5F082EA31]に分類される特許

1 - 2 / 2

半導体装置

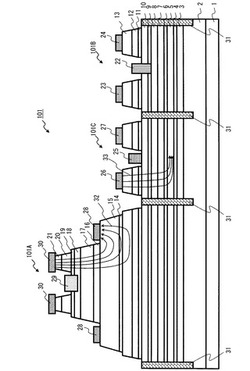

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高周波帯域で動作する半導体装置の特性向上と製造コストの低減とを両立した半導体装置およびその製造方法を提供する。

【解決手段】同一の半絶縁性GaAs基板1上に積層された複数の半導体層を用いて複数の半導体素子が形成された半導体装置100であって、FET領域23を用いて形成されたFETと、FET領域23と隣接するHBT領域22を用いて形成されたHBTと、FET領域23とHBT領域22との間である素子分離領域24に設けられ、FET領域23とHBT領域22とを分離する分離溝25とを備え、分離溝25は、内壁面と該内壁面の端部とに接地電位を有する導電性金属層が形成されることにより、素子分離領域24を通過する素子間リーク電流を抑制する。

(もっと読む)

1 - 2 / 2

[ Back to top ]