Fターム[2G029AF08]の内容

周波数測定、スペクトル分析 (483) | 計数結果の処理 (41) | 計数値の補正回路を有するもの (4)

Fターム[2G029AF08]に分類される特許

1 - 4 / 4

周波数計測装置及び周波数位相差比較装置

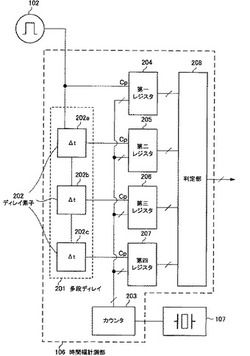

【課題】デジタル回路に供給するベースクロックの周波数を高くせずとも、必要な周期計測のための分解能を得ることができる、高分解能の周波数計測装置及び周波数位相差比較装置を提供する。

【解決手段】ベースクロックの周期を等間隔に細分化するディレイ手段202を複数備える多段ディレイ201を用いて、入力される矩形波信号を遅延させ、夫々のディレイ素子202から得られるタイミングでカウンタ203の値をレジスタで取得し、各々のレジスタの値を比較することで、矩形波信号のアップエッジがベースクロックのどのタイミングに位置しているのかが判定できる。そして、その判定結果に応じた時間軸上のずれの値を、周期カウンタ105によって得られる周期の値に与えることで、周期計測の分解能を向上させることができる。

(もっと読む)

測定装置および測定方法

【課題】交流信号の周期が変動する要因が発生した場合においてもその交流信号の周波数を正確に測定する。

【解決手段】交流信号S1のゼロクロスによって区分される交流信号S1の1波長分の周期を、予め決められた規定時間内に含まれている各区分についてそれぞれ特定すると共に特定した周期に基づいて交流信号S1の周波数を測定する周波数測定処理を実行する測定処理部12を備え、測定処理部12は、ゼロクロスの間隔が変動する要因として予め決められた変動要因の発生を検出したときに、変動要因の発生を検出した時点における1波長分の周期を除外して周波数測定処理を実行する。

(もっと読む)

周波数測定回路

【課題】オンとなる時間が不定のパルス波が入力信号である場合でも、所望の精度で入力信号の周波数を測定することができるようにする。

【解決手段】観測信号がロジックLowになったとき、ラッチ信号LaがロジックHighであれば、ラッチ内蔵アナログ補間器7により保持されている検出電圧V2aを選択し、逆に、ラッチ信号LbがロジックHighであれば、ラッチ内蔵アナログ補間器8により保持されている検出電圧V2bを選択し、その選択した検出電圧V2(V2a、または、V2b)と、アナログ補間器6から出力された検出電圧V1と、カウント値m及びカウント値nとを用いて、入力信号の周波数finを算出する。

(もっと読む)

周期計測回路

【課題】 基準周波数を作るクロック装置の発振周波数が中心値からずれた場合でも精度の良い周期計測を行う。

【解決手段】 信号変換回路6は計測対象の入力信号の周期に応じたパルス幅のパルス信号に変換し、このパルス幅を第1のタイマ50aはクロック装置7で発生した基準周波数に基づいて生成したタイマ周期を用いてカウントし、マイコン50はこのカウント値を用いて入力信号の周期を算出する。一方、基準信号変換回路11は商用電源1の周期に応じたパルス幅のパルス信号に変換し、このパルス幅を第2のタイマ50bはタイマ周期を用いてカウントし、マイコン50はこのカウント値から商用電源周波数が50Hzか60Hzか判定し、判定周波数に基づいて上記算出した入力信号の周期を補正する。それ故、より正しい周期が計測できる。

(もっと読む)

1 - 4 / 4

[ Back to top ]