国際特許分類[H03K17/10]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 最大許容被開閉電圧を増大させるための変形 (45)

国際特許分類[H03K17/10]に分類される特許

1 - 10 / 45

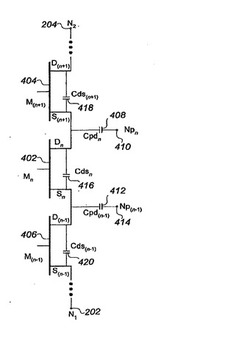

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

半導体スイッチ回路

【課題】低周波帯域において線形性劣化のない半導体スイッチ回路を提供する。

【解決手段】入出力端子間に直列にソースおよびドレインを接続した1又は2以上の電界効果トランジスタと、電界効果トランジスタのゲートに接続した抵抗を備えた半導体スイッチ回路において、電界効果トランジスタのゲート−ドレイン間およびゲート−ソース間に、キャパシタをそれぞれ接続可能とした。

【効果】FETのゲート−ドレイン間およびゲート−ソース間すべてにキャパシタを接続したことにより、従来より低い周波数帯域においてゲート電極に接続する抵抗よりFETのインピーダンスが十分低くなるため、線形性を向上させることが可能となる。

(もっと読む)

パワースイッチング素子直列電圧制限回路

【課題】 パワースイッチング素子直列電圧制限回路を提供する。

【解決手段】 パワースイッチング素子直列電圧制限回路は、複数のパワースイッチング素子(Q1〜Qn)などからなるパワースイッチング素子直列分岐回路を含み、当該パワースイッチング素子は制御端と、高端(SD)と低端(WD)とを含み、パワースイッチング素子は分岐回路に直列にされるが、当該複数のパワースイッチング素子(Q1〜Qn)直列方式は1つのパワースイッチング素子における高端(SD)と別の1つのパワースイッチング素子における低端(WD)とを順に従って直列する。また、複数のエネルギー一時記憶回路(K1〜Kn)を含み、各パワースイッチング素子の両端が1つのエネルギー一時記憶回路を対応並列するが、各パワースイッチング素子の開/閉が非同期短時間過電流の負荷エネルギーを記憶するためである。また、前記パワースイッチング素子直列分岐回路に電圧制限を行う集中電圧制限回路Hを含む。

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

半導体回路

【課題】 高電位側スイッチング素子の導通を示す第1状態から前記高電位側スイッチングデバイスの非導通を示す第2状態への遷移、または前記第2状態から前記第1状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合であっても誤信号が発生することのない半導体回路を提供する。

【解決手段】 高電位側スイッチング素子駆動回路1は、レベルシフト回路2の第1の負荷抵抗28、28に発生するオン側、オフ側の第1のレベルシフト済み信号S4、S5のうち少なくとものいずれか一方に信号が発生したときに、第2の負荷抵抗30、29に同時に発生する第2のレベルシフト済み信号S6、S7によって制御され、他方の出力が発生しないようにレベルシフトの出力を抑制する短絡手段31、32を有する。

(もっと読む)

1 - 10 / 45

[ Back to top ]