Fターム[5F033XX02]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 段差被覆性改善、段切れ防止 (570)

Fターム[5F033XX02]に分類される特許

1 - 20 / 570

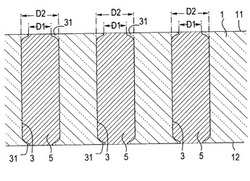

縦導体充填構造

【課題】ウエハ等の基板に設けられた縦孔内に、脱落、抜け等を生じることなく、完全充填された縦導体充填構造を提供すること。

【解決手段】基板1の厚み方向に設けられた縦孔3内に縦導体5を充填した縦導体充填構造であって、孔開口端が内側に突出する凸縁31となっており、凸縁31−31間で見た孔径D1が、孔内壁面3−3間で見た内径D2よりも小さい。

(もっと読む)

微細空間内に機能部分を形成する方法

【課題】低温分散系機能性材料を用いて、微細空間内に空隙、隙間、または空洞のない機能部分を形成する方法を提供する。

【解決手段】熱溶解性を有する機能性微粉末52を、液状分散媒51中に分散させた分散系機能性材料5を、微細空間3内に充填する。次に、微細空間3内の液状分散媒51を蒸発させる。次に、熱処理により機能性微粉末52を熱溶解させた後、加圧しながら冷却する。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極におけるボイドの発生を防止することができ、従来に比べて信頼性の高い半導体装置およびその製造方法、ならびに電子部品を提供すること。

【解決手段】Si基板29上のゲート絶縁膜30上に電極層51を形成する。ゲート絶縁膜30上に層間絶縁膜31を形成した後、ダマシン法により電極層51と同一パターンの下側配線42と、反対パターンの下側絶縁膜43を含む下側パッド40を形成する。次に、貫通孔59を形成し、同時に、貫通孔59内に下側絶縁膜43と同一パターンの突出部60が形成された第1層間絶縁膜32を露出させる。そして、突出部60の一部がエッチング残渣として残るように第1層間絶縁膜32をエッチングした後、ビア絶縁膜38を形成し、貫通孔59の底面のビア絶縁膜38をエッチングする。次に、貫通孔59のビア絶縁膜38の内側に電極材料をめっき成長させることにより、貫通電極17を形成する。

(もっと読む)

半導体装置の製造方法

【課題】高い歩留まりを実現できる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、基板11上の絶縁層13に形成された第1の凹部14および第1の凹部14よりも幅が狭い第2の凹部15に、基板11を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜21を形成する工程を備えている。また、前記半導体装置の製造方法は、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を、第1の銅膜21の形成時よりも流動性が小さい状態で形成する工程を備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

パターン構造体の製造方法

【課題】基材上にパターンを低温かつ低コストで形成することができると共に、リフトオフを容易にできるパターン構造体の製造方法を提供する。

【解決手段】実施形態に係るパターン構造体の製造方法では、基材10上に、インクジェット法によりリフトオフ材12を形成する。次に、基材10及びリフトオフ材12上に、原子層堆積法により機能膜14を形成する。次に、リフトオフ法によりリフトオフ材12を除去することによって、基材10上に、機能膜14からパターン14aを形成する。リフトオフ材12は、樹脂と溶媒とを含むインクを基材10上に塗布した後、溶媒を除去することによって形成される。溶媒は、樹脂に対する第1溶解性を有する第1溶媒と、第1溶解性よりも低い第2溶解性を有する第2溶媒とを含む。第1溶媒は第2溶媒に相溶する。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

流動性充填材の充填方法、充填装置及びウエハ

【課題】ウエハに設けられた微細孔内に流動性充填材を、より確実に充填し得、しかも、ウエハ上から充填材残渣を取り払い得る充填方法、そのための充填装置及びウエハを提供すること。

【解決手段】ウエハ7に存在する微細孔73内に流し込まれた流動性充填材9を、加圧手段1,3により加圧する工程において、ウエハ7の受圧面71に対する流動性充填材9の表面張力と、加圧手段1,3の加圧面311に対する流動性充填材9の表面張力とを互いに異ならせる。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

液晶表示装置の製造方法及びレジスト剥離装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】エッチングによってAl合金層11、キャップ層12で形成される走査線10をパターニングした後、レジスト200をMEA(モノエタノールアミン)によって剥離する。MEAを剥離したあと、第1水洗槽において、基板に付着しているMEAを水によって洗浄する。この時、洗浄液である水に所定の量以上のMEAが含まれていると、Al合金が溶解し、キャップ層12であるMoCrの庇が発生する。これを防止するために、第1水洗槽における洗浄液のMEAの濃度を10PPM以下、好ましくは5PPM以下に管理する。これによって、Al合金の溶解を防止し、キャップ層12の庇が発生することを防止する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】中間層の形成時に、第2コイル46および第3コイル61によってターゲット53と基体11との間に磁力線M1が通るように磁場を発生させることによって、溝部12の内壁面に均一な厚みで中間層を成膜することが可能になる。

(もっと読む)

表示装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】映像信号線が絶縁膜を介して走査線を乗り越える構成となっている。走査線10はAlCu合金を下層11とし、MoCr合金を上層12とする2層構造である。上層/下層の膜厚比を、0.4以上、1.0以下とすることによって、走査線10の断面において、電池作用によって上層12のエッチング速度が遅くなって、上層12の庇部が形成されることを防止する。これによって、走査線10に生じた庇部に起因して、映像信号線が走査線10との交差部において断線することを防止する。

(もっと読む)

金属充填装置

【課題】充填不良や被処理物の割れを生じず、被処理物上に開口するように形成された微小空間に溶融金属を的確に充填する。

【解決手段】金属充填装置1であって、半導体ウェハKを保持する保持台Hと、ハウジングCと、ハウジングCの内部空間内に気密状に嵌入されたピストンPとを備え、半導体ウェハK又は保持台H、ハウジングC及びピストンPによって気密状の処理室2が形成され、更に、処理室2内を減圧する減圧機構3と、前記処理室2内に溶融金属Mを供給する溶融金属供給機構4とを備えるとともに、ピストンPは、少なくとも、その半導体ウェハKに対向する側が金属から構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置、及びその製造方法

【課題】絶縁破壊が発生しにくい半導体装置及びその製造方法を提供する。

【解決手段】集積回路13と電気的に接続する電極14が位置する半導体基板10を用意する。半導体基板の前記第1の面11とは反対側の第2の面12において等方性エッチングを行い、第1内壁面を有する第1凹部を形成する。第1凹部内から前記半導体基板を貫通して電極に至り、第2内壁面22aを有する第2凹部を形成する。第2の面と第1内壁面によって形成された第1の角部、及び第1内壁面と第2内壁面によって形成された第2の角部を除去するエッチバック処理を行い、第2の面と第2内壁面とを連続する第1内壁面を形成する。角部を除去した後、少なくとも第1内壁面、及び第2内壁面を覆うように、電極とオーバーラップする位置に開口部65を有する絶縁層30を形成する。絶縁層を介して第2凹部内に充填され、電極と接続し、かつ第2の面から突出する導電部40を形成する。

(もっと読む)

配線膜およびそれを用いたアクティブマトリクス基板、並びに配線膜の製造方法

【課題】テーパー形状のAl配線膜を容易かつ安定的に得る。

【解決手段】Al配線膜101は、AlもしくはAl合金から成る第1のAl合金層101aと、その上に配設され、Ni、PdおよびPtのいずれか1以上の元素を含み第1のAl合金層101aとは異なる組成のAl合金から成る第2のAl合金層101bとから成る二層構造を有する。フォトレジスト102の現像処理に用いるアルカリ性薬液により、第2のAl合金層101bはエッチングされ、その端部はフォトレジスト102の端部よりも後退する。その後、フォトレジスト102をマスクとするウェットエッチングを行うことにより、Al配線膜101の断面はテーパー形状となる。

(もっと読む)

半導体装置の製造方法

【課題】所定値以上の厚みを有するパッドを少ない工程数で形成することができる半導体装置の製造方法を提供すること。

【解決手段】本発明は、アルミ層22を、半導体基板上に形成された層間絶縁膜1の上方に堆積させる。アルミ層22上には、アルミ層24を堆積させる。パッド領域102のアルミ層24の上方に、フォトレジスト7を形成する。フォトレジスト7を用いてエッチングを行うことにより、パッド領域102にパッド上層52を形成するとともに、配線領域101のアルミ層24を除去する。そして、フォトレジスト8を、パッド領域102のパッド上層52を覆い、かつ、配線領域101で配線パターンを構成するように形成する。フォトレジスト8を用いてエッチングを行うことにより、パッド領域102にパッド下層51を形成するとともに、配線領域101に配線2を形成する。

(もっと読む)

1 - 20 / 570

[ Back to top ]