Fターム[5F082EA01]の内容

Fターム[5F082EA01]の下位に属するFターム

Fターム[5F082EA01]に分類される特許

1 - 3 / 3

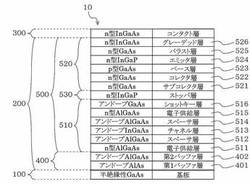

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

半導体装置

【課題】統合型のインテリジェントスイッチデバイス、統合型の入力信号・伝達ICまたは統合型のパワーICなどに用いられる横型MOSFETにおいて、複雑な分離構造を用いずに、より小さいチップ面積で高ESD耐量および高サージ耐量を具えた半導体装置を提供する。

【解決手段】P型半導体よりなるエミッタ領域25、ベース領域として機能するNウェル領域10およびP型エピタキシャル成長層13およびP型半導体基板12をコレクタとするベースオープンの縦型バイポーラトランジスタの表面電極26と、横型MOSFETのドレイン電極22とを金属電極配線27により電気的に接続し、高ESD電圧や高サージ電圧が印加されたときに、ベースオープンの縦型バイポーラトランジスタの動作によりESDおよびサージエネルギーを吸収するとともに、破壊に至る横型MOSFETの降伏耐圧以下の電圧に制限する。

(もっと読む)

1 - 3 / 3

[ Back to top ]