Fターム[5J055CX24]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 負荷・用途 (2,057) | 信号用、通信用 (591)

Fターム[5J055CX24]の下位に属するFターム

外部信号伝送用、同軸ライン駆動等 (24)

内部信号伝送用、バス駆動等 (43)

Fターム[5J055CX24]に分類される特許

521 - 524 / 524

半導体スイッチ回路

入力端子と出力端子との間に第1、第2、第3半導体スイッチを直列接続して挿入し、入力端子に接続された第1半導体スイッチ及び出力端子に接続された第3半導体スイッチのそれぞれに第1、第2電圧印加手段を並列接続し、それぞれの電圧印加手段を、利得が約+1の状態に設定され、入力側が入力端子及び出力端子に接続された直流増幅器と、電圧印加手段用半導体スイッチとの直列接続回路で構成し、この電圧印加手段用半導体スイッチの一端を第1と第2半導体スイッチの接続点Jまたは第2と第3半導体スイッチの接続点Kに接続し、スイッチ制御手段が第1〜第3半導体スイッチと電圧印加手段用半導体スイッチを逆モードでをオン及びオフ状態に制御し、第1〜第3半導体スイッチがオフ状態に制御されたときに、第1及び第2電圧印加手段が入力端子及び出力端子の電位を接続点J及びKに印加するように構成した半導体スイッチ回路。 (もっと読む)

無線周波数用双極単投スイッチ

【解決手段】本発明の双極単投(DPST)スイッチは、第1入力ポートに対応する第1回路部と、第2入力ポートに対応する第2回路部と、及び出力ポートを有するスイッチ回路とを具備する。ここで、第1及び第2の回路部の各々は、分離チャンネルの一部を提供する少なくとも1個の第1トランジスタと、送信チャンネルの一部を提供する少なくとも1個の第2トランジスタと、送信チャンネル又は分離チャンネルのいずれかを選択する制御バイアスを提供する少なくとも1個の第3トランジスタとを有する。 (もっと読む)

バッファにおける伝搬遅延及びプロセス及び温度の影響を低減する方法

低速出力エッジを有するバッファ回路が記載されている。パルスのより高値の電流が、ワンショットタイミング回路から駆動されて、出力MOSFETのターンオンか又はターンオフの開始を加速させるために、電流パルスが前記バッファの該出力MOSFETの制御ゲート内へと注入される。前記開始とターンオン及びターンオフとに至る時には、より低値の電流源が、前記出力MOSFETの前記ゲートを駆動するために継続する。一実施形態において、ワンショットは、入力信号の立ち上がりエッジと立ち下がりエッジとからトリガされる。前記より高値の電流パルスの効果は、バッファによる回路遅延を低減することである。更にまた、温度、供給電圧、及びプロセスの変動が起きる時に、実質的に一定となるようバッファ回路の遅延を維持するために、温度に応じるように、及び供給電圧に応じるように、パルス幅を設計することができる。

(もっと読む)

(もっと読む)

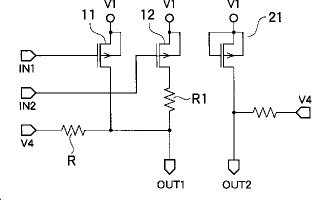

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

521 - 524 / 524

[ Back to top ]