エプコス アクチエンゲゼルシャフトにより出願された特許

21 - 30 / 318

圧電素子

【解決手段】本発明は、互いに上下に配設された複数の圧電層(2、2’、2’’、2’’’、3、3’、3’’、3’’’)とその間に配設された電極層(4,5)から成る積層体(1a)を有する圧電素子(1)に関する。前記積層体(1a)は第1圧電定数を備える少なくとも1つの第1圧電層(2)と、直接これに隣接して、第2圧電定数を備える少なくとも1つの第2圧電層(3)とを有する。圧電定数は、電極層(4,5)に印加された電圧による電界に垂直な方向の圧電層(2,3)の歪みを表す。第1圧電定数は第2圧電定数とは異なる。 (もっと読む)

積層型圧電素子の製造方法および積層型圧電素子

本発明は、圧電グリーンシートを含む圧電材料を準備するステップと、グリーンシートと、電極材料からなる層とを交互に配置し、PbOを含有する被覆層を備える電極材料からなる少なくとも一層を設け、および/または電極材料にPbOを混合する、積層型圧電素子を製作するための方法が提案される。さらに、内部電極(20)の表面に分極亀裂(25)を有する領域を備える積層型圧電素子が提供される。 (もっと読む)

温度依存的なコンデンサ、およびコンデンサモジュール

コンデンサにおいて、次の構成要素すなわち第1の加熱部材(1)と第1のコンデンサ領域(2)とを含んでおり、該コンデンサ領域は、誘電性層(3)と、それぞれの誘電性層(3)の間に配置された内部電極(4)とを含んでおり、第1の加熱部材と第1のコンデンサ領域(2)は熱伝導式に相互に結合されている。  (もっと読む)

(もっと読む)

バラクタ、およびバラクタを製造する方法

バラクタは、次の各構成要素を含んでおり、すなわち、抵抗に関して正の温度係数を有する第1のPTC領域(4)と、コンデンサ領域(3)とを含んでおり、該コンデンサ領域は、第1の電極(2)と、第2の電極(2’)と、第1の電極(2)と第2の電極(2’)との間に配置された第1の誘電性層(1)とを含んでおり、

第1のPTC層(4)とコンデンサ領域(3)は熱伝導式に相互に結合されており、コンデンサ領域(3)のキャパシタンスは、第1のPTC領域(4)、コンデンサ領域(3)、または第1のPTC領域(4)およびコンデンサ領域(3)へのバイアス電圧の印加によって変更可能である。  (もっと読む)

(もっと読む)

成形体、加熱装置、及び成形体の製造方法

【解決手段】正の温度係数の電気抵抗をもつ第1セラミック材料を含む第1領域(10)と、第2セラミック材料を含む第2領域(20)と、第3セラミック材料を含む第3領域(30)とを有する成形体が提供される。また、当該成形体を備える加熱装置が提供される。更に、成形体の製造方法が提供される。 (もっと読む)

圧電セラミック材料、その製造方法及び積層構造素子

【課題】

【解決手段】本発明は一般式P1-c-dDcZd(PbO)wの圧電セラミック材料に関する。ただし0<c≦0.025、0≦d≦0.05、0≦w≦0.05であり、Pは式[Pb1-vAgIv][(Zr1-yTiy)1-uCuIIu]O3を有する化合物を表し、0.50≦1-y≦0.60、0<u≦0.0495、0≦v≦0.02であり、Dは一般式[(M1O)1-p(M2O)p]a[Nb2O5]1-aを有する成分を表し、ここでM1はBa1-tSrtを表し、0≦t≦1であり、M2はSr及び/またはCaを表し、0<p<1かつ2/3<a<1であり、Zは一般式Pb(LlRr)O3を有する化合物を表し、ここでLは酸化状態IIまたはIIIで存在し、Rは酸化状態VIまたはVで存在し、LIIならば、RVI=Wと組み合わせてFe,Mg,Co,NiまたはCuから選択され、l=1/2かつr=1/2であり、LIIIならば、RV=Nb,TaまたはSbと組み合わせてFe,CrまたGaから選択され、l=1/2かつr=1/2であるか、またはRIV=Wと組み合わせてFe,CrまたGaから選択され、l=2/3かつr=1/3である。

(もっと読む)

結合器および増幅器機構

結合器は、第1のライン(31)と、第1区間(42)および第2区間(53)において第1のライン(31)に横型結合された第2のライン(32)とを備える。第1のライン(31)の単位長さ当りの第1のライン(31)と第2のライン(32)との間の静電容量は、第1区間(42)の方が第2区間(53)より大きい。第1のライン(31)と第2のライン(32)とが第1の曲部(40)を形成する。  (もっと読む)

(もっと読む)

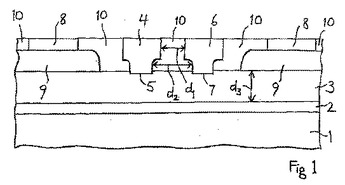

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

電力増幅回路及びフロントエンド回路

所定の送信信号に依存する前置増幅されたドライバー信号(S_DR)を供給するよう適用可能なドライバー段(DR)を備えた電力増幅回路(DIPPA)である。電力増幅回路(DIPPA)はまた、ドライバー段(DR)に電気的に結合されていて、ドライバー信号(S_DR)を第1及び第2の信号(S_1、S_2)へと分離するよう適用可能な周波数選択器(DIP)を備える。第1の信号(S_1)は第1の所定の周波数帯に対応付けられており、第2の信号(S_2)は第2の所定の周波数帯に対応付けられている。電力増幅回路(DIPPA)は、少なくとも第1及び第2の電力増幅段(PA1、PA2)を備える。第1及び第2の電力増幅段(PA1、PA2)は、周波数選択器(DIP)に電気的に結合される。第1及び第2の電力増幅段(PA1、PA2)は、それぞれ第1及び第2の信号(S_1、S_2)に依存する、それぞれ第1及び第2の増幅された信号(S_A1、S_A2)を供給する。 (もっと読む)

低電流の論理およびドライバ回路

低電流回路は、論理ステージ(E3,E4,E5)と、インバータステージ(E8)と、ドライバステージ(E9,E10)とを備える。論理ステージおよびインバータステージには電流リミッタが設けられ、電流リミッタは、Dモードフィードバックトランジスタ(D1;D2)および電圧降下を生成する要素(E1,E2;E6,E7)を備える。フィードバックループ(FL)は、Dモードフィードバックトランジスタのソースおよびゲートを、この要素を介して接続する。ドライバステージは、トーテムポール状に接続されたEモードトランジスタ(E9,E10)を備え、それは、負荷回路を接続および非接続とするように、DモードトランジスタおよびEモードトランジスタを駆動する。この回路は、オン状態において大電流能力を提供するとともに、オフ状態において無視できるほどの電流を有する。  (もっと読む)

(もっと読む)

21 - 30 / 318

[ Back to top ]