Fターム[5C024HX24]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | A/D変換、D/A変換 (1,126) | リファレンス電圧調整 (46)

Fターム[5C024HX24]に分類される特許

1 - 20 / 46

固体撮像装置、固体撮像装置の制御方法、および撮像装置

【課題】複数枚のチップを接続した構成の固体撮像装置において、それぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化と、コストの削減を図ることができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と、第2の基板に配置され、光電変換素子で発生した信号をアナログの読み出し信号として出力する読み出し回路とを具備する画素が複数配置された画素部と、読み出し信号に対して信号処理を行う信号処理回路とを備え、信号処理回路を構成する回路要素を区分基準に基づいて第1の基板側または第2の基板側に区分し、第1信号処理回路に区分された回路要素を第1の基板内に配置し、第2信号処理回路に区分された回路要素を第2の基板内に配置する。

(もっと読む)

撮像装置及び撮像システム

【課題】 ダミー画素をAD変換するサンプリングタイミングと有効画素をAD変換するサンプリングタイミングのサンプリング時間差を小さくし、横引きノイズを軽減することを可能にした撮像装置を提供すること。

【解決手段】 第1のアナログ−デジタル変換手段がアナログ−デジタル変換を行っている期間中に、ダミー画素部から出力されるアナログ信号を複数回アナログ−デジタル変換する第2のアナログ−デジタル変換手段と、第2のアナログ−デジタル変換手段によって得られた複数のデータを記録する為の複数の記録手段と、第1のアナログ−デジタル変換が行われたタイミング応じて、複数の記録手段に記録された複数のデータのうちの1つを選択する選択手段と、第1のアナログ−デジタル変換手段から得られるデータと、選択手段によって選択されたデータを演算する第1の演算手段を有する事を特徴とする構成とした。

(もっと読む)

固体撮像装置、撮像装置および撮像方法

【課題】ストリーキングを低減することができるようにする。

【解決手段】 入射された光に対応する画素読み出し信号を出力する複数の単位画素から出力された画素読み出し信号が信号線により伝達され、信号線に接続され、単位画素から画素読み出し信号を読み出すための読み出し電流を供給され、画素読み出し信号のレベルをディジタルデータに変換するための参照信号が生成され、信号線の電圧の振幅の変化を制限する閾値を参照信号のゲインに連動して切り替えて、信号線の電圧の振幅の変化が制限される。

(もっと読む)

固体撮像装置

【課題】異常な画像が出力されることを抑制することができる固体撮像装置を提供することを課題とする。

【解決手段】固体撮像装置は、行列状に配列され、光電変換により信号を生成する複数の画素(1)と、前記行列状に配列された複数の画素の列毎に設けられ、前記複数の画素の信号を読み出す複数の読み出し回路(2)と、前記複数の読み出し回路から出力される信号と時間的にレベルが変化する参照信号とを比較する複数の比較部(3)と、前記参照信号のレベルが変化を開始してからの時間をカウントするカウンタ(7)と、前記複数の読み出し回路から出力される信号と前記参照信号との大小関係が逆転したときの前記カウンタのカウント値を列毎に記憶する記憶部(4,5)と、前記記憶部が記憶するカウント値をリセットするリセット部(11〜13)とを有することを特徴とする。

(もっと読む)

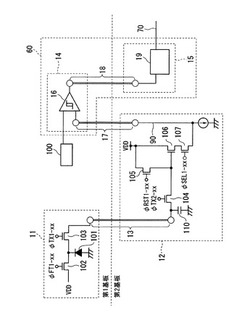

AD変換回路および撮像装置

【課題】カウントした計数値の誤差の発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ104から出力される上位用カウントクロックに基づいてカウントを行って第2の上位計数値を取得する。変更部103は、上位カウンタ101のカウントクロックの切換えの際に、カウントクロックの論理状態を所定の状態に変更する。

(もっと読む)

撮像装置

【課題】回路規模の増大を抑制しつつアナログデジタル変換の精度を向上させることができる撮像装置を提供することを課題とする。

【解決手段】撮像装置は、画素のリセット状態における画素に基づく基準信号と時間に対して変化する基準信号用参照信号とを比較し、画素の非リセット状態における画素に基づく有効信号と基準信号用参照信号より時間に対する変化率が大きい有効信号用参照信号とを比較する比較回路と、画素に基づく基準信号と基準信号用参照信号との大小関係が逆転するまでの間に第1のカウント値のカウントを行い、画素に基づく有効信号と有効信号用参照信号との大小関係が逆転するまでの間に第2のカウント値のカウントを行うカウンタ回路と、基準信号用参照信号及び有効信号用参照信号の時間に対する変化率の違いに対応する第1のカウント値及び第2のカウント値の分解能の違いを補正する補正部とを有する。

(もっと読む)

撮像装置

【課題】AD変換のダイナミックレンジを拡大することができる撮像装置を提供することを課題とする。

【解決手段】撮像装置は、光電変換により信号を生成する第1の画素と、第1の画素に対して同一行に配列され、光電変換により信号を生成する第2の画素と、第1の画素に基づく信号(SIG)と時間に対してレベルが変化する第1の参照信号(RAMP_A)とを比較する第1の比較器と、第2の画素に基づく信号(SIG)と第1の参照信号に対して時間に対する変化率が異なる第2の参照信号(RAMP_B)とを比較する第2の比較器と、第1の比較器が第1の画素に基づく信号と第1の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第1のカウンタと、第2の比較器が第2の画素に基づく信号と第2の参照信号との大小関係が逆転することを示す信号を出力するまでの間にカウントを行う第2のカウンタとを有する。

(もっと読む)

撮像装置

【課題】冗長にラッチ回路の回路規模を増大させることなく駆動負荷を軽減し、内部の信号情報を確実に転送することができる回路構成を備えた撮像装置を提供する。

【解決手段】入射光量に応じた画素信号を出力する画素が二次元の行列状に複数配置された画素部と、画素部の1列毎または複数列毎に配置され、対応する列の画素の画素信号の大きさに応じたn(nは1以上の自然数)ビットのデジタル信号を出力するm(mは1より大きい自然数)個のデジタル信号出力回路と、デジタル信号出力回路のそれぞれに対応して配置され、対応するデジタル信号出力回路のデジタル信号の各ビットの信号をそれぞれ保持するn個のラッチユニットを具備したm個のラッチ回路と、ラッチユニットのそれぞれに対応して配置され、対応するラッチユニットが保持したデジタル信号を、隣接するラッチ回路内の対応するラッチユニットに転送するm−1個のスイッチと、を備える。

(もっと読む)

固体撮像装置用信号処理装置

【課題】面積の増加を抑制しつつ、フレームレートを向上できる固体撮像装置用信号処理装置を提供する。

【解決手段】本発明に係るアナログフロントエンド200は、CCD部100により出力されるアナログ信号を処理するアナログフロントエンド200であって、前記アナログ信号を増幅するアンプ201と、時系列に入力される、アンプ201により増幅されたn個のアナログ信号を保持するためのn個の容量203を含むマルチホールド回路210と、n個の容量203に保持されているn個のアナログ信号をn個のデジタル信号に変換するAD変換回路211とを備える。

(もっと読む)

固体撮像装置及びその駆動方法

【課題】簡単な回路構成で参照ランプ電圧に対してオフセット電圧を付加することができる固体撮像装置を提供することを課題とする。

【解決手段】固体撮像装置は、複数の画素の各列に共通に接続される出力線(13)と、ランプ状に変化する参照ランプ電圧を生成する参照ランプ生成回路(17)と、参照ランプ電圧と出力線のアナログ電圧とを比較する比較器(15)と、比較器の比較開始後に比較器の出力信号が反転するまでの時間をデジタル値としてカウントするカウンタ部(18,19)とを有し、参照ランプ生成回路は参照ランプ電圧をオフセット電圧に設定し、その後、比較器の入力端子がリセットされ、その後、参照ランプ生成回路は、参照ランプ電圧をオフセット電圧からランプ開始電圧にリセットし、その後、参照ランプ生成回路はランプ開始電圧からランプ状の参照ランプ電圧を生成し、比較器は比較を開始する。

(もっと読む)

固体撮像素子および駆動方法、並びに電子機器

【課題】アナログゲインを上げたときに、情報の損失を防ぎ、高S/Nの画像を得る。

【解決手段】CMOSイメージセンサは、物理量を検知する画素が行列状に2次元に配置されてなる画素アレイ部と、画素アレイ部から読み出したアナログの複数の系統の画素信号に対してAD変換を行うAD変換回路と、画素信号のゲイン設定に応じて、AD変換部によるAD変換の量子化単位を設定する制御回路とを備え、制御回路は、画素信号のゲイン設定に応じて、少なくとも1系統の画素信号に対するAD変換のデジタル出力の階調数を決定する。本技術は、例えば、感度の異なる複数の信号を得てダイナミックレンジを拡大するCMOSイメージセンサに適用することができる。

(もっと読む)

二重の集積時間および条件付選択を備えるイメージセンサ

【課題】二重の集積時間および条件付選択を備えるイメージセンサを提供する。

【解決手段】フォトダイオードから蓄積ノードへの第1の転送は第1の期間(Ti1)の後に、第2の転送は第1の期間とは異なる第2の期間(Ti2)の後に行う。第1の電荷転送後の蓄積ノードの電位を読取回路の第1のコンデンサ内で(shs1)、蓄積ノードを再初期化した後の電位を第2のコンデンサ内でサンプリングする(shr)。第2の転送後に取られる電位レベルを第1のコンデンサ内で条件付きで再サンプリングする(shs2)。第1の転送後の信号レベルを短いランプ期間(RMP1)にわたりランプ型変換器の差動増幅器に適用し、終了時における増幅器の出力の状態に応じ再サンプリングを実行するかどうかに関する決定を下し、コンデンサ内でサンプリングした差動信号レベルの最終的ランプ(RMP2)を用いた完全なアナログ−デジタル変換が終了する。

(もっと読む)

固体撮像装置

【課題】煩雑な位相合わせが必要なく、高速化や高画素数化が可能な固体撮像装置を提供する。

【解決手段】状態変化検出回路1002は、下位ラッチ回路9によってラッチされたパルス信号のうち、複数の遅延素子のうちの2つの遅延素子から出力されたパルス信号を順に比較し、2つのパルス信号の間で状態が異なるときに状態変化検出信号を出力する。エンコード信号ラッチ回路1003は、状態変化検出回路1002に入力されるパルス信号を出力した遅延素子に応じた状態を有するエンコード信号が入力され、状態変化検出信号が入力された場合にエンコード信号をラッチする。

(もっと読む)

画像信号処理装置および固体撮像装置

【課題】OB画素から読み出された黒レベルが一定になるように黒レベルを補正する。

【解決手段】フィードバッククランプ回路102は、CMOSセンサ101のOB画素から読み出された黒レベルが目標値に近づくようにクランプパラメータPCを増減させる。この時、フィードバッククランプ回路102は、CMOSセンサ101のOB画素から読み出された黒レベルに基づいてクランプパラメータPCの変化量を制御する。

(もっと読む)

半導体装置および固体撮像装置

【課題】画素情報の読出し速度を向上させることが可能な半導体装置および固体撮像装置を提供する。

【解決手段】カラムADCは、PGA22と、縦列接続された2つの巡回型ADCとを含む。PGA22は、画素の黒レベルおよび信号レベルの差分を増幅した信号にVrefを加算した電位をPGA画素情報として出力する。第1ADC24_1は、Vrefを参照電位としてサンプリングして保持するとともに、PGA画素情報を信号電位としてサンプリングして保持し、これらの差分信号であるi行の画素情報に応じてデジタル値の中の上位ビットを生成すると、(i+1)行の画素情報のサンプリングを開始する。第2ADC24_2は、第1ADC24_1が(i+1)行の画素情報をサンプリングして保持するのと並行して、第1ADC24_1によって生成された上位ビットに応じて該デジタル値の中の下位ビットを生成する。

(もっと読む)

固体撮像素子及び参照電圧の調整方法

【課題】固体撮像素子の電源電圧の低電圧化が進んでも、所望の波形を有する参照電圧RAMPを生成する。

【解決手段】固体撮像素子100は、画素アレイ部1と、テスト電圧印加部2と、参照電圧生成回路9と、動作点制御部8とを備える構成とする。テスト電圧印加部2は、種々の電圧レベルのテスト電圧Vtを対応する読み出し信号線VSLに印加する。参照電圧生成回路9は、動作点が変更可能なMOSトランジスタを有する。そして、動作点制御部8は、テスト電圧及び参照電圧に基づいて、参照電圧生成回路9内のMOSトランジスタの動作点の調整処理を制御する。

(もっと読む)

AD変換装置およびその方法、固体撮像素子およびその駆動方法、並びにカメラシステム

【課題】間欠カラム動作時におけるP相ばらつき量や縦筋量を小さくすることが可能で、ひいては画質の向上を図れる固体撮像素子、およびカメラシステムを提供する。

【解決手段】ADC群150は、画素の列配列に対応して配置され、読み出し信号電位と参照電圧とを比較判定し、その判定信号を出力する複数の比較器151と、比較器の出力により動作が制御され、対応する上記比較器の比較時間をカウントする複数のカウンタ152とを有し、比較器200(151)は、縦続接続された第1アンプと第2アンプを有し、行動作開始時に各カラム毎に動作点を決めるための初期化(AZ)用スイッチ(AZスイッチ)に印加する初期化信号を、水平方向における間欠動作の基本単位分だけ並列独立制御することで、非動作比較器のAZスイッチのみ非動作行開始時にオフに固定にする。

(もっと読む)

固体撮像装置

【課題】格段の回路増加をせず、回路の利用効率を向上させ、かつ、ダイナミックレンジの拡大を可能とする固体撮像装置を提供する。

【解決手段】ある列のカラムアンプと、異なる列のカラムアンプとを接続する手段を設けるとともに、間引き動作において、読み出される列のカラムアンプと異なる読み出されない列のカラムアンプを利用してニー補正をかけることによりAD入力時の画像信号のダイナミックレンジの拡大を図る。読み出されない列のカラムアンプに通常動作の設定ゲインより低いゲイン値を設定し特定のニー電圧分だけオフセットして出力をさせる。通常出力側の出力レベルが特定のニー電圧を越えた時点で出力を読み出されない列に切り替える動作を行うことができる。

(もっと読む)

撮像装置及び放射線撮像システム

【課題】簡単な構成で、複雑な演算を用いることなく、ラインノイズアーチファクトを低減可能な撮像装置を提供することを課題とする。

【解決手段】行及び列方向に複数配置され、各々が放射線又は光を電荷に変換する変換素子(102)と、前記電荷に基づく電気信号を出力するスイッチ素子(103)と、を有する複数の画素と、列方向の複数の前記スイッチ素子に接続された複数の信号配線(110)と、前記複数の信号配線に対応する複数のサンプルホールド回路を有し、前記複数の信号配線に接続された読み出し回路(105)と、を有する撮像装置であって、前記複数の画素は、複数の群に分割されており、前記複数のサンプルホールド回路は、前記複数の画素のうち所定行の画素から前記複数の信号配線を介して前記読み出し回路に並列に出力された電気信号のサンプルホールドを、前記複数の群毎に異なるタイミングで行うことを特徴とする撮像装置が提供される。

(もっと読む)

信号処理回路、固体撮像素子およびカメラシステム

【課題】開始直後から線形性のとれた参照信号を生成することが可能で、セトリング時間を大幅に改善することができ、ダイナミックレンジを拡大することが可能な信号処理回路、固体撮像素子およびカメラシステムを提供する。

【解決手段】時間とともに電圧値が変化するランプ波形の参照信号RAMPを、電流を変化させて生成する参照信号生成回路161と、ランプ波である上記参照信号とカラム毎に供給されるアナログ信号電位とを比較する複数の比較器151−1を含む信号処理部151と、を有し、参照信号生成回路161は、参照信号を生成するための電流とは別の整定電流を参照信号の開始時から一定期間流し込む電流源I162を含む。

(もっと読む)

1 - 20 / 46

[ Back to top ]