国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

31 - 40 / 487

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

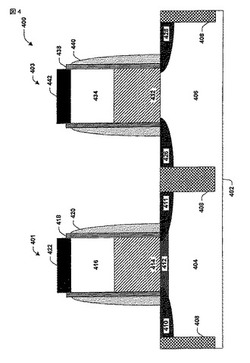

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

半導体装置

【課題】大電力の制御を行う、高耐圧の半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の、ゲート電極と重畳する酸化物半導体層と、酸化物半導体層と接し、端部をゲート電極と重畳するソース電極及びドレイン電極と、を有し、ゲート電極と酸化物半導体層が重畳する領域において、ゲート絶縁層は、ドレイン電極と端部を重畳する第1の領域と、前記第1の領域と隣接する第2の領域と、を有し、第1の領域の静電容量は第2の領域の静電容量より小さいトランジスタを提供すること。

(もっと読む)

化合物半導体装置

【課題】 電流コラプスを抑制するとともに、高耐圧動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】 SiC基板10上に形成されたi−GaNバッファ層12と、i−GaNバッファ層12上に形成されたn−AlGaN電子供給層16と、n−AlGaN電子供給層16上に形成されたn−GaNキャップ層18と、n−GaNキャップ層18上に形成されたソース電極20及ドレイン電極22と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成されたゲート電極26と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成された第1の保護層24と、ゲート電極26とドレイン電極22との間の第1の保護層24に形成されたn−GaNキャップ層18に達する開口部28に埋め込まれ、第1の保護層24とは異なる絶縁層よりなる第2の保護層30とを有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】MISFETが微細化されてくると、単チャネル効果が更に顕著となり、トランジスタの特性ばらつきが増大しやすくなる。ここで、トランジスタの特性ばらつきは、従来のゲート長に依存するものに加えて、オフセットスペーサ長やサイドウォールスペーサ長に依存するものの影響が強くなることが本願発明者らによって明らかにされた。

【解決手段】本願の発明は、CMIS型半導体集積回路装置の製造方法において、オフセットスペーサ長とサイドウォールスペーサ長の和をNチャネルMISFETとPチャネルMISFETに於いて、調整するものである。

(もっと読む)

半導体装置

【課題】本発明は、金属膜の端部の応力により金属膜の端部直下の表面電極がダメージを受けることを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、基板24と、該基板24の上に、アルミを含む材料で形成された表面電極26と、該表面電極26の上に、はんだ付け可能な材料で形成された金属膜28と、該表面電極26の上の部分と、該金属膜28の端部に重なる重畳部分30aとが一体的に形成されて該金属膜28の端部を固定する端部固定膜30と、を備えたことを特徴とする。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ液晶表示装置の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極、ゲート絶縁層、活性層及びソースドレイン電極を有した薄膜トランジスタであって、該ゲート電極は該活性層のチャンネル領域と重なり、該ゲート絶縁層は該ゲート電極と該活性層間に設けられており、該ソースドレイン電極と該活性層のソースドレイン領域は重なり、該活性層と前記ソースドレイン電極間に電子の走行を許容する薄いSiNx又はSiOxNy層が設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

半導体装置

【課題】金属酸化物中の酸素欠損を低減し、電気的特性の安定した半導体装置を提供することを目的の一とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の金属酸化物膜と、第1の金属酸化物膜に接して設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極上に設けられたパッシベーション膜と、を有し、パッシベーション膜は、第1の絶縁膜と、第2の金属酸化物膜と、第2の絶縁膜とが順に積層された半導体装置である。

(もっと読む)

31 - 40 / 487

[ Back to top ]