Fターム[2G132AE10]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 入出力兼用端子への接続回路 (19)

Fターム[2G132AE10]に分類される特許

1 - 19 / 19

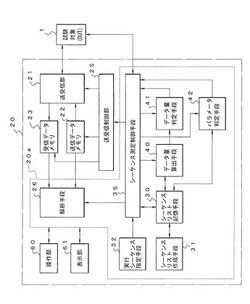

移動体通信装置試験システムおよび試験方法

【課題】試験対象に対してシーケンス測定を実行する際に、取得データ量の面で、誤った測定の無駄な測定をしないで済むようにする。

【解決手段】シーケンス測定制御手段35が実行指定された測定シーケンスにしたがう制御を開始する前に、実行指定された測定シーケンスで送受信部21が解析対象として取得する予定のデータ量の合計値を算出するデータ量算出手段40と、算出したデータ量の合計値が受信データメモリ23の所定容量に応じて予め設定した許容値を超えるか否かを判定するデータ量判定手段41とを備え、シーケンス測定制御手段35は、データ量判定手段41により算出したデータ量の合計値が許容値を超えると判定されたとき、その判定結果を表示部61に表示して、ユーザーに通知する。

(もっと読む)

半導体試験装置および半導体試験装置における静電気保護方法

【課題】静電気耐量を高めた半導体試験装置を提供する。

【解決手段】測定対象デバイスに電気信号を出力する1または複数個の信号出力部と、信号出力部に対応して設けられ、信号出力部と測定対象デバイスとの間の電気的接続のオンオフを切り替える半導体リレーと、測定対象デバイスとの直接的あるいは間接的な接続の前に、半導体リレーをオンにする制御部とを備えた半導体試験装置。測定対象デバイスとの直接的あるいは間接的な接続の前に、さらに、信号出力部から0Vの電圧を出力させるようにしてもよい。

(もっと読む)

半導体試験回路、半導体試験用冶具、半導体試験装置及び半導体試験方法

【課題】多くのDUTを同時に試験可能な半導体試験回路を提供する。

【解決手段】信号処理部12が、テスタ20から信号線SLを介して入力された試験信号を複数のDUT30−1〜30−nに分配して供給するとともに、試験信号に基づいた複数のDUT30−1〜30−nからの応答信号を合成した試験結果を生成し、試験結果出力部13が、その試験結果を、入力された試験信号とは異なる電圧レベルにして、信号線SLを介してテスタ20に出力する。

(もっと読む)

試験装置および試験方法

【課題】試験装置の消費電力を削減する。

【解決手段】被試験デバイスに試験信号を与えて被試験デバイスを試験する試験装置であって、試験の周期を与える周期信号を生成する周期信号発生部と、周期信号に基づいて、試験信号のパターンを示す試験パターンおよび試験信号を出力することの許可を示す出力許可パターンを生成するパターン生成部と、周期信号の少なくとも現周期における出力許可パターンが許可状態であるときに、試験パターンに従う出力波形を生成する出力波形生成部と、出力許可パターンに従い、許可波形を生成する許可波形生成部と、許可波形が許可状態である場合に、出力波形に従い試験信号を出力する信号出力部と、を備えた試験装置を提供する。

(もっと読む)

DCLデバイスおよびそれを用いた半導体試験装置

【課題】従来のDCLデバイスは、被試験半導体の入力専用ピン、出力専用ピン、入出力兼用ピンのいずれにも対応できるという柔軟性はあるが、DCLデバイスは一般に効果であり、かつ1つのピンにしか対応できないので、消費電力、実行面積が大きくなってしまうという課題を解決する。

【解決手段】2つ以上の端子を具備し、ドライバを介してこれらの端子にパターン信号を出力すると共に、これらの端子に負荷を接続し、かつこれらの端子からの入力信号を選択して比較器に入力するようにした。また、このDCLデバイスを半導体試験装置に用いた。使用するDCLデバイスの数を削減できるので、低消費電力化、小型化、コストダウンが可能になる。また、1つのデバイスで入力専用、出力専用、入出力兼用のいずれのピンにも対応できるので、デバイスの種類を削減できる。

(もっと読む)

試験装置

【課題】双方向差動インタフェースを有するDUTの試験装置を提供する。

【解決手段】メインドライバアンプAMP0は、DUT102に送信すべきパターンデータPATにもとづいて第1差動信号Vdを生成する。第1レプリカドライバアンプAMP1は、パターンデータPATにもとづいて第2差動信号Vcpを生成する。第2レプリカドライバアンプAMP2は、パターンデータPATにもとづいて第3差動信号Vcnを生成する。第1コンパレータCMP1は、ノードN1とノードN2の電圧を比較し、第2コンパレータCMP2はノードN3とノードN4の電圧を比較する。

(もっと読む)

試験装置及び製造方法

【課題】高分解能のDA変換器を備える被試験デバイスを、そのDA変換器以下の分解能を有するAD変換器を用いて試験する。

【解決手段】デジタル入力信号に応じたアナログ出力信号を出力する被試験デバイスを試験する試験装置であって、試験用のデジタル入力信号を被試験デバイスに供給する試験信号供給部と、試験用のデジタル入力信号に応じたアナログ基準信号を出力する基準信号出力部と、試験用のデジタル入力信号に応じて被試験デバイスが出力するアナログ出力信号と、アナログ基準信号との差を示すアナログ差分信号を出力する差分器と、アナログ差分信号に基づいて、被試験デバイスが出力したアナログ出力信号の良否を判定する判定部とを備える。

(もっと読む)

システムインパッケージ、ロジックICおよびメモリIC

【課題】端子数を増加せずに、ボンディング接続の不良箇所を特定できるSiPの実現。

【解決手段】IC2,3をパッケージ1に搭載し、IC2,3の端子間をボンディングワイヤで接続したSiP1であって、IC2は、試験モード設定回路13と、第1のグループの各端子20A-20Cに対応して設けられた出力切替回路16A-16Cと、第2のグループの各端子21A-21Cに対応して設けられた入力切替回路18A-18C,19A-19Cと、入力したテスト信号を判定する判定回路15A-15Cと、を備え、IC3は、試験モード設定回路32と、第1のグループの各端子33A-33Cに対応して設けられた入力回路35A-35Cと、第2グループの各端子34A-34Cに対応して設けられた出力切替回路37A-37C,38A-38Cと、を備え、試験モード時にはIC2の出力切替回路は初段テスト信号または前段の入力テスト信号を反転して出力し、IC3の出力切替回路は、前段の入力テスト信号を反転して出力する。

(もっと読む)

半導体試験装置及びその調整方法

【課題】高精度のタイミング調整が可能であり、且つ短時間でタイミング調整を行うことができる半導体試験装置及びその調整方法を提供する。

【解決手段】半導体試験装置1は、半導体試験装置本体2、複数の交換可能な調整用治具3a、及び切替装置4を備える。上記の半導体試験装置本体2は、被試験デバイスの信号入力ピンに与える信号を出力する複数のドライバピンブロック11a〜11nと、被試験デバイスの信号入出力ピンに与える信号を出力するとともに信号入出力ピンから出力される信号を測定する複数のIOピンブロック12a〜12nとを備える。上記の調整用治具3aは、ドライバピンブロック11a〜11nの信号出力端子34a〜34n並びにIOピンブロック12a〜12nの信号出力端子44a〜44n及び及び信号入力端子45a〜45nを所定の接続状態にする。

(もっと読む)

テスタ入力/出力共用

一実施態様では、単一のテスタチャネルを用いて複数のDUTを試験する方法が提供され、当該方法は、単一のテスタチャネルによって各DUTに同時に入力信号を与えることを含む。方法は、DUTのそれぞれにクロック信号を与えることをさらに含む。DUTのそれぞれに与えられるクロック信号として、連続して遅延したクロック信号を用いることができ、これらのクロック信号が一連のDUTに与えられる。方法は、クロック信号を用いて、先行するDUTの出力が遷移する前の状態に戻される前に、次のDUTに出力遷移を与えさせることを含む。方法は、入力信号及びクロック信号に応答して、単一のテスタチャネルによってDUTのそれぞれの出力遷移を検出することをさらに含む。 (もっと読む)

メモリ試験装置及び方法

【課題】並列に試験される被試験メモリ毎に良否判定を省略する箇所を個別に設定可能とすることで、試験時間の短縮を図ることができるメモリ試験装置及び方法を提供する。

【解決手段】メモリ試験装置10は、複数の被試験メモリD1〜D32に試験信号を書き込むとともに複数の被試験メモリD1〜D32に書き込まれた信号を読み出して、複数の被試験メモリD1〜D32の試験を並列して行う。このメモリ試験装置10は、複数の被試験メモリD1〜D32の各々から読み出される信号を被試験メモリD1〜D32毎個別にマスクするマスクデータを記憶するメモリ21と、複数の被試験メモリD1〜D32の各々から読み出される信号をメモリ21に記憶されたマスク信号に基づいて被試験メモリD1〜D32毎に個別にマスクして被試験メモリD1〜D32の良否判定を行う判定部26とを備える。

(もっと読む)

半導体装置と半導体装置のテスト方法

【課題】マルチチップモジュールの性能を維持しつつ、信頼性の高い試験を可能にした半導体装置とテスト方法を提供する。

【解決手段】第1半導体チップと上記第2半導体チップとでマルチチップモジュールを構成する。第1半導体チップから第2半導体チップに対する動作指示の有効/無効を示す第1信号を外部端子に接続する。第2半導体チップの動作指示の有効/無効を受け取る第2信号を外部端子に接続する。第1半導体チップのリセット指示を行なう第3信号を外部端子に接続する。第1信号と第2信号マルチチップモジュール外に一旦引き出し、マルチチップモジュール外で結合変更可能なように構成し、第1、第2、第3信号の制御をマルチチップモジュール外部で行なうことで、試験対象とすべき半導体チップを単体の半導体チップを持つ半導体装置と等価にテスト可能にする。

(もっと読む)

メモリインターフェース回路及びメモリ試験装置

【課題】 メモリ動作試験におけるインターフェース回路の判定を容易にすること。

【解決手段】

メモリインターフェース回路1が、メモリコントローラ2が生成したライトデータを保持する第1保持部18と、メモリコントローラ2が生成したリードデータを、メモリの書き込み遅延に相当する時間遅延させて出力する遅延部10と、リードデータがメモリに対して出力中であることを表すリードタイミング信号を生成するリードタイミング信号生成部15と、遅延部10が遅延出力したリードデータを、リードタイミング信号生成部15が生成したリードタイミング信号に同期させて出力するリードタイミング制御部9と、リードタイミング制御部9が出力するリードデータを保持する第2保持部19と、第1保持部18に保持されたライトデータと、第2保持部19に保持されたリードデータとが一致するか否かを判定する判定部12とを備える。

(もっと読む)

半導体検査装置及び半導体テスト方法

【課題】作成期間及び費用が押さえられ、且つ、テスト時の誤差が少なくなる半導体検査治具を提供する。

【解決手段】 半導体デバイスのテストを行うテスタと、半導体検査治具と、前記半導体デバイスの種類毎に固有である変換ボードと、を具備し、前記半導体検査治具は、前記テスタの複数の信号端子の各々を前記半導体デバイスの複数の信号端子の各々、又は電源端子に接続する配線ラインと、前記テスタの電源端子を前記変換ボードを介して前記半導体デバイスの所定の電源端子に接続した前記配線ラインに接続する電源ラインと、を備える。

(もっと読む)

テストシステムチャネルとインタフェースをとるための双方向バッファ

エミッタフォロワートランジスタまたはソースフォロワートランジスタは、低電力DUTがテストシステムチャネルを駆動することができるようにするために、DUTとテストシステムコントローラとの間に、ウエハテストシステムのチャネルにおいて提供される。バイパス抵抗器は、双方向信号伝達がDUTチャネルとテストシステムコントローラとの間に提供されることができるようにするために、およびパラメトリックテストが実行されることができるようにするために、エミッタフォロワートランジスタのベースとエミッタとの間に含まれる。エミッタフォロワートランジスタおよびバイパス抵抗器は、プローブカード上に提供され得、プルダウンターミネーション回路は、テストシステムコントローラに含まれる。テストシステムコントローラは、エミッタフォロワートランジスタのベース・エミッタ電圧降下に対する補正を提供し得る。  (もっと読む)

(もっと読む)

集積回路、テスト回路およびテスト方法

【課題】パラレル・シリアル変換を行う集積回路から出力される高速シリアルデータのファンクションテストを行うことができ、しかも集積回路から出力される同期クロックの変化タイミングに対するシリアルデータのセットアップタイムおよびホールドタイムのテストも行うことができるようにする。

【解決手段】本発明のテスト回路は、パラレルデータをクロックに同期してシリアルデータに変換し、これらのシリアルデータおよびシリアルデータに同期したクロックを出力する機能を有する集積回路をテストするもので、遅延制御信号に応じて、集積回路から出力されるシリアルデータと同期クロックとの間を相対的かつ可変的に遅延して出力する遅延可変回路と、遅延可変回路から出力されるクロックを用いて、遅延可変回路から出力されるシリアルデータをパラレルデータに変換するシリアル・パラレル変換回路とを備える。

(もっと読む)

半導体デバイステスタのためのインターフェース装置

半導体テスタを被試験デバイスに接続するための信号インターフェース。そのインターフェースは汎用構成部品及びカスタム化構成部品を含む。汎用構成部品は、テスタと被試験デバイスとの間の信号経路内に接続することができる電子素子の複数の複製物を含む。カスタム化構成部品は特定の被試験デバイスのために構成され、汎用構成部品上の汎用コンタクト箇所と被試験デバイス上の試験箇所との間の接続を提供する。さらに、カスタム化構成部品は、汎用構成部品上の電子素子を相互接続するために用いることができる導電性部材を有する。その接続は電子素子を信号調整回路内に組み込み、それにより、被試験デバイス上の特定の試験箇所のI/O特性と一致するインターフェースを通じて信号経路が与えられる。汎用構成部品及びカスタム化構成部品は、半導体ウェーハ上に製造することができる。  (もっと読む)

(もっと読む)

半導体集積回路検査装置、半導体集積回路検査方法、及びプログラム

【課題】 論理シミュレーション及び故障シミュレーションを行わず、半導体集積回路の良品/不良品の判定を簡易に行うことを可能にする。

【解決手段】 抵抗ユニット3の抵抗器の各々を、DUT1の出力端子と電圧印加回路5との間にそれぞれ選択的に接続し、DUT1の入力端子に所定の動作パターン信号を入力する。この入力によって、前記接続された各抵抗器にそれぞれ流れる電流量の総和を、電流測定回路4で所定の動作パターン信号の動作ブロックごとに測定する。LSIテスタ8は、この電流測定回路4で測定された電流量の総和を、前記所定の動作パターン信号の入力で正常に動作することが予め確認されているDUT1と同一機能を持った良品サンプルをDUT1の代わりにして、電流測定回路4で測定された動作ブロックごとの電流量の総和の正常値と比較する。

(もっと読む)

集積回路、試験システム、および、集積回路からエラーデータを読み出すための方法

【課題】各集積回路を試験する場合に試験機の各接続チャネル数を低減できて、エラーの発生や、コストを抑制できる集積回路、試験システムおよび試験方法を提供する。

【解決手段】エラーデータが試験モードに応じて読み出され、上記エラーデータを、第1および第2データ出力部を介してそれぞれ出力できる集積回路を設ける。集積回路に試験回路を、第1読み込み命令が印加されるとき、エラーデータを第1データ出力部に出力し、第2データ出力部を高インピーダンスに切り替え、第2読み込み命令が印加されるとき、エラーデータを第2データ出力部に出力し、第1データ出力部を高インピーダンスに切り替えるように設ける。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]