Fターム[5F003BH10]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | フィールドプレート (10)

Fターム[5F003BH10]に分類される特許

1 - 10 / 10

バイポーラトランジスタ

エミッタ領域(50)と、ベース領域(40)と、コレクタ領域(20)と、ベース領域(40)から離間し、それを囲む、保護領域(200)とを備える、バイポーラトランジスタ。保護領域(200)は、ベース領域(40)を形成するために使用される同一ドーピングマスクを使用して形成することができ、動作中には、空乏層を展開する役割を果たすことができる。また、本発明は、上記バイポーラトランジスタを製造する方法であって、エミッタ領域と、ベース領域と、コレクタ領域とを形成することと、該ベース領域を囲む保護領域を形成することとを含む、方法も提供する。  (もっと読む)

(もっと読む)

シリコンカーバイドバイポーラ接合トランジスタ

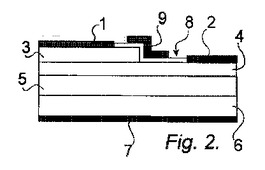

本発明は、シリコンカーバイド(SiC)バイポーラ接合トランジスタ(BJT)に関し、当該トランジスタ上のエミッタコンタクトとベースコンタクトと(1、2)の間の表面領域には、バルクSiC内の電位と比較して負の表面電位が与えられている。  (もっと読む)

(もっと読む)

半導体装置

【課題】 エミッタ-ベース間に発生する順方向電圧の温度特性を利用するバイポーラトランジスタにおいて、素子面積を縮小することを目的とする。

【解決手段】 エミッタ-ベース間に発生する順方向電圧の温度特性を利用するバイポーラトランジスタにおいて、第二の導電型であるベース電極用高濃度不純物領域と、第一の導電型であるコレクタ電極用高濃度不純物領域とを直接に接触させ、不要な分離領域を形成しないことで素子面積を縮小する。

(もっと読む)

合併したバイポーラ回路およびCMOS回路とその製造法

【課題】高特性の合併したバイポーラ回路とCMOS回路とをCMOS処理工程だけのコストで製造する方法および回路を提供する。

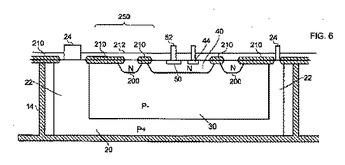

【解決手段】BiCMOS集積回路を製造する方法は、バイポーラ・トランジスタのベース領域211とNチヤンネルMOSトランジスタのP形ウエル212とを1つの注入段階で作成する段階と、バイポーラ・トランジスタのコレクタ接触体ウエル213とPチヤンネルMOSトランジスタのN形ウエル208とを1つの注入段階で作成する段階とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】同一のSOI基板上に、MOSトランジスタと、耐圧が十分に確保されたラテラルバイポーラトランジスタとが形成された半導体装置を提供する。

【解決手段】埋め込み酸化膜14上に形成され、p型のチャネル領域60を挟んで形成されるn型のソース領域62s及びn型のドレイン領域62dと、チャネル領域60上にゲート酸化膜52を介して形成されたゲート電極54と、を有するMOSトランジスタ51と、p型のベース領域90を挟んで形成されるn型のコレクタ領域92c及びn型のエミッタ領域92eと、ベース領域90とチャネル幅方向において隣接するp型のベースコンタクト領域89と、ベース領域90上に第2酸化膜82を介して形成されたダミーパターン84と、を有するバイポーラトランジスタ81と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電流増幅率hFEやコレクタ・エミッタ間の耐圧を、他の半導体素子に影響を与えずに、容易に調整することができる半導体装置及びその製造方法を提供する。

【解決手段】本半導体装置は、第1の導電型不純物を含む半導体基板と、半導体基板上に形成された第2の導電型不純物を含む第1の半導体領域と、第1の半導体領域上に、周囲を第1の導電型不純物を含む第2の半導体領域で囲むように形成された、第2の導電型不純物を含む第3の半導体領域と、第2の半導体領域直下の第1の半導体領域内に形成された、第1の半導体領域より高濃度の第2の導電型不純物を含む埋込半導体領域と、第2の半導体領域及び第1の半導体領域の接合部に形成された、第1の半導体領域より高濃度の第2の導電型不純物を含む介挿半導体層とを有し、第3の半導体領域をエミッタとし、第2の半導体領域をベースとし、埋込半導体領域をコレクタとするバーティカル型バイポーラトランジスタである。

(もっと読む)

半導体装置

【課題】IGBTとダイオードが同じ半導体基板に形成されてなる小型の半導体装置であって、ダイオードのリカバリー特性の劣化を抑制できる半導体装置を提供する。

【解決手段】半導体基板1におけるIGBTの形成領域とダイオードの形成領域以外の領域(周辺部)において、主面側の表層部に、P導電型の第5半導体領域6が形成され、第1半導体領域2、第3半導体領域4および第5半導体領域6が、電気的に共通接続され、第5半導体領域6に対向して、裏面側の表層部に、P導電型の第6半導体領域7aが形成され、第2半導体領域3、第4半導体領域5および第6半導体領域7aが、電気的に共通接続されてなる半導体装置100とする。

(もっと読む)

半導体装置

【課題】共通の半導体基板の上に複数の半導体素子を形成すると寄生トランジスタが形成される。

【解決手段】寄生トランジスタの動作を抑制することができる複合半導体装置は、p型の第1の半導体領域7の上にn型の第2の半導体領域8と環状に形成された第3、第4及び第5の半導体領域9,11,12を有する。最も内側に配置されたn+型の第5の半導体領域12の内側に抵抗膜3が配置されている。この抵抗膜3はドレイン電極18と接続導体30との間に接続されている。

(もっと読む)

半導体装置

【課題】 半導体装置において、反転領域対策を、既存の製造工程の条件を変えないで実現することを課題とする。

【解決手段】 N型エピタキシャル層4上にP型拡散層よりなる抵抗素子5が形成してあり、N型エピタキシャル層4上にシリコン酸化膜40が形成してあり、抵抗素子5の端から出ているアルミニウム配線8,9がシリコン酸化膜40上を延在している。シリコン酸化膜40は、N型エピタキシャル層4内に食い込んで厚みが増してある厚み付加部分42を枠状に有する。厚み付加部分42は、シリコン酸化膜40の反転電圧を上げる。厚み付加部分42は酸素イオンの注入及びアニール処理によって形成される。

(もっと読む)

CMOS製造技術と両立可能なバイポーラデバイス

【課題】性能を向上する新規なバイポーラデバイスを提供する。

【解決手段】本発明は、バイポーラデバイス30を開示する。エミッタ33が半導体基板に形成される。コレクタ34が、エミッタ33から横方向に空間を置いて基板に設けられる。ゲート端子38は基板上に形成され、エミッタ33とコレクタ34間の空間を規定する。外部ベース35は、エミッタ33またはコレクタ34の何れか一方から所定の距離を隔てて、基板上に形成される。外部ベース35は、エミッタ33またはコレクタ34の何れか一方から所定の距離を有して基板上に形成され、基板に設けた分離構造31で周囲を囲まれた穴によって活性領域32を規定し、この活性領域32に、ベース35,エミッタ33,コレクタ34およびゲート端子38が配置される。

(もっと読む)

1 - 10 / 10

[ Back to top ]