Fターム[5F003BP36]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | 接着 (15)

Fターム[5F003BP36]に分類される特許

1 - 15 / 15

半導体装置およびその製造方法

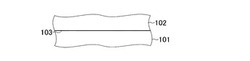

【課題】ヘテロ構造のpn接合において、電子が妨げられることなく注入されるようにする。

【解決手段】Gaを含む窒化物半導体からなるn型の窒化物半導体層101と、窒化物半導体層101に接合して形成されたp型のシリコンからなるp型シリコン層102とを少なくとも備える。窒化物半導体層101とp型シリコン層102とは、接合界面103により接合している。

(もっと読む)

大面積ナノ可能マクロエレクトロニクス基板およびその使用

【課題】複数の半導体デバイスを有する電子的な基板を得るための方法および装置。

【解決手段】ナノワイヤ薄膜が、基板上に形成される。ナノワイヤ薄膜は、動作電流レベルを達成するのに十分なナノワイヤの密度を有するように形成される。複数の半導体領域が、ナノワイヤ薄膜に画定される。コンタクトが、半導体デバイス領域において形成され、それによって、電気的な接続を複数の半導体デバイスに提供する。さらに、ナノワイヤを製造するための様々な材料、p型ドーピングナノワイヤおよびn型ドーピングナノワイヤを含む薄膜、ナノワイヤヘテロ構造、発光ナノワイヤヘテロ構造、ナノワイヤを基板上に配置するためのフローマスク、ナノワイヤを成膜するためのナノワイヤ噴霧技術、ナノワイヤにおける電子のフォノン散乱を減少または除去するための技術、および、ナノワイヤにおける表面準位を減少させるための技術が、説明される。

(もっと読む)

半導体デバイスの製造方法

【課題】犠牲層を介してInP系のデバイスを形成したときに、犠牲層としてAlAs単層を用いたときのデバイス特性よりも良好なデバイス特性を得ることができ、かつ、犠牲層をエッチングする際に、デバイス層もエッチングされてしまう虞のない半導体デバイスの製造方法を提供する。

【解決手段】保護膜35の平坦面35Aに支持基板10を接合もしくは接着したのち、InPと疑似格子整合するInAlAsからなる犠牲層42を、フッ酸を用いて選択的に除去することにより、InP基板41を、InP系のデバイス層21を含む支持基板10から剥離する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの周りで電位変動が発生した場合であっても、該電位変動の影響を受け難く、耐圧等の他の特性と両立できる、安価な半導体装置を提供する。

【解決手段】埋め込み酸化膜12上のSOI層13に、埋め込み酸化膜12に達する絶縁トレンチ17が形成され、該絶縁トレンチ17により取り囲まれたSOI層13からなる第1絶縁分離領域Z1に、バイポーラトランジスタTr1が形成されてなる半導体装置100であって、第1絶縁分離領域Z1を取り囲む絶縁トレンチ17の外側のフィールド領域Fが、バイポーラトランジスタTr1に印加される最高電位Vmaxと同じ電位に設定されてなる半導体装置100とする。

(もっと読む)

半導体装置の製造方法

【課題】非単結晶Si薄膜と単結晶Si薄膜デバイスとを形成し、高性能なシステムを集積化した半導体装置の製造方法を提供する。

【解決手段】絶縁基板2上に、単結晶Si薄膜トランジスタ16aと非単結晶Si薄膜トランジスタ1aとが形成された半導体装置20の製造方法において、表面に酸化膜、ゲートパターン、不純物イオン注入部が形成された後に平坦化されており、所定の深さに所定の濃度の水素イオンが注入された水素イオン注入部15を備えた単結晶Si基板10aを熱処理によって絶縁基板2上に接合し、さらに水素イオン注入部15において熱処理により劈開剥離した後、非晶質Si薄膜5を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ELOにおける配線の高密度化、デバイス特性の向上を図ること。

【解決手段】本発明は、半導体基板10に犠牲層を介して成長させたデバイス層に所定のデバイスおよび接続用パッドを形成する工程と、支持基板20に所定のパターンおよび接続用パッドを形成する工程と、半導体基板10の接続用パッドと支持基板20の接続用パッドとが接続金属を介して導通するよう半導体基板10と支持基板20とを貼り合わせる工程と、半導体基板10と支持基板20とを貼り合わせた状態で犠牲層をエッチングにより除去して半導体基板10とデバイス層とを分離する工程とを備える半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】ELO(エピタキシャルリフトオフ)を用いた半導体装置の製造方法において、短時間で確実に半導体基板と支持基板(デバイス層側)との分離を行うこと。

【解決手段】本発明は、半導体基板1に犠牲層2を介して成長させたデバイス層4に所定のデバイスを形成し、そのデバイス層4側に支持基板10を貼り合わせた状態で犠牲層2をエッチングにより除去して半導体基板1とデバイス層4とを分離する工程を備えた半導体装置の製造方法であり、犠牲層2を除去するにあたり、予めデバイス層4から犠牲層2まで溝dを形成しておき、この溝dを介してエッチング液を犠牲層2まで浸透させる方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子のコレクタ領域でのシート抵抗値を低減させることが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板4上に2層のN型のエピタキシャル層5、6が形成されている。基板4の裏面56からはコレクタ領域として用いられるN型の埋込拡散層21が露出している。そして、基板の裏面56側には、N型の埋込拡散層21とコンタクトする金属層57が形成されている。この構造により、金属層57がコレクタ領域として用いられ、コレクタ領域でのシート抵抗値を大幅に低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子のコレクタ領域でのシート抵抗値を低減させることが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板4上にN型のエピタキシャル層5が形成されている。基板4の裏面54からはコレクタ領域として用いられるN型の埋込拡散層19が露出している。そして、基板の裏面54側には、N型の埋込拡散層19とコンタクトする金属層55が形成されている。この構造により、金属層55がコレクタ領域として用いられ、コレクタ領域でのシート抵抗値を大幅に低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】活性層を劣化させることなく窒素を含むp型III-V 族化合物半導体層を低抵抗化できる半導体装置の製造方法を提供することにある。

【解決手段】サファイア基板1上に、組成が(Alx Ga1-x )y In1-y N(0≦x≦1、0≦y≦1)で表されるp型InGaAlN層2,InGaAlN活性層3及びn型InGaAlN層4を形成する。as-grownの状態では、p型InGaAlN層2中においてMgが水素原子と結合している。次に、窒素雰囲気下で、サファイア基板1の裏面からレーザを照射する。弱いレーザの照射により、p型InGaAlN層2の水素離脱による低抵抗化を行なう。その際、積層部10中のドーパントの拡散を抑制して、ドーパントプロファイルの急峻性を維持することができる。その後、強いレーザの照射によって、サファイア基板1を積層部10から分離させることもできる。

(もっと読む)

半導体デバイスの製造方法、および得られるデバイス

【課題】半導体デバイス、とくには複数のゲートをフィンガー状に備えるHEMTなどの高周波かつ大電力のデバイスであって、公知の空中ブリッジ構造より小型であり、かつ放熱が要求されるデバイスの製造方法の提供。

【解決手段】高電子移動度トランジスタ(HEMT)などの大電力のデバイスの製造に適しており、ソース・コンタクト間の接続が、空中ブリッジ構造によって製造されるのではなく、半導体層を貫いてビアをエッチングし、デバイスの背面に設けられたコンタクト層に直接接続することにより達成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】縦構造のバイポーラトランジスタを用い、コレクタの電極取り出しを基板の裏面側で行うことで、バイポーラトランジスタのデバイス面積を縮小化するとともに高速動作化を可能とする。

【解決手段】バイポーラトランジスタ100とMOS型トランジスタ200とを同一基板10に搭載した半導体集積回路装置1であって、バイポーラトランジスタ100は、エミッタ層120、ベース層110、コレクタ層130が基板10主面に対して垂直方向に配列されたものからなり、ベース層110に接続されるベース取り出し電極111が基板10の主面側に設けられ、エミッタ層120に接続されるエミッタ取り出し電極121が基板10の主面側に設けられ、コレクタ層130に接続されるコレクタ取り出し電極131が基板10の主面とは反対の裏面側に設けられたものである。

(もっと読む)

高出力半導体デバイスのための半導体構造体の作成方法

高出力半導体デバイスのための基材配置物は、SiCウエハの表面上に付着させたSi層を有するSiCウエハを包含する。Si第1層、SiO2中間層およびSi第3層を有するSOI構造体が、そのSi第3層を、SiCウエハ上に付着させたSiに接着して、単一構造体を形成する。SOIのSi第1層およびSiO2中間層を除去して、純粋なSi第3層を残し、この上にさまざまな半導体デバイスを製作することができる。Si第3層および付着Si層を、1種以上の半導体デバイスをSiCウエハ上に製作することができるように基材配置物の一部にわたり除去してもよい一方、他の半導体デバイスを純粋なSi第3層上に対応させてもよい。 (もっと読む)

半導体装置とその製造方法

【課題】半導体装置の製造方法として、縦型バイポーラトランジスタの底部に、形状良く低抵抗層を設ける方法を提供する。

【解決手段】2重SOI基板を用意する工程と、ディープトレンチを形成する工程と、ディープトレンチを埋め込む工程と、開口部54を設ける工程と、空孔部56を設ける工程と、多結晶シリコン層80を堆積する工程と、バイポーラトランジスタを形成する工程とを有している。開口部を設ける工程では、ドライエッチングを行って、バイポーラトランジスタ被形成領域55の、第2埋め込み酸化膜40を露出させる。空孔部を設ける工程では、ウェットエッチングにより、バイポーラトランジスタ被形成領域内の第2埋め込み酸化膜を除去する。多結晶シリコン層を堆積する工程では、上述の工程で形成された、互いに連通している開口部及び空孔部に多結晶シリコン層を堆積する。

(もっと読む)

半導体素子、及びその製造方法

【課題】厚み方向の特定領域に重金属を拡散させた半導体素子及び、その製造方法を提供する。

【解決手段】

N型半導体基板51の一方の主面に、P型半導体領域12を形成する。N型半導体基板51の一方の主面にAu膜を形成し、熱処理によってN型半導体基板51内にAuを拡散させる。N+半導体基板52の一方の主面に、第2N型半導体領域22を形成する。次に、N型半導体基板51の他方の主面と、第2N型半導体領域22とを重ね、熱処理によって固着させる。

(もっと読む)

1 - 15 / 15

[ Back to top ]