Fターム[5H430JJ07]の内容

トランジスタを用いた連続制御型電源 (9,660) | 帰還部全体 (266) | 複数の経路を持つもの (108)

Fターム[5H430JJ07]に分類される特許

1 - 20 / 108

半導体集積回路

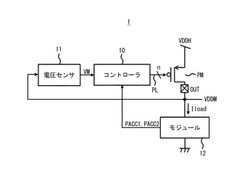

【課題】従来の半導体集積回路のレギュレータ回路では、出力電圧の制御精度を十分に高めることができない問題があった。

【解決手段】本発明の半導体集積回路は、制御端子に与えられるインピーダンス制御信号で示される制御値PLに応じて負荷電流Iloadの大きさに対する出力電圧VDDMの大きさを制御する複数の出力トランジスタPMと、出力電圧VDDMの電圧値を示す出力電圧モニタ値VMを出力する電圧モニタ回路12と、出力電圧VDDMの目標値を示す参照電圧Vrefと、出力電圧モニタ値VMと、の間の誤差値の大きさに応じて制御値PLの大きさを制御し、当該制御値PLにより複数の出力トランジスタPMいずれを導通状態とするかを制御する制御回路10と、を有し、制御回路10が負荷電流Iloadの変更を事前に通知する事前通知信号PACCに応じて、誤差値に対する制御値の変化ステップを一定期間の間大きくする。

(もっと読む)

レギュレータ回路及び電源装置

【課題】従来例に係るレギュレータ回路において、出力電圧を切り替える際に、出力が無負荷もしくは軽負荷である場合に、出力電圧が安定するまでに時間を大幅に短縮する。

【解決手段】出力電圧設定信号に対応した基準電圧を発生して出力する基準電圧回路と、前記基準電圧回路からの基準電圧と、入力される帰還電圧との誤差電圧を増幅して、増幅後の出力電圧を出力端子を介して出力する誤差増幅回路と、前記誤差増幅回路からの出力電圧を所定の帰還率で帰還電圧として出力する帰還回路とを備えたレギュレータ回路において、前記出力端子に接続され、前記出力電圧の切り替え時に発生される強制負荷イネーブル制御信号に応答して、前記出力端子から強制負荷電流を流す強制負荷回路をさらに備えた。

(もっと読む)

定電圧電源回路

【課題】出力トランジスタの電力損失を低減することが可能な定電圧電源回路を提供する。

【解決手段】定電圧電源回路は、電源端子と出力端子との間に接続された第1導電型の第1のトランジスタを備える。定電圧電源回路は、一端が前記出力端子に接続された第1の抵抗と、一端が前記第1の抵抗の他端に接続され、他端が接地に接続された第2の抵抗と、を有し、前記第1の抵抗と前記第2の抵抗との間の分圧電圧を出力する分圧回路を備える。定電圧電源回路は、前記分圧電圧と基準電圧とを比較し、前記分圧電圧と前記基準電圧とが等しくなるように前記第1のトランジスタの制御端子の電圧を制御する出力電圧制御アンプを備える。定電圧電源回路は、前記分圧電圧に応じて、前記第1のトランジスタの制御端子の電圧を制御するフの字特性制御回路と、を備える。

(もっと読む)

電圧発生回路

【課題】外部電源電圧の変動に対してレギュレータの出力電圧の変動を抑制する。

【解決手段】電圧発生回路は、出力端子(出力電圧配線5)を介して、内部電源電圧を内部回路16へ供給する電圧発生回路であって、レギュレータ10、ドライブ素子2、及び、制御回路13を備える。レギュレータ10は、外部電源VDD3(第1電源)と出力端子との間に配置されるドライブ素子1を備え、ドライブ素子1を制御することにより、基準電圧6に基づく電圧を出力端子に供給する。ドライブ素子2は、外部電源VDD3と出力端子との間に配置され、活性状態のときに、外部電源VDD3の電圧を出力端子へ供給する。制御回路13は、外部電源VDD3の電圧が、予め設定する検出電圧値以下である場合に、ドライブ素子1とドライブ素子2とを活性状態に制御し、外部電源VDD3の電圧が検出電圧値を超えると、ドライブ素子2を非活性状態に制御する。

(もっと読む)

ボルテージレギュレータ

【課題】負荷電流に応じて消費電流を変化させる低消費電流の位相補償回路を有するボルテージレギュレータを提供する。

【解決手段】位相補償回路をドレインが誤差増幅回路の出力端子に接続される第一のトランジスタと、ドレインが第一のトランジスタのゲートに接続され、ゲートが抵抗を解して第一のトランジスタのゲートに接続される第二のトランジスタと、誤差増幅回路の出力端子と第一のトランジスタのドレインと第二のトランジスタのドレインに接続されるカレンントミラー回路と、第二のトランジスタのゲートと出力トランジスタのドレインの間に接続される容量を備える。こうすることで、負荷電流に応じて位相補償回路での消費電流を変化させることができ、低消費電流の位相補償回路を有するボルテージレギュレータが実現できる。

(もっと読む)

多入力電源回路

【課題】一の電源から他の電源に切り替えるとき、一の入力端子から他の入力端子へ電流が逆流しない多入力電源回路の提供。

【解決手段】この発明は、入力端子101〜103と出力端子104との間に出力安定化部110、120、130を備えている。出力安定化部110は、MOSトランジスタMNL1と、基準電圧生成回路111と、演算増幅器112と、共通の分圧回路140とを備えている。出力安定化部120は、MOSトランジスタMNL2と、基準電圧生成回路112と、演算増幅器122と、共通の分圧回路140とを備えている。出力安定化部130は、バイポーラトランジスタQ1と、基準電圧生成回路131と、演算増幅器132と、レベルシフト回路135と、共通の分圧回路140とを備えている。

(もっと読む)

ボルテージレギュレータ

【課題】起動時に異常な消費電流が流れることなく、高速な過渡応答を実現できるボルテージレギュレータを提供する。

【解決手段】本発明では、基準電圧を出力する基準電圧回路と、出力トランジスタと、基準電圧と出力トランジスタの出力する電圧を分圧した分圧電圧との差を増幅して出力し、出力トランジスタのゲートを制御する第一の差動増幅回路と、出力トランジスタの出力電流を検出して第一の差動増幅回路へブースト信号を出力するブースト回路と、出力電流をセンスするセンストランジスタと、出力電流を正確にコピーできるように調整する第一トランジスタと、出力端子が前記第一のトランジスタのゲートに接続され、反転入力端子が前記センストランジスタのドレインに接続され、非反転入力端子が出力端子に接続された第二の差動増幅回路とを備える。こうして、起動時に異常な消費電流が流れることなく、高速な過渡応答を実現することが可能となる。

(もっと読む)

電源装置と充放電制御装置とその制御方法

【課題】ダイオードの沿層電圧を超えるための時間をなくし高速な制御切り替えをする電源装置と充放電制御装置とその制御方法とを提供することを目的とする。

【解決手段】負荷に対して定電流動作モードと定電圧動作モードとで充電または放電させる電源装置において、定電流制御部と定電圧制御部との出力側を、抵抗を用いたOR回路により構成する電源装置とする。また、定電流制御部は、定電流制御用誤差アンプと定電流制御用誤差アンプの出力側に接続された定電流制御用出力側抵抗とを備え、定電圧制御部は、定電圧制御用誤差アンプと定電圧制御用誤差アンプの出力側に接続された定電圧制御用出力側抵抗とを備える電源装置とする。

(もっと読む)

電源回路

【課題】電源回路を備える装置の低消費電力化と、電源回路が発生させる出力電圧の安定化とを両立させる。

【解決手段】負荷へ供給するための出力電圧を入力電圧に基づいて発生させる一対のMOSトランジスタで構成された電圧発生部と、入力電圧および出力電圧の電圧値を検出する検出部と、検出された電圧値に応じて電圧発生部の駆動を制御する駆動部とを有する電源回路において、負荷の動作状態に応じて駆動部を制御することにより、一対のMOSトランジスタの不感帯の幅を変化させる制御部を有する。

(もっと読む)

定電圧回路

【課題】シリーズレギュレータ回路の位相余裕を増大させる。

【解決手段】定電圧回路10は、入力電圧VINと負荷Lの間に接続されて負荷Lに出力電圧VOUTを供給する第1トランジスタQ1と、出力電圧VOUTに応じた電圧信号を出力する電圧検出部4と、基準電圧Vrefと電圧信号V1との差に応じた差分電圧を出力する差動部1と、差分電圧を増幅して第1トランジスタQ1へ入力する増幅部3と、差動部1及び増幅部3の少なくともいずか一方の出力へ第1トランジスタQ1の出力電流に応じた電流を負帰還させるフィードバック経路5、6を備える。

(もっと読む)

定電圧回路

【課題】負荷が低消費電力動作状態となったときに自らの消費電流も十分に低減する。

【解決手段】定電圧ユニット25、26のツェナーダイオード29、35の素子サイズおよび定電流回路30、32の出力電流値は、トランジスタ8が必要とするベース電流に対応させて互いに異なっている。スタンバイ動作状態では、スイッチ33、38がオフして定電圧ユニット25が選択的に定電圧動作を行い、通常動作状態では、スイッチ33、38がオンして定電圧ユニット25、26がともに選択されて定電圧動作を行う。

(もっと読む)

ボルテージレギュレータ

【課題】従来のボルテージレギュレータは、小さな占有面積で、低消費電流動作と高速動作を切り替えることが困難であった。

【解決手段】本構成では、第一の差動増幅回路の出力を第二の差動増幅回路に接続し、第二の差動増幅回路が出力トランジスタを制御するようにし、低消費が要求される場合には第一の差動増幅回路を停止させ、高速応答が要求される場合には、第一の差動増幅回路を動作させるようにし、最低限の回路面積で低消費・高速動作を切り替えられるような構成とした。

(もっと読む)

出力装置

【課題】本発明は、出力の過渡応答特性を改善しつつ、消費電流を低減することができる、出力装置の提供を目的とする。

【解決手段】出力電流Ioutを出力する出力トランジスタ11と、出力トランジスタ11の出力電圧Voutのフィードバック電圧Vfbが基準電圧Vrefに一致するように、出力トランジスタ11を駆動する第1の駆動部(16)と、グランドに接続されたキャパシタ18に抵抗17が直列接続されたRC回路と、フィードバック電圧がRC回路の両端に印加されることによって抵抗17の両端に発生する電位差が、出力電圧Voutの低下に伴い大きくなる場合、前記電位差が小さいときに比べて、出力電流Ioutが増加するように、出力トランジスタ11を駆動する第2の駆動部(19,20)とを備える、出力装置。

(もっと読む)

非反転増幅回路及び半導体集積回路と非反転増幅回路の位相補償方法

【課題】位相余裕の出力電流への依存性を抑制し、位相余裕−出力電流特性をフラットにする非反転増幅回路の提供。

【解決手段】非反転入力に入力信号(Vref)を入力する差動増幅部(差動対(NM1、NM2)、定電流源(NM3)、負荷回路(PM1,PM2))と、前記差動増幅部の出力を入力に受け負荷回路20を駆動する出力トランジスタ(PM3)と、前記出力トランジスタの出力を抵抗(Rf、Rs)で分圧した信号が、前記差動増幅部の反転入力に入力され、前記出力トランジスタの入力(ノードN1)と帰還路(ノードN2)の間に直列に挿入された可変抵抗(13)と容量(Cc)を含む位相補償回路と、前記出力トランジスタ(PM3)に流れる出力電流(Iout)を検出するIoutモニタ回路(11)と、Ioutモニタ回路(11)での出力電流の検出結果に応じて、可変抵抗(13)の抵抗値を可変させるバイアス電圧生成回路(12)と、を備える。

(もっと読む)

過電流検知回路、レギュレータ回路および電子機器

【課題】 過電流検知回路の電流検出用の抵抗素子の異常を検知して、レギュレータ回路の出力を停止することができる過電流検知回路、レギュレータ回路および電子機器を提供する。

【解決手段】 オープン検知回路13は、抵抗素子R1の一端と接続端子31がオープンでなく、電源2の電圧が入力されるとき、ローレベルを出力し、トランジスタTr4を遮断状態とし、差動増幅器4によるトランジスタTr1の制御を可能とする。そして、抵抗素子R1の一端と接続端子31がオープンであるとき、ハイレベルを出力して、トランジスタTr4を導通状態とする。トランジスタTr4が導通状態になると、差動増幅器4の出力は強制的にローレベルまで下げられ、トランジスタTr2は遮断状態となり、トランジスタTr1のベース電流がながれなくなり、トランジスタTr1の出力が停止される。

(もっと読む)

電源回路

【課題】消費電流の増加を極力抑えながら電源出力電圧の変動を抑制した電源回路を提供する。

【解決手段】トランジスタT2がオンのとき、電源線2から電流供給回路11、電圧負担回路10、トランジスタT2を通じて電源線3に電流が流れる。このとき、トランジスタT1のベースには、トランジスタT2のコレクタ・エミッタ間飽和電圧と電圧負担回路10の端子間電圧との加算電圧が与えられる。この状態からトランジスタT2がオフすると、トランジスタT1のベースの電圧は加算電圧から上昇を開始する。

(もっと読む)

定電圧回路

【課題】 突入電流のピークを通常動作時用に設定された制限電流よりも低くすることで起動時に周辺回路・装置に悪影響を与える恐れの少ない定電圧回路を提供する。

【解決手段】 パワートランジスタMptに流れる電流をカレントミラー回路13と電流検出回路14で検出し、それが予め設定された値以上になった場合、電流の大きさに応じた電流検出信号Scdを補正回路16に供給する。補正回路16において、パワートランジスタMptに供給される駆動信号Sdrvを電流検出信号Scdの大きさに応じて減少させる。起動時においては、レベル切換回路15が電流検出回路14に電流検出信号Scdのレベルを大きくさせ、補正回路16における駆動信号Sdrvの減少量を通常運転字よりも大きくさせる。

(もっと読む)

電源装置

【課題】さらに、出力電圧のオフセットのばらつきを抑制し、安定した電力供給を行うことが可能な、電源装置を実現する。

【解決手段】電源装置510は、ドレイン端子が、出力回路109に接続されているnトランジスタM103と、ドレイン端子が、nトランジスタM103のドレイン端子に接続されており、ゲート端子が、駆動電圧出力線L101に接続されているnトランジスタM104と、nトランジスタM103のゲート端子と、駆動電圧出力線L101と、の間に設けられたスイッチ103と、を備える。スイッチ103は、nトランジスタM103のゲート端子を、駆動電圧出力線L101に、接続するか否かを、電源装置510の動作状況に応じて切り替える。

(もっと読む)

電源回路及びその動作制御方法

【課題】誤差増幅回路の出力インピーダンスに関係なく、改善可能な入力電圧Vinの変動周波数を任意に設定することができる電源回路及びその動作制御方法を得る。

【解決手段】入力電圧Vinと誤差増幅回路3の反転入力端との間に、コンデンサC1と抵抗R3の直列回路からなるハイパスフィルタを設けたことから、誤差増幅回路3の出力インピーダンスに関係なく、改善可能な入力電圧Vinの変動周波数を任意に設定することができると共に、前記ハイパスフィルタを構成している抵抗とコンデンサの内、該コンデンサの容量を小さくすることができるようにした。

(もっと読む)

リニアレギュレータ回路及び半導体装置

【課題】出力トランジスタの特性に関わらず、PSRRの低下を抑止するレギュレータ回路を提供する。

【解決手段】リニアレギュレータ回路10は、出力トランジスタTr1に流れるトランジスタ電流Itを検出して該出力トランジスタTr1に流れるトランジスタ電流Itに相対した電流検出電圧Vkを出力する電流検出部11と、第1誤差増幅器ERR1の出力端子と出力トランジスタTr1のゲートとの間に、出力トランジスタTr1に流れるトランジスタ電流Itに相対した電流検出電圧Vkと誤差信号Sgとの電圧差に基づく駆動信号Sdを出力トランジスタTr1のゲートに出力して、出力トランジスタTr1に流れるトランジスタ電流Itを誤差信号Sgに相対した電流値にするように動作する第2誤差増幅器ERR2を介在させる。

(もっと読む)

1 - 20 / 108

[ Back to top ]