Fターム[5J055AX02]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | スイッチの基本性能向上 (933) | 高速化 (341)

Fターム[5J055AX02]の下位に属するFターム

主にON時間 (15)

主にOFF時間、蓄積電荷対策 (17)

Fターム[5J055AX02]に分類される特許

1 - 20 / 309

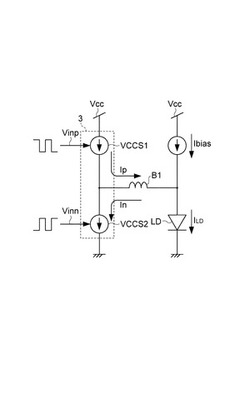

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

エレベーターかご内照明装置およびエレベーターかご内照明方法

【課題】エレベーターが停止してから自動消灯するまでの時間を短くして省エネルギー効果を高めることができるエレベーターかご内照明装置を得る。

【解決手段】交流電源1からの交流電流を整流する全波ブリッジ整流回路21と、全波ブリッジ整流回路21の出力端子間に接続される電解コンデンサ23と、全波ブリッジ整流回路21から直流電流が供給されかご内を照明するLED3と、LED3に供給される直流電流が流れる回路を開閉するMOSFET41と、MOSFET41のオンオフを制御するドライバIC42と、エレベーターが所定の時間連続して停止していることを検出する自動消灯制御リレー51と備え、ドライバIC42は、自動消灯制御リレー51の検出結果に基づいてMOSFET41をオフにしてLED3への直流電流の供給を停止させる。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

(もっと読む)

サンプルアンドホールド回路

【課題】ハイパスフィルタ回路を急速充電できるようにして、その起動時間を短くする。

【解決手段】所定のタイミング毎に入力信号を保持する信号保持回路11と、信号保持回路11の出力側に接続された第1のトランジスタQ1の出力側の第1のノードN1に現れる信号から低域成分を除去するハイパスフィルタ回路12と、起動時にのみ動作してハイパスフィルタ回路12のコンデンサC2に対して急速充電を行う急速充電回路14と、ハイパスフィルタ回路12の出力側に接続された増幅回路13と、急速充電回路14による急速充電動作の終了から通常動作に移行する前後で前記第1のノードN1のバイアス電位をほぼ一定に保持するバイアス制御回路15とを備える。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体スイッチ回路

【課題】簡易な構成によりスイッチ切替時間のさらなる高速化を図る。

【解決手段】外部から供給される外部制御信号に応じて、高周波スイッチ回路101のFET1,2のオン、オフ状態を制御する駆動制御信号を出力する論理制御回路104と、FET1,2が論理制御回路104によりオフ状態からオン状態とされる際にパルス電圧を出力する切替加速回路102,103とは、それぞれの出力信号が共にFET1,2の駆動制御信号として、それぞれへ印加可能に設けられ、論理制御回路104は、定常状態においてFET1,2をオン状態とする電源電圧とほぼ等しい駆動制御信号を出力するよう構成され、切替加速回路102,103は、ピークが電源電圧を超えるパルス電圧を出力する一方、そのパルス電圧が論理制御回路104の出力信号の電圧レベルを下回った際には、その出力が遮断されるよう構成されたものとなっている。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

半導体装置及びそれを備えた半導体リレー装置

【課題】半導体装置及び半導体リレー装置において、製造コストを抑えつつ、CR積の値を小さくする。

【解決手段】双方向スイッチ1を構成する2つのMOSFETのうち、一方のMOSFET2に、化合物半導体で構成されたユニポーラ型化合物半導体装置を用い、他方のMOSFET3に、シリコンで構成されたSi−MOSFETを用いる。ここで、ユニポーラ型化合物半導体装置の中には、Si−MOSFETよりもCR積の値が小さいものが多く存在する。従って、一方のMOSFET2にユニポーラ型化合物半導体装置を用いたことにより、両方のMOSFET2、3にSi−MOSFETを用いた場合に比べて、装置全体のCR積の値を小さくできる蓋然性が高まる。また、Si−MOSFETよりも製造コストの高いユニポーラ型化合物半導体装置を2つ用いた場合に比べて、製造コストを抑えられる。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に互いに離間して配置された第1及び第2の主電極、及び前記第1の主電極と前記第2の主電極間で前記主面上に配置された制御電極を有するスイッチング素子TSWと、コレクタ端子とエミッタ端子と制御端子とを有する第1の駆動素子TD1及び入力端子を含む駆動回路10と、を備え、前記第1の駆動素子の前記コレクタ端子は前記スイッチング素子の前記第1の主電極に接続され、前記第1の駆動素子の前記エミッタ端子は前記スイッチング素子の前記制御電極に接続され、前記第1の駆動素子の前記制御端子は前記入力端子及び前記エミッタ端子に接続される。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮し、オーバドライブによらず速度の向上と電力効率の向上を図り得るスイッチング回路を提供する。

【解決手段】半導体スイッチ素子20a、20dがON(OFF)のとき残りの半導体スイッチ素子がOFF(ON)となるように、各半導体スイッチ素子の入力端子にパルス状信号が印加される。スイッチング回路は、半導体スイッチ素子20bの出力端子と半導体スイッチ素子20dの入力端子の間に接続されるキャパシタンス素子60と、半導体スイッチ素子20bの入力端子と半導体スイッチ素子の出力端子20dの間に接続されるキャパシタンス素子61とを備える。キャパシタンス素子60,61は、半導体スイッチ素子20b、20dの各々の入力端子と出力端子間の寄生容量を、半導体スイッチ素子20b、20dに供給されるパルス状信号のクロック周波数のN倍の周波数において低減する容量を有する。

(もっと読む)

ゲート駆動回路

【課題】 リカバリー電流を低減させつつ、出力MOSトランジスタのスイッチング応答性を高くすることができるゲート駆動回路を提供する。

【解決手段】 制御信号Scdの信号レベルが所定の第1レベルLから第2レベルHへ遷移する第1遷移を契機として出力MOSトランジスタ2のゲートへ充電を開始する第1チャージ回路6と、制御信号Scdの第1遷移または第1期間Tp1の経過を契機として出力MOSトランジスタ2のゲートへの充電を開始する第2チャージ回路7と、制御信号Scdの第1遷移から第1期間Tp1より長い所定の第2期間Tp2経過後に出力MOSトランジスタ2のゲートへ充電を開始する第3チャージ回路8とを備え、第2チャージ回路7の単位時間あたりの充電量は、第1チャージ回路6および第3チャージ回路8の単位時間あたりの充電量より少ない。

(もっと読む)

1 - 20 / 309

[ Back to top ]