Fターム[5J081AA03]の内容

LC分布定数、CR発振器 (9,854) | 発振回路の種類 (659) | 集中定数型 (453) | LC型 (362) | コルピッツ型 (74)

Fターム[5J081AA03]に分類される特許

1 - 20 / 74

発振器

【課題】基本波を逓倍した高次高調波を用いる発振器において、出力レベルと雑音特性を向上させることを目的としている。

【解決手段】基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、基本波の通過を阻止し、基本波の高次高調波を通過させる周波数選択回路と、を備え、周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、並列経路の共振周波数が、基本波の周波数に設定されている。

(もっと読む)

電圧制御発振器

【課題】コルピッツ型発振回路を用いた電圧制御発振器において、可変容量素子の非線形歪みによる位相雑音特性の劣化を抑制することができる技術を提供すること。

【解決手段】2つのバリキャップダイオード12、13が設けられたコルピッツ型発振回路で構成したVCO回路において、共振部1と帰還部2の間にバリキャップダイオード12をそのカソード側で帰還部2と接続するように設けると共に、バリキャップダイオード12のカソードと帰還部2との間に逆電圧印加部3を接続して、バリキャップダイオード12のカソードに制御電圧を印加している。またバリキャップダイオード12のカソードと帰還部2との間にバイパス部4を接続して、インダクタ40のインピーダンスを適切に調整することにより、バリキャップダイオード12のカソードに印加される発振段トランジスタ20のベース交流電圧の振幅を低減し、可変容量素子の非線形歪みを低減することができる。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

発振回路及び発振器

【課題】発振子と発振回路とのインピーダンス整合を容易にとることができる発振回路及び発振器を提供する。

【解決手段】発振回路100が、第1の入力端子4と、第1の出力端子5と、第1の入力端子4に接続される信号調整部10と、第1の入力端子4及び第1の出力端子5に接続される信号形成部20と、を含み、該信号調整部は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有し、第1の素子13は、一方端が第1の入力端子4に接続され、他の一方端が第1の抵抗11の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源2に接続され、第2の抵抗は、他の一方端が第2の電源3に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続され、該信号形成部において、第1の出力端子から出力される信号は、第1の入力端子から入力された信号を基に形成される。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

車両制御システムおよび車載器

【課題】携帯機と車載器との間で無線通信を行うに際し、車載器に使用される振動子の発振周波数の温度ばらつきを軽減する。

【解決手段】受信IC22には車載器20の温度を測定する第2温度センサ27が内蔵されている。そして、補正部23は、携帯機10の第1振動子11および車載器20の第2振動子21の周波数温度特性のデータマップがそれぞれ記憶されており、受信IC22から携帯機10の温度を示す送信側温度情報を入力すると共に第2温度センサ27から車載器20の温度を示す受信側温度情報を入力し、送信側温度情報、受信側温度情報、およびデータマップに基づいて取得したオフセット値を第2振動子21に付加することで、第2振動子21の第2周波数を第1振動子11の第1周波数に近づける補正を行う。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

センサのモニタリング装置

【課題】高温環境下でも正常に動作してセンサの測定値を正確に求めることができるようにする。

【解決手段】本発明のモニタリング装置1は、センサ2と、このセンサ2が接続され且つワイドバンドギャップ半導体を使用した発振器を備えたインタフェース3と、インターフェース3とは別に配置され且つインターフェース3から出力された発振信号を処理する演算装置4とを備えている。発振器は、基準となる発振信号を出力する第1発振器6aと、センサ2の出力に基づいて発振信号を出力する第2発振器6bとから構成されている。第演算装置4は、第1発振器6aからの発振信号と第2発振器6bからの発振信号とに基づいてセンサ2で測定した測定値を算出する演算部15とを備えている。

(もっと読む)

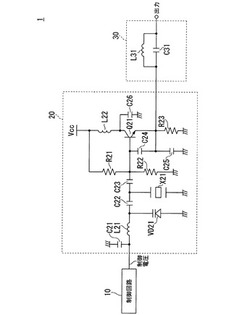

電圧制御発振器

【課題】小型で周波数特性の良好な電圧制御発振器を提供する。

【解決手段】電圧制御発振器(VCO)の共振部1は、共振周波数の調整を行うために静電容量が変化する可変容量素子13、14と、インダクタンス素子11と、を含み、エミッタ接地型のトランジスタ21はこの共振部1からベース端子T1に入力された周波数信号を増幅する。帰還部2は帰還用の容量素子22、23を含み、前記トランジスタ21のエミッタ端子T2から出力された周波数信号を、前記ベース端子T1を介してトランジスタ21に帰還させる。そして前記ベース端子T1に印加されるバイアス電圧を調整するためのベース・ブリーダ抵抗R2、R3及びトランジスタ21が共通の集積回路3内に形成され、トランジスタ21の動作点を調整するためにエミッタ抵抗R1はこの集積回路3外に別体の抵抗素子として設けられる。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

二重正帰還電圧制御発振器

【課題】低供給電圧の性能でのマイクロ波帯域における電圧制御発振器の効率を向上させるための二重正帰還電圧制御発振器を提供する。

【解決手段】2つのコルピッツ回路20、21は第1正帰還ループを提供し、第1負抵抗と等価である。NMOS交差結合ペア回路30は、第2正帰還ループを提供し第2負抵抗と等価である。2つのコルピッツ回路20、21及びNMOS交差結合ペア回路30によって生成される2つの各負抵抗は、LCタンクの寄生抵抗に対して並列に接続されている。この為2つの各負抵抗は、LCタンクの寄生抵抗をオフセットする。2つの各負抵抗が生成されるので、低電圧の稼動時において、及び、直流電流の共有において、高い負抵抗が二重正帰還電圧制御発振器10によって生成される。この為、二重正帰還電圧制御発振器10は、より低い電力下で発振可能である。

(もっと読む)

電圧制御発振器

【課題】コルピッツ回路を用いた電圧制御発振器において、帰還部の2つのコンデンサ間とトランジスタのエミッタとを接続する導電線路におけるインダクタンス成分の影響による出力周波数の可変幅(調整幅)の劣化(低下)を抑えることのできる電圧制御発振器を提供すること。

【解決手段】コルピッツ回路を用いたVCOにおいて、帰還部2のコンデンサ22、23について、トランジスタ21のベースから伸びる端子部8(T1)及び前記トランジスタ21のエミッタから伸びる端子部8(T2)が夫々装着されるベース基板5上のベース用端子(接続部7)とエミッタ用端子とを直結するように第1の帰還容量素子(コンデンサ)22を配置すると共に、上記エミッタ用端子とアース用端子(接地電極51)とを直結するように第2の帰還容量素子(コンデンサ)23を配置する。

(もっと読む)

電圧制御発振器

【課題】マイクロストリップラインのトリミングによってQ値の劣化を招くことなく、各種の周波数帯への調整を可能とする。

【解決手段】電圧制御発振器は、発振用トランジスタのベースに接続された共振回路を有しており、この共振回路には、バラクタダイオードとともにマイクロストリップライン10が設けられている。マイクロストリップライン10は、その一端が制御端子に接続されており、他端がビア7を介してグランド電極に接続されている。またマイクロストリップライン10は、その一端に位置する入力導体部10bから他端に位置する接地導体部10eに至る導電路がスパイラル形状をなしており、導電路の途中が粗調用導電体10aを介してグランドに接続されている。

(もっと読む)

電圧制御発振器

【課題】電源電圧に重畳されたノイズにより発生する発振器の位相雑音を低減することができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ることのできる電圧制御発振器を提供すること。

【解決手段】この電圧制御発振器1は、直流電源端子16にコレクタが接続された発振用トランジスタ11と、発振用トランジスタ11のエミッタ・接地間に接続された第1の抵抗21と、発振用トランジスタ11のベース・接地間に接続された共振回路27と、発振用トランジスタ11のエミッタと第1の抵抗21との接続点と直流電源端子16とを接続する結合ラインL1上に設けられた第1のキャパシタ22とを具備することを特徴とする。

(もっと読む)

低雑音電圧制御発振回路

【課題】 電源雑音を除去し、低周波雑音の特性を良好にできる低雑音電圧制御発振回路を提供する。

【解決手段】 駆動用トランジスタQ1 のベースとGNDの間にコンデンサC11を設けることで、そのベースに入力される低周波ノイズを除去でき、駆動用トランジスタQ1 をhFEの低いトランジスタとすることで、電源から入力される低周波ノイズを除去することができ、発振用トランジスタQ2 のエミッタ側に、コイルL3 を設けることで、周波数特性を広域化して位相雑音の周波数特性を良好にでき、発振用トランジスタQ2 のエミッタ側に、コンデンサC7 とコイルL3 で構成される共振回路における共振周波数をVCOの発振周波数帯域の中心辺りに設定することで、ノイズの影響を受けにくい発振周波数にすることができる低雑音電圧制御発振回路である。

(もっと読む)

電圧制御発振器

【課題】電源ラインなどから入力する外来ノイズの影響を低減できる電圧制御発振器を提供すること。

【解決手段】

発振トランジスタ11のベース・エミッタ間に第1の帰還コンデンサ12を接続し、発振トランジスタ11のエミッタ・コレクタ間に第2の帰還コンデンサ13を接続し、発振トランジスタ11のベース・コレクタ間にインダクタ14を接続してコルピッツ発振回路を構成する。発振トランジスタ11のコレクタと直流電源端子18との間にコレクタバイアス抵抗30を接続し、コンデンサ19を介してコレクタバイアス抵抗30の一端を接地する。発振トランジス11のコレクタとベースとの間にチョークインダクタ31とコンデンサ32とが直列に接続されたフィルタ回路を接続する。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振回路

【課題】振動子の安定発振を早める発振回路に関する技術を提供するとともに、それを用いた超音波流量計を提供する。

【解決手段】共振周波数を有する振動子1と、前記振動子に接続されるアンプ2と、付勢パルス発生手段3と、前記付勢パルス発生手段3と前記振動子1およびアンプ2との接続・非接続とを切替える切替え手段4とを備え、前記振動子1の駆動初期は前記切替え手段4により、前記振動子1と前記付勢パルス発生手段3とを接続するようにした発振回路。

(もっと読む)

電圧制御発振器を用いた方法及び配置

【解決手段】自己注入同期電圧制御発振器の配置(1)では、一組の結合する第1及び第2電圧制御発振器(21,22)がチップ(2)上に配置され、増幅器(23)が同一の反射型チップ(2)上に配置され、オフチップ遅延線路(10)が、前記結合された第1及び第2電圧制御発振器(21,22)の外部端子に接続される一端子であって前記外部端子からの信号を反射するように適合された一端子で配列され、低位相雑音及び小型化を示すVCOの配置(1)を提供するために、増幅器(23)は、前記外部端子からの注入信号を増幅するため及び増幅された注入信号を前記第1及び第2電圧制御発振器(21,22)の一つに供給するために配置される。 (もっと読む)

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

1 - 20 / 74

[ Back to top ]