Fターム[5J500AA17]の内容

Fターム[5J500AA17]の下位に属するFターム

コンプリメンタリ(相補型) (150)

準コンプリメンタリ (37)

SRPP (2)

Fターム[5J500AA17]に分類される特許

1 - 20 / 44

D級増幅器

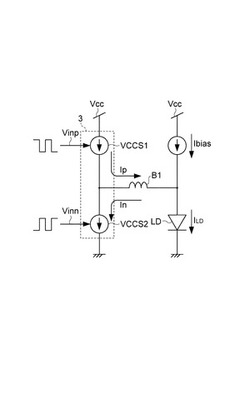

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

オーディオ信号処理回路および電子機器

【課題】アンプに対する電源電圧を好適に制御する。

【解決手段】メインアンプ4は、オーディオ信号S1を増幅する。電源回路2は、アンプの上側電源ラインに正の電源電圧CPVDDを、下側電源ラインに負の電源電圧CPVSSを供給する。電圧検出部32は、アンプにより増幅されたオーディオ信号S2の振幅が所定のしきい値より大きいときアサートされる電圧検出信号S21を生成する。電流検出部34は、メインアンプ4の出力段に流れる負荷電流ILが所定のしきい値電流ITHより大きいときアサートされる電流検出信号S22を生成する。電圧制御部30は、電圧検出信号S21がネゲートされると、電源回路2が生成する正および負の電源電圧の絶対値を低下させる。また電圧検出信号S21がアサートされ、または電流検出信号S22がアサートされると、電源回路2が生成する正および負の電源電圧の絶対値を増大させる。

(もっと読む)

適応型バイアシングを用いた高スイング演算増幅器出力段

【課題】加工コストを増大させず、適応型バイアシング出力段を用いた高スイング演算増幅器を提供する。

【解決手段】出力段123は、VDDAノードと出力ノードとの間のプルアップ電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT3及びバイアシングトランジスタT4)を含み、前記出力ノードと接地ノードとの間のプルダウン電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT1及びバイアシングトランジスタT2)も含む。前記バイアシングトランジスタT4,T2を提供することは、前記トランジスタT3,T4において低下される最大電圧を低減させ、それによって前記トランジスタT1〜T4がVDDAよりも低い破壊電圧を有するのを可能にする。

(もっと読む)

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

増幅回路

【課題】SEPP回路の温度上昇の熱が放熱器を介してバイアス回路に伝わるまでの熱結合によるタイムラグを解消して、熱暴走の発生を未然に防止する。

【解決手段】トランジスタ素子を有して構成されるトランジスタQ1と、トランジスタQ1のトランジスタ素子とは逆極性のトランジスタ素子を有して構成されるトランジスタQ2と、が直列接続されると共に、両端が電源に接続されたシングルエンデッド・プッシュプル回路と、トランジスタQ1回路にバイアス電圧を印加するバイアス回路を構成するトランジスタQ5と、トランジスタQ2にバイアス電圧を印加するバイアス回路を構成するトランジスタQ6と、トランジスタQ1のベース電圧を検出してトランジスタQ5にフィードバックする直列接続の抵抗R3、R4と、トランジスタQ2のベース電圧を検出してトランジスタQ6にフィードバックする直列接続の抵抗R5、R6と、を備えている。

(もっと読む)

パワーアンプ回路と充放電制御装置

【課題】効率をさらに高めて損失を低減することが可能なパワーアンプ回路と充放電制御装置とを提供することを目的とする。

【解決手段】負荷に供給する電圧を制御するパワーアンプ回路において、負荷の状態に対応して正電圧を出力するとともに負荷の他の状態に対応して負電圧を出力する内部電源と、負荷の電圧を検出する負荷電圧検出部とを備え、負荷電圧検出部で検出した負荷電圧に基づいて、負荷に供給する内部電源の出力電圧をフィードバック制御するパワーアンプ回路とする。さらに好ましくは、負荷に供給する電圧を、負荷に流れる電流が一定になるように制御するパワーアンプ回路とする。

(もっと読む)

音響用擬似三極管特性増幅装置および音響用擬似三極管特性プッシュプル増幅装置

【課題】半導体素子を用いた音響用増幅装置において、その特性を三極管アンプの特性に近似させると共に、負荷に供給される出力信号の歪み成分を低減することを目的とする。

【解決手段】入力端子T1は、差動増幅回路12の正相端子に接続されている。差動増幅回路12の逆相端子はトランジスタ10のエミッタ電極に接続され、出力端子はトランジスタ10のベース電極に接続されている。トランジスタ10のコレクタ電極と入力端子T1との間には、入力側抵抗器R2が接続され、入力端子T1と接地導体との間には副入力側抵抗器R3が接続されている。トランジスタ10のエミッタ電極と接地導体との間には出力側抵抗器R1が接続されている。そして、トランジスタ10のコレクタ電極には、負荷端子TLが接続されている。

(もっと読む)

電流電圧変換回路

【課題】回路構成を簡素化した電流電圧変換回路を提供することである。

【解決手段】NPNトランジスタQ1のエミッタとPNPトランジスタQ2のエミッタとが入力端子INに接続される。NPNトランジスタQ1のコレクタが定電源V1ラインに接続され、PNPトランジスタQ2のコレクタが電源C2ラインにされる。NPNトランジスタQ1のベースと、PNPトランジスタQ2のベースとの間に、バイアス回路20が接続され、フローティング状態とされる。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】駆動回路76は、入力電位VIよりも所定電圧高い電位をノードN22に出力するレベルシフト回路61と、ノードN22の電位よりも所定電圧低い電位をノードN30に出力するプルアップ回路30と、入力電位VIよりも所定電圧低い電位をノードN27に出力するレベルシフト回路63と、ノードN27の電位よりも所定電圧高い電位をノードN30に出力するプルダウン回路33と、一方電極がそれぞれ信号φB,/φBを受け、他方電極がそれぞれノードN22,N27に接続されたキャパシタ76,77とを備える。入力電位VIの変化時、信号φB,/φBは、それぞれパルス的に「H」レベルおよび「L」レベルになる。したがって、低消費電流化と応答速度の高速化が図られる。

(もっと読む)

出力回路及び増幅回路

【課題】出力ダイナミックレンジを低下させることなく出力インピーダンスを変化させることができる出力回路及び増幅回路を提供する。

【解決手段】実施形態によれば、可変抵抗回路と、第1のトランジスタと、プッシュプル回路と、を備えたことを特徴とする出力回路が提供される。前記可変抵抗回路は、第1の抵抗と前記第1の抵抗に接続された第1のスイッチ素子とを有する。前記第1のトランジスタは、前記可変抵抗回路と直列的に接続され、前記第1の抵抗の抵抗値よりも出力抵抗の大きい状態にバイアスされる。前記プッシュプル回路は、前記第1のトランジスタにより駆動される。

(もっと読む)

高効率オーディオ増幅器システム

【課題】高効率オーディオ増幅器システムを提供すること。

【解決手段】高効率増幅器システムであって、該高効率増幅器システムは、デューティーサイクルの50%より大きい間に連続的に伝導するように動作可能な少なくとも2つの伝導性デバイスを有する第1出力ステージと、該第1出力ステージと並列に連結される第2出力ステージとを含み、該第2出力ステージが、インターリーブスイッチングによって動作可能なスイッチングモード出力ステージとして動作可能であり、該第1出力ステージおよび第2出力ステージが、負荷を供給するように協働的に動作可能であり、該第1出力ステージが、決定された閾値に従って、該第2出力ステージの動作を選択的に有効にし、そして、無効にするように構成される、高効率増幅器システム。

(もっと読む)

フォールデッドカスコード型の差動アンプ及び半導体装置

【課題】回路を構成する素子数を削減すると共に、差動アンプのオフセットや抵抗の比精度による誤差を低減できるフォールデッドカスコード型の差動アンプ及び半導体装置を提供する。

【解決手段】フォールデッドカスコード型の差動アンプ14の入力段30をHVMOSにより構成し、出力段32をLVMOS20により構成することにより、従来では、2つの差動アンプにより構成していた差動増幅アンプを1つの差動アンプ14により構成することができる。

(もっと読む)

シングルサプライD級アンプ

出力回路

【課題】構成素子数を最小限に抑えて消費電流の増加を抑え、且つ過渡応答時のクロスオーバー歪を改善する。

【解決手段】NチャネルMOSトランジスタM1,M2,M6と、PチャネルMOSトランジスタM3,M4,M5を備える出力回路において、ドレインとゲートがMOSトランジスタM2のドレインおよびトランジスタM5のゲートに接続され、ソースがMOSトランジスタM4のドレインに接続されたMOSトランジスタM7を設けた。

(もっと読む)

差動増幅器およびその制御方法

【課題】高スルーレートの差動増幅器を提供する。

【解決手段】差動増幅器は、差動入力信号を受ける差動対トランジスタ(TN12/TN13、TP12/TP13)と、定電流源(ICS11、ICS12)と、スイッチ(TN11、TP11)とを具備する。定電流源(ICS11、ICS12)は、差動対トランジスタ(TN12/TN13、TP12/TP13)に流れる電流を制御する。スイッチ(TN11、TP11)は、定電流源(ICS11、ICS12)と並列に配置され、差動入力信号の反転動作に同期して差動入力信号の反転動作の遷移時間より短い時間だけ差動対トランジスタTN12/TN13、TP12/TP13)に流れる電流を増加する。

(もっと読む)

バッファ回路

【課題】 消費電力を抑制することができるバッファ回路を提供すること。

【解決手段】 検波回路11が、入力信号IDのレベルに応じた入力レベル判定信号SWを制御回路9へ供給し、入力信号IDの振幅が比較的小さい場合には、制御回路9が、低レベル入力用回路6を選択して、トータルゲインを十分に上げ、入力信号IDの振幅が比較的大きい場合には、制御回路9が、高レベル入力用回路5を選択して、無用な消費電流の増大を抑制する。

(もっと読む)

H級共鳴電気外科手術発電機

【課題】電気外科手術デバイスと共に使用する発電機を提供すること。

【解決手段】第一の電圧レールと第二の電圧レールとの間に電気的に配置された利得ステージと、利得ステージの入力に動作可能に結合された電圧供給源と、増幅器の動作パラメータを感知することと、動作パラメータに対応するセンサ信号を提供することとを行うように構成された少なくとも1つのセンサと、少なくとも1つのセンサ信号を受信することと、その信号に応答して、駆動制御信号を電圧供給源に提供することとを行うように適合されたコントローラと、利得ステージの出力が第一の電圧レールの電圧と第二の電圧レールの電圧との間に入るとき、対応する出力電圧を供給するように構成され、出力電圧が第一の電圧レールの電圧より大きいか、または第二の電圧レールの電圧より小さいときには、ピーク電圧出力を供給するように構成される、増幅器出力とを備えている、発電機。

(もっと読む)

差動増幅器

【課題】非反転入力端子の電圧が変化した場合でも、出力トランジスタに流れる電流を一定にすることができる、差動増幅器を提供する。

【解決手段】非反転入力端子143と、反転入力端子144と、P型MOSトランジスタ107及び108とN型MOSトランジスタ101及び102と定電流源121とからなる差動増幅回路と、P型MOSトランジスタ103及び104とN型MOSトランジスタ113及び114と定電流源122とからなる差動増幅回路と、P型MOSトランジスタ107及び108に電流を流す定電流源124とで構成される相補型フォールデッドカスコード増幅回路に、さらにP型MOSトランジスタ107及び108に電流を流す電流制御回路である、定電流源123とN型MOSトランジスタ105を備え、相補型差動対の負荷であるカスコード増幅回路に流れる電流を、非反転入力端子の電圧によって制御する構成とした。

(もっと読む)

1 - 20 / 44

[ Back to top ]