Fターム[2G132AE08]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | ドライバー、センサー回路 (457)

Fターム[2G132AE08]に分類される特許

1 - 20 / 457

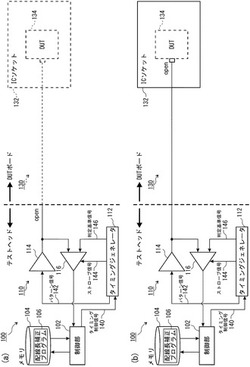

ICテスタ用信号遅延測定プログラムおよびその測定方法

【課題】 TDR測定によって、DUTボードの配線長に依存した信号遅延時間を正確に求めることが可能なICテスタ用信号遅延測定プログラムを提供する。

【解決手段】 本発明にかかるICテスタ用信号遅延測定プログラム106の構成は、コンピュータを、テストヘッド110側からステップ波形148を印加してその入射波と反射波との第1到達時間差Td1、第2到達時間差Td2を測定するTDR測定手段、第1スルーレートS2、第2スルーレートS2を演算するスルーレート演算手段、第1スルーレートS2と第2スルーレートS2とを用いて第2到達時間差Td2を補正し、第1到達時間差Td1を差し引くことで信号遅延時間を演算する信号遅延演算手段、として機能させることを特徴とする。

(もっと読む)

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

移動体通信装置試験システムおよび試験方法

【課題】試験対象に対してシーケンス測定を実行する際に、取得データ量の面で、誤った測定の無駄な測定をしないで済むようにする。

【解決手段】シーケンス測定制御手段35が実行指定された測定シーケンスにしたがう制御を開始する前に、実行指定された測定シーケンスで送受信部21が解析対象として取得する予定のデータ量の合計値を算出するデータ量算出手段40と、算出したデータ量の合計値が受信データメモリ23の所定容量に応じて予め設定した許容値を超えるか否かを判定するデータ量判定手段41とを備え、シーケンス測定制御手段35は、データ量判定手段41により算出したデータ量の合計値が許容値を超えると判定されたとき、その判定結果を表示部61に表示して、ユーザーに通知する。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング調整方法

【課題】複数の被試験デバイスに対して電源供給部から電源の供給を行って試験を行うときに、同時スイッチングノイズの影響を抑制することを目的とする。

【解決手段】本発明の半導体試験装置1は、複数のDUT3に電源を供給するデバイスパワーサプライ5を備える半導体試験装置1であって、DUT3の試験を行うピンエレクトロニクスカード2のドライバ12およびコンパレータ13とDUT3との間の伝送経路15の伝播遅延Tpdを校正するデータをタイミング校正データとして記憶するタイミング校正データ記憶部21と、DUT3を複数のグループに分割して、当該グループごとに異なる遅延量をタイミング校正データに加算する遅延量加算部25と、を備えたことを特徴としている。

(もっと読む)

任意波形発生装置のインターリーブ・チャンネル校正方法

【課題】任意波形発生装置の校正方法を改善する。

【解決手段】Sパラメータを用いて任意波形発生装置を校正する。任意波形発生装置が有するチャンネルとしては、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルでも良い。差動信号を生成する場合でも良く、2チャンネルを1対として、複数のチャンネル対を校正できる。このとき、各チャンネルは、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルで1つのチャンネルを構成する場合でも良い。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】外部端子数の増加を抑えつつ、半導体集積回路のテスト時間を短縮する。

【解決手段】テスト回路は、入力されるリファレンスクロック109を逓倍して、テスト対象回路106をテスト動作させるための実動作クロック112及びサンプリングクロック105を生成するPLL108と、入力されるテストコマンドに従い、テスタ同期クロック103に同期してテスト対象回路106のテスト結果を出力するテスト結果出力回路107と、を備えるテスト回路であって、テストコマンドを含むテスト入力信号104とサンプリングクロック105とに基づきテスタ同期クロック103を生成するテスタ同期クロック生成回路100を備えるものである。

(もっと読む)

任意波形発生装置のチャンネル校正方法

【課題】任意波形発生装置の校正方法を改善する。

【解決手段】Sパラメータを用いて任意波形発生装置を校正する。任意波形発生装置が有するチャンネルとしては、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルでも良い。差動信号を生成する場合でも良く、2チャンネルを1対として、複数のチャンネル対を校正できる。このとき、各チャンネルは、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルで1つのチャンネルを構成する場合でも良い。

(もっと読む)

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

書込回路、半導体集積回路、及び書込方法

【課題】アンチヒューズ型のOTPメモリへの書き込み時間を短縮化すること。

【解決手段】書込回路は、OTPマクロに対して書き込むデータを記憶する記憶部と、前記書き込むデータの書き込みを前記OTPマクロに実行させる第一の信号を印加し、前記OTPマクロが記憶しているデータの読み出しを前記OTPマクロに実行させる第二の信号を印加する制御部と、前記第二の信号に応じて前記OTPマクロから読み出されたデータと、前記記憶部が記憶するデータとを比較し、比較結果を出力する比較部とを有し、前記制御部は、前記比較結果が一致を示す場合、前記書き込むデータに関する処理を終了し、前記比較結果が不一致を示す場合、前記第一の信号及び前記第二の信号の印加を再度行う。

(もっと読む)

直流電流電圧源および半導体試験装置

【課題】直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【解決手段】本発明の直流電流電圧源3は、出力設定部11により設定された設定電圧Vsetを出力する出力アンプ12と、出力アンプ12が出力する出力電圧V1と出力アンプ12に帰還されて入力される入力電圧V2とを入力して、出力アンプ12の消費電力Pampを演算する演算部19と、演算部19により演算された消費電力Pampが予め設定された設定電力Plimを超過しているか否かを比較する比較部20と、消費電力Pampが設定電力Plimを超過しているときには、出力設定部11の設定値を低下させる制御を行う制御部21と、を備えている。

(もっと読む)

半導体試験装置における電気長測定方法

【課題】ウェハを対象とした半導体試験装置において、簡易にプローブ先端を接地状態として電気長測定を行なえるようにする。

【解決手段】試験対象のウェハと接触するプローブを複数備えた半導体試験装置における、プローブを一端とする信号経路の電気長測定方法であって、電気伝導性領域を有するキャリブレーションウェハの電気伝導性領域を全プローブに接触させ、信号経路の他端から測定信号を入力し、電気伝導性領域との接触部で反射した信号波形を他端側で測定することにより電気長を算出する。

(もっと読む)

スイッチ装置、伝送路切替装置、および試験装置

【課題】長寿命化した圧電式アクチュエータを備えるスイッチ装置。

【解決手段】第1接点が設けられた基体と、第2接点を移動させて第1接点と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層と、支持層の上面に形成される第1圧電膜と、支持層を介して第1圧電膜に対向して、支持層の第1圧電膜が形成される面とは反対側の面に設けられ、駆動電圧に応じて伸縮してアクチュエータのそり量を変化させる第2圧電膜と、第1圧電膜および第2圧電膜のそれぞれの上面と下面とに、それぞれの駆動電圧を印加する電極層と、第2圧電膜と第2圧電膜の支持層側とは反対側の電極層との間に形成された導電性酸化物を含む第2導電性酸化物膜と、を有するスイッチ装置を提供する。

(もっと読む)

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

試験装置および試験方法

【課題】正確なタイミングでサンプリングしたデータ値を期待値と比較する。

【解決手段】データ信号とデータ信号をサンプルするタイミングを示すクロック信号とを出力する被試験デバイスを試験する試験装置であって、データ信号をバッファリングするバッファ部と、当該試験装置の試験周期毎に、制御信号およびデータ信号の期待値を発生するパターン発生部と、試験周期毎に、制御信号がバッファ部からのデータの読出しを指示することを条件として、バッファ部からデータ信号を読み出す読出制御部と、読出制御部により読み出されたデータ信号とパターン発生部から発生された期待値とを比較する判定部とを備える試験装置を提供する。

(もっと読む)

試験装置

【課題】高速多値信号を試験可能な試験装置を提供する。

【解決手段】パターン発生器PGは、I/O端子PIOに入力される被試験信号S1と比較すべきしきい値電圧Vthを指定する制御データS11を発生するとともに、被試験信号S1としきい値電圧Vthの比較結果の期待値を示す期待値データEXP2を発生する。しきい値電圧発生器10は、制御データS11に応じた電圧レベルを有するしきい値電圧Vthを、第1タイミング信号St1が指定する設定タイミングtVごとに生成する。レベルコンパレータCpは、被試験信号S1の電圧レベルをそれと対応するしきい値電圧Vthと比較する。タイミングコンパレータTCは、レベルコンパレータCpの出力S3を、第2タイミング信号St2が指定するストローブタイミングでラッチし、比較信号S4を生成する。タイミング調節部50は第1タイミング信号St1の位相を調節する。

(もっと読む)

試験装置および試験方法

【課題】精度良く被試験デバイスを試験する。

【解決手段】データ信号とクロック信号とを授受する被試験デバイスを試験する試験装置であって、被試験デバイスにデータ信号およびクロック信号を試験信号として供給する試験信号供給部と、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、調整時において、データ信号を取得するタイミングを生成するためのクロック信号の遅延量を調整する調整部とを備える試験装置を提供する。

(もっと読む)

スイッチ装置、伝送路切り替え装置、製造方法、および試験装置

【課題】剛性を高めつつ、物理的な破壊を防いだアクチュエータを提供する。

【解決手段】スイッチ装置は、第1接点122が設けられた基体110と、第2接点134を移動させて第1接点122と接触または離間させるアクチュエータと、を備え、アクチュエータは、支持層150と、支持層150上に形成され、第1駆動電圧に応じて伸縮する第1圧電膜136と、第1圧電膜136上に絶縁材料で形成され、第1圧電膜136の端部の少なくとも一部において支持層150と接して端部を覆う第1保護膜152と、を有する。

(もっと読む)

スイッチ装置および試験装置

【課題】圧電膜の変位を大きくして動作させるスイッチ装置を提供する。

【解決手段】スイッチ装置100は、第1接点122が設けられた接点部120と、第2接点134を有し、第2接点134を移動させて第1接点122と接触または離間させるアクチュエータと、第1駆動電圧を制御する制御部200と、を備え、アクチュエータは、第1駆動電圧に応じて伸縮する第1圧電膜136と、第1圧電膜136上に設けられる支持層と150、を有し、制御部200は、第1圧電膜136に第1の抗電界以下の電界を印加する電圧から、第1圧電膜136に第1の抗電界以上の電界を印加する電圧まで変化させて第1圧電膜136を縮ませ、第1圧電膜136に第2の抗電界未満の電界を印加する電圧を出力して第1圧電膜136を伸ばす。

(もっと読む)

半導体試験装置

【課題】従来のタイミング発生器を用いて、異なるタイミングで動作可能なピン数を増加させる。

【解決手段】パタン信号とエッジ信号とに基づいてドライバ波形を整形する複数個の波形整形器と、指定されたタイミングでエッジ信号を各波形整形器に出力するドライバタイミング発生器と、ドライバタイミング発生器にエッジ信号の出力タイミングを指示するとともに、複数個の波形整形器に独立にパタン信号を出力するフォーマッタとを備えた半導体試験装置。

(もっと読む)

半導体テスト装置および半導体装置の製造方法

【課題】半導体装置のテスト用電源電圧として、複雑なパターンの電源波形を短時間で、高精度に生成する。

【解決手段】マルチプレクサ16から出力された電圧変化値ΔVは加算器17により電圧設定値保持部19に格納された電圧値が加算される。この加算結果は電圧設定値保持部19に格納される。加算回路20は加算器17の加算結果に、電圧初期値格納部18の初期値データを加算する。この加算結果は、補正器21が補正情報に基づいて補正する。制御回路26は比較器24の比較結果に基づいて補正器21のデジタルデータが上限/下限電圧になったかを判定し、到達していない場合、補正器21の信号を時間情報格納部25のデータ転送時間間隔ΔTに基づいて出力する。D/A変換器12は、その信号をアナログ信号に変換し、デバイス供給電源アナログ回路13に増幅されて電源電圧VCCとして出力される。

(もっと読む)

1 - 20 / 457

[ Back to top ]