Fターム[2G132AG09]の内容

電子回路の試験 (32,879) | 信号の印加に関するもの (2,293) | 強制的な信号の印加 (40)

Fターム[2G132AG09]に分類される特許

1 - 20 / 40

擬似障害発生方法と装置

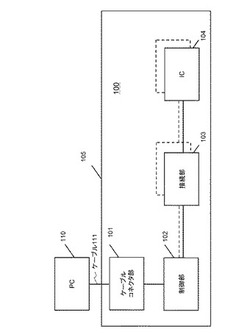

【課題】電子回路装置に対する擬似障害発生を容易化し、試験・評価等の作業を効率化する装置、方法の提供。

【解決手段】

電子回路装置(100)を構成する回路基板(105)上のIC(104)のON/OFF端子に接続部103を介して接続する制御部102が、ケーブルコネクタ部(101)を介してPC(110)の制御により、IC(104)のON/OFF端子に動作中の第1の値とは異なる第2の値を設定することで擬似障害を発生させる。

(もっと読む)

高電圧検査装置

【課題】検査対象の複数個のデバイスに対して一括して、規格に適合した電流波形(または電圧波形)で明確かつ正確に高電圧印加試験を行うことにより、高電圧検査を大幅に効率よく行う。

【解決手段】ESD試験装置1は、所定の高電圧を出力する高電圧電源2と、高電圧電源2からの所定の高電圧を蓄積する高電圧容量手段としての高圧コンデンサ4と、高圧コンデンサ4からの所定の高電圧を印加抵抗5を通して出力する高電圧出力部と、この高電圧電源2からの所定の高電圧を高圧コンデンサ4側に接続するかまたは高圧コンデンサ4からの所定の高電圧を高電圧出力部側に接続するように切り替える切替手段としての高耐圧リレー3とを有し、同一回路構成として、高圧コンデンサ4から高耐圧リレー3さらに印加抵抗5を通して高電圧出力部に至る回路を独立に、一括印加処理すべき複数の検査対象デバイス6の個数分だけ並列に有している。

(もっと読む)

高電圧検査装置

【課題】検査対象の複数個のデバイスに対して一括して、規格に適合した電流波形(または電圧波形)で明確かつ正確に高電圧印加試験を行う場合にも、簡単な構成でショート不良が混在することなく、高電圧検査を大幅に効率よく行う。

【解決手段】ESD試験装置1は、所定の高電圧を出力する高電圧電源2と、高電圧電源2からの所定の高電圧を蓄積する高電圧容量手段としての高圧コンデンサ4と、高圧コンデンサ4からの所定の高電圧を印加抵抗5を通して出力する高電圧出力部と、この高電圧電源2からの所定の高電圧を高圧コンデンサ4側に接続するかまたは高圧コンデンサ4からの所定の高電圧を高電圧出力部側に接続するように切り替える切替手段としての高耐圧リレー3とを有する。

(もっと読む)

半導体試験装置

【課題】格別の操作を要することなく最適な電圧供給を行い、無駄な電力消費や負荷の削減を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT2の試験を行う出力制御ユニット5を備える半導体試験装置1であって、試験を行うためのテストプログラムに設定された設定電圧の情報に基づいて動作を行う複数のドライバ32と、設定電圧の情報を取得して、取得した情報に基づいてドライバ32に設定される設定電圧の電圧をドライバ32に供給する供給電圧を変更可能な1または複数の可変電源33と、を備えている。これにより、DUT2が無駄な電力を消費することなく、負荷が与えられなくなる。且つ、テストプログラムの設定電圧の情報を利用しているため、電源制御の操作を要することなく、最適な電圧を供給することができる。

(もっと読む)

信号出力装置およびこれを用いた半導体試験装置

【課題】消費電力を低減させると共に小型化およびコスト低減が可能な信号出力装置およびこれを用いた半導体試験装置を実現する。

【解決手段】信号出力装置において、ドライバから出力される出力信号のハイレベル側の設定電圧を生成する第1のD/A変換器と、ハイレベル側の設定電圧に正側バイアス電圧を加算した正側電源電圧を前記ドライバの正側電源端子に供給する正側電源供給部と、ドライバから出力される出力信号のローレベル側の設定電圧を生成する第2のD/A変換器と、ローレベル側の設定電圧から負側バイアス電圧を減算した負側電源電圧を前記ドライバの負側電源端子に供給する負側電源供給部と、第1のD/A変換器へハイレベル側の設定電圧の設定、正側電源供給部へ正側電源電圧の設定、第2のD/A変換器へローレベル側の設定電圧の設定、および、負側電源供給部へ負側電源電圧の設定をそれぞれ行う制御部とを備える。

(もっと読む)

半導体試験装置

【課題】電圧印加電流測定時において、測定手法を変更することなく、従来の測定に加えて、1つのDCモジュールでの連続的な電流波形も測定することが可能な半導体試験装置を実現する。

【解決手段】被試験対象デバイスに電源電圧を供給すると共に被試験対象デバイスに流れる電流に応じた変換信号を出力するDCモジュールを複数有し、各DCモジュールからの変換信号をマルチプレクサを切り替えて選択し、選択した変換信号をA/D変換器に与え、このA/D変換器を用いて電流を測定する半導体試験装置において、複数のDCモジュールからの変換信号がそれぞれ入力され、複数のDCモジュールのうちいずれか1つのDCモジュールからの変換信号を全ての出力端子に分配して出力する接続状態、または、複数のDCモジュールからのそれぞれの変換信号を各出力端子からそれぞれ出力する接続状態をとるスイッチ部を備える。

(もっと読む)

ノイズ注入装置

【課題】任意の周波数のノイズ信号を簡単にノイズ注入対象の部品に注入することができるノイズ注入装置を得ることを目的とする。

【解決手段】ノイズ注入用コネクタ11側と可変容量部材14側とのインピーダンスの整合を図るマッチング回路13と、一端がマッチング回路13の出力側と接続されており、ノイズ信号源2から発生されたノイズ信号の周波数に応じた容量に切り換えられる可変容量部材14とを設け、ノイズ注入対象の部品の電源端子に注入するノイズ信号の周波数帯域を切り換えるようにする。

(もっと読む)

電源装置及び半導体試験装置

【課題】回路規模及びコストの増大を極力抑えることができる電源装置、及び当該電源装置を備えることによりコストの低減を図ることができる半導体試験装置を提供する。

【解決手段】電源装置1は、直流電圧を供給すべきDUT40の接地ピンP2に現れる電圧を測定するセンスアンプ20と、センスアンプ20で測定される電圧を基準としてDUT40に対して所定の直流電圧を供給するデバイス電源部10と、センスアンプ20の反転入力端に接続されて、センスアンプ20で測定される電圧に重畳されるべき交流信号を出力する交流信号源30とを備える。

(もっと読む)

半導体集積回路装置およびその検査方法、半導体ウエハ、およびバーンイン検査装置

【課題】正常なバーンイン検査を行うとともに、検査時の無駄な電力を削減できる検査方法、およびこれに用いられる半導体集積回路を提供する。

【解決手段】ウエハに対しウエハ試験を行ない、ウエハ試験後、良品には端子以外のチップ表面に保護膜を付加する。不良品には、端子も含むチップ表面全体に保護膜を付加し、その状態でバーンイン検査を行い、バーンイン投入前に判明した不良品チップへの電源供給、信号印加を遮断する。また、チップの良品判定を行うために自己検査回路を内蔵し、不良チップと判定された場合は、チップ内部動作を停止する機能をチップ内部に設けたり、あるいは、判定信号をバーイン検査装置に送信し、バーンイン検査装置から電源供給、信号印加を停止することでバーンイン投入後に判明した不良チップへの電源供給、信号印加を遮断できる。

(もっと読む)

試験装置及び試験方法

【課題】本発明は、試験装置及び試験方法に関し、例えば集積回路の試験装置に適用して、テストパターン等を印加している端子に対して別電源により高電圧を印加する場合に、安全に高電圧を印加することができるようにする。

【解決手段】本発明は、直流電圧V1を低下させた状態で試験対象2のピン7に直流電圧V1を印加した後、動作試験用の出力信号S1の印加を中止し、その後、直流電圧V11を耐久試験用の電圧に立ち上げる。

(もっと読む)

半導体評価装置

【課題】 半導体のグランド端子から高周波ノイズを注入した場合の半導体装置のイミュニティ評価を行うことができる半導体評価装置を実現する。

【解決手段】 LSI10のグランド端子12はインダクタLを介して接地されているため、高周波ノイズ発生器2から発生した高周波ノイズの交流成分をグランド端子12に注入することができる。従って、グランド端子12から高周波ノイズを注入した場合のLSI10のイミュニティ評価を行うことができる。また、電路14には、インダクタLの一端が電気的に接続されており、インダクタLの他端が接地されてなるため、グランド端子12に注入された高周波ノイズがグランド端子12から流出するおそれがない。従って、LSI10のグランド端子12に高周波ノイズを定量かつ安定に注入することができるため、LSI10のイミュニティ評価を高精度に行うことができる。

(もっと読む)

クランプ試験装置およびクランプ試験方法

【課題】デジタル処理装置の所定部位を通る信号をクランプするクランプ試験装置に関し,クランプ対象となる信号の電圧レベルを確実にスレッシュホールド未満にクランプすることが可能となる技術を提供する。

【解決手段】マイナス電圧生成部11は,クランプ対象の信号の電圧レベルをクランプするために必要となるマイナス電圧を,コンデンサに電荷を蓄積することにより発生させる。リレースイッチ制御部12は,コンデンサの充電と充電されたコンデンサによるクランプ実行とを切り換えるリレースイッチの接続/切断等の制御を行う。遅延回路部13は,マイナス電圧生成部11でのリレースイッチの動作が完了する時間分遅延して,ゲート条件をクランプ実行トリガ生成部14に送る。クランプ実行トリガ生成部14は,クランプ対象となる信号にマイナス電圧を印加するタイミングを制御する。

(もっと読む)

ジッタ増幅回路、信号発生回路、半導体チップ、及び試験装置

【課題】入力信号に含まれるジッタを増幅するジッタ増幅回路150。

【解決手段】入力信号に含まれるジッタを増幅するジッタ増幅回路であって、入力信号を受け取り、入力信号の波形を歪ませることにより、入力信号の高調波成分を生じさせる歪回路と、歪回路が出力する歪信号を、ジッタを増幅すべき増幅率に応じた次数の高調波成分以外の成分を除去して通過させるフィルタとを備えるジッタ増幅回路。

(もっと読む)

耐性評価装置

【課題】静電気ノイズに対する半導体素子単体の誤動作電圧を実測する耐性評価装置を得る。

【解決手段】半導体素子7の動作電圧を供給する直流電源発生部4と、所定方向に静電気ノイズを放射する静電ガン1と、動作電圧に静電気ノイズを重畳させ半導体素子7に印加させるバイアスティ3と、半導体素子7に印加される電圧に応じて出力される論理レベル電圧値を測定する電圧計6と、論理レベル電圧値の論理が反転した時点における半導体素子7に印加される静電気ノイズの電圧測定をおこなうオシロスコープ5とを備え、静電ガン1とバイアスティ3との間に挿入され、静電ガン1から放射される静電気ノイズの一部を分岐してバイアスティ3に供給する分岐回路2と、静電ガン1を覆い、静電ガン1から放射された静電気ノイズのうち、分岐回路2に入射されないものが外部に漏れることを防止する遮蔽部8とをさらに備える。

(もっと読む)

試験信号に振幅ノイズを加える方法及び信号生成装置

【課題】選択されたセグメントに振幅ノイズのある試験信号を生成する。

【解決手段】ユーザ・インターフェイスを用いて試験信号のセグメントとこれに係るパワー・レベルを選択し、この試験信号セグメントに選択されたパワー・レベルで振幅ノイズを適用するようにする。信号処理ユニットは、選択されたセグメントの選択されたパワー・レベルを試験信号とともにコンパイルして、選択されたセグメントに振幅ノイズを有する試験信号を表すデジタル・データを生成する。波形生成ブロックは、このデジタル・データを受けて、試験信号の選択されたセグメントに振幅ノイズのある試験信号出力を生成する。

(もっと読む)

半導体集積回路、液晶表示装置、および半導体集積回路の検査方法

【課題】高い精度で異物の混入が検知可能であり、短時間でのストレス試験が可能な半導体集積回路、および半導体集積回路の検査方法を実現する。

【解決手段】本発明の半導体集積回路の検査方法では、半導体集積回路内の信号配線L3・L4に並走するように設けられたダミー配線LDにストレス電圧を印加するストレス試験と、信号配線L3・L4とダミー配線LDとの間のリーク電流を測定することにより半導体集積回路の良否を判定するテスト工程とを含む。さらに、ダミー配線LDは、電位差を設けることができない非反転側信号配線L1と反転側信号配線L2との間に設けられる。ダミー配線LDは、半導体集積回路内の他の信号配線と電気的に独立しているため、高いストレス電圧を印加することができる。これにより、異物と信号配線との間の絶縁膜等をより確実に破壊でき、テスト工程における異物の検出精度を向上させることができる。

(もっと読む)

信号発生回路、ジッタ印加回路、半導体チップ、及び試験装置

【課題】ジッタが印加された出力信号を生成する信号発生回路200。

【解決手段】ジッタが印加された出力信号を生成する信号発生回路であって、周波数の異なる第1ジッタ信号及び第2ジッタ信号を出力するジッタ出力部と、第1ジッタ信号及び第2ジッタ信号の略中間の周波数のキャリア信号を出力するキャリア出力部と、第1ジッタ信号、第2ジッタ信号、及びキャリア信号を加算して、出力信号を生成する加算部とを備える信号発生回路。

(もっと読む)

診断装置、診断方法、その診断方法をコンピュータに実行させることが可能なプログラム、及びそのプログラムを記録した記録媒体

【課題】 診断の分解能をさらに向上させて良好な診断結果を得ることが可能な診断装置等を提供する。

【解決手段】 診断装置1は記号挿入部3を備え、記号挿入部3は能動素子用記号挿入部5と受動素子用記号挿入部7を有する。診断装置1は発生確率付与部9と等価発生確率付与部11と切替部13を備える。診断装置1によるパーテストX故障診断フローは故障情報の収集ステージと診断の結論を出すステージで構成される。受動素子用記号挿入部7により、ディープサブミクロンLSI回路のレイアウトがしばしば多層配線を必要とし、広範囲で使用されるビアの情報が利用されるのでビアレベルでの欠陥個所を示すことが可能になり診断の分解能が大幅に向上する。発生確率付与部9により、新しい診断値を使用し、とりうる可能性のある故障の論理的組合せの発生確率を考慮するのでディープサブミクロンLSI回路の実動作がより良く反映され、診断の分解能の向上に役立つ。

(もっと読む)

静電耐圧評価装置および静電耐圧評価方法

【課題】半導体装置の故障状況をより良く再現し、半導体装置の静電破壊に対する耐量を評価する。

【解決手段】ソースドライバ120の入力端子または出力端子に接続可能となっており、ソースドライバ120に電荷を付与する第1接続部15と、第1接続部15が接続された端子とは異なる端子に接続可能、かつ、接続した端子を接地可能とする第2接続部16とを備え、パルス性の電荷を付与する印加装置10と、ソースドライバ120の複数の出力端子に接続可能となっており、かつ、これら複数の出力端子を電気的に1つにまとめる共通接続部51とを備えており、ソースドライバ120の出力端子には、共通接続部51を介して第1接続部15または第2接続部16を接続するようになっている。

(もっと読む)

半導体試験装置

【課題】DUTへの伝送ラインの特性によるタイミングエラーを防止することができる半導体試験装置を提供する。

【解決手段】半導体試験装置は、その調整用DAコンバータ15、16によりドライバ2がDUT4に入力するハイレベル、ローレベルの信号を、それぞれ調整用ハイレベル、調整用ローレベルに設定する。伝送ライン9の特性により立ち上がり、立ち下がりの時間が長くなった場合でも、波形の立ち上がり、立ち下がりの勾配は互いに同一となる。実際の波形は調整用ハイレベルVIHH、調整用ローレベルVILLまで到達せずに、最小パルス幅の間にそれぞれハイレベルVIH、ローレベルVILに到達し、そこから折り返していくので、伝送ライン9の特性の影響を受けない場合とほぼ同一の波形が得られる。

(もっと読む)

1 - 20 / 40

[ Back to top ]