Fターム[2G132AG11]の内容

電子回路の試験 (32,879) | 信号の印加に関するもの (2,293) | 試験用データの作成 (324)

Fターム[2G132AG11]の下位に属するFターム

スキャン用検査パターンの作成 (70)

エディタ、表示回路を利用して作成 (12)

シミュレーション技術を用いるもの (115)

Fターム[2G132AG11]に分類される特許

1 - 20 / 127

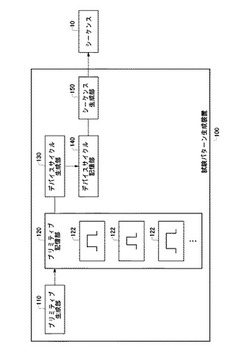

試験パターン生成装置、試験プログラム生成装置、生成方法、プログラム、および試験装置

【課題】試験装置のハードウェア仕様および試験装置用のプログラム言語に詳しくないユーザでも、試験パターンを容易に作成させる装置を提供する。

【解決手段】複数の端子を有する被試験デバイスとの間で通信する試験パターンを生成する試験パターン生成装置であって、基本サイクル中に複数の端子のそれぞれとの間で通信する信号パターンを示すサイクルプリミティブをユーザの指示に基づき生成するプリミティブ生成部と、ユーザの指示に基づき複数のサイクルプリミティブを配列して、複数の基本サイクル分の信号パターンを示すデバイスサイクルを生成するデバイスサイクル生成部と、ユーザの指示に基づき複数のデバイスサイクルを配列して、被試験デバイスに供給する試験パターンのシーケンスを生成するシーケンス生成部と、を備える試験パターン生成装置を提供する。

(もっと読む)

半導体メモリ装置および半導体システム

【課題】PVT変動によってスキューが発生しても、不良に関する情報を適切に格納できるようにした半導体メモリ装置を提供する。

【解決手段】書き込み動作のために書き込みコマンドおよびデータを印加し、読み出し動作のために読み出しコマンドを印加し、前記読み出し動作によって出力データが入力されるテスト回路と、前記書き込みコマンドに応答して前記データをメモリセルに格納し、前記読み出しコマンドに応答して不良に関する情報を含む情報データを内部的に格納するが、前記情報データの格納は、前記情報データのレベルが遷移する場合に発生するパルスに同期して行われる。

(もっと読む)

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

テストデータ生成装置および方法

【課題】各種テスタに共通なテストデータから、個々のテスタの制約に合致したテストデータを自動的に生成することのできるテストデータ生成装置および方法を提供する。

【解決手段】実施形態のテストデータ生成装置1は、タイミング記述検証部11が、共通テストデータ100に記述された1サイクル当たりのタイミングエッジ数が指定されたテスタの制約範囲内かを検証し、タイミングエッジ数が前記制約を超えている場合は、サイクライズ期間設定部12が、タイミングエッジ数および1サイクルの期間がテスタの制約範囲内となるサイクライズ期間を設定し、イベントデータ展開部13が、テストデータ100をイベントデータに展開し、サイクライズ処理部14が、そのイベントデータをサイクライズ期間でサイクライズし、テストデータ出力部15が、サイクライズ後のイベントデータを元の記述形式へ逆変換し、修正版共通テストデータ200を出力する。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法、および、プログラム

【課題】半導体集積回路において、スキャンテスト時における消費電力を削減する。

【解決手段】半導体集積回路設計装置は、第1のスキャンFFのデータ入力端子に接続された第1のロジックコーンの入力端子数である第1の入力端子数と、第1のロジックコーンにデータを設定する第2のスキャンFFのデータ入力端子に接続された第2のロジックコーンの入力端子数である第2の入力端子数とを比較するデザイン解析部と、複数のスキャンFFのそれぞれのデータ入力端子に接続されたロジックコーンの入力端子数、および、複数のスキャンFFのそれぞれを第1のスキャンFFとした場合の前記比較結果に応じて、複数のスキャンFFを複数のグループに分類し、複数のグループのそれぞれに含まれるスキャンFFを相互に接続したスキャンチェーンを複数のグループのそれぞれについて生成するスキャンチェーン構築部と、を備える。

(もっと読む)

テストパターン生成装置,テストパターン生成方法およびテストパターン生成プログラム

【課題】並列処理に起因するテストパターンの増加を抑止する。

【解決手段】第2の演算処理装置20は、複数の第1の演算処理装置10が要求値の設定対象となる同じ回路素子に対してそれぞれ異なる要求値を設定するコンフリクトが発生するか否かを要求値バッファ22aに格納された要求値に基づいて判定する。そして、第1の演算処理装置10が要求値の設定対象となる入力点に設定しようとする要求値が、他の第1の演算処理装置10が当該入力点に設定する要求値と異なるコンフリクトが発生すると、第2の演算処理装置20が判定した場合、当該第1の演算処理装置10は当該要求値の設定を抑止する。

(もっと読む)

電子デバイスにおけるパケットエラー率の決定論的試験のためのシステム及び方法

【課題】電子機器におけるパケットエラー率を試験する方法及びシステムを提供する。

【解決手段】試験器104からDUT102に一連のデータパケット201を送信し、事前定義される受信エラーフリーデータパケットの数を設定し、一連のデータパケット201からDUT102でエラーなしに受信されたデータパケット201の数が事前定義される受信エラーフリーデータパケットの数と等しいか評価し、一連のデータパケット201からDUT102でエラーなしに受信されたデータパケット201の数が事前定義される受信エラーフリーデータパケットの数と等しくないとき正常動作のDUT102でゼロの受信パケットエラーを生成することが既知の電力レベルで試験器104からDUT102に追加データパケットを送信して、電子機器におけるパケットエラー率を試験する。

(もっと読む)

スキャンテスト回路およびスキャンテスト回路生成方法

【課題】スキャンテストにおいて、異クロックドメイン間のユーザロジックパスに対するホールド違反を起こさない。

【解決手段】第1スキャンフリップフロップ(111/112)は、第1クロック信号(CLK1/CLK2)に応答して動作する第1クロックドメイン(101/102)に含まれ、スキャンテスト時に形成されるスキャンチェーンに組み込まれる。ホールド対応回路(202/201)は、第1クロック信号(CLK1/CLK2)と周波数の異なる第2クロック信号(CLK2/CLK1)に応答して動作する第2クロックドメイン(102/101)に属し、スキャンチェーンにテスト結果を取り込むキャプチャ期間に第1スキャンフリップフロップ(111/112)に出力するデータを固定する。スキャンテスト時には、第1クロックドメインおよび第2クロックドメイン(101、102)に同一周波数のクロック信号が供給される。

(もっと読む)

テストプログラムジェネレータ

【課題】テストアルゴリズムの変更無しでテスト実行部を任意に追加する機能を提供する。

【解決手段】半導体集積回路テスタのハードウェアに依存しない書式でテスト実行部記述ファイルを記載する。このテスト実行部記述ファイル102をテスタ実行書式変換部106がハードウェアに依存する形式に変換する。変換後のテスト実行部記述ファイル102‐2を受信したテストプログラムジェネレータ103は、これを解析し、テスト条件100とテストアルゴリズム101から生成したテストプログラム104の該当箇所にテスト実行部プログラムを挿入する。

(もっと読む)

半導体試験装置、半導体試験方法および半導体試験プログラム

【課題】高速なパターンと低速なパターンとを混在させて被試験デバイスの試験を行うときに、試験時間の短縮化を図りつつ同期を取ることを目的とする。

【解決手段】低速パターンジェネレータ2Lと、低速パターンジェネレータ2Lよりも高速に動作する高速パターンジェネレータ2Hと、パターンを記述した記述パターンに基づいて、低速パターンジェネレータ2Lが1回の動作を行う間に高速パターンジェネレータ2Hが動作する回数を動作回数Nとして検出する動作回数検出部23と、低速パターンジェネレータ2Lが1回の動作を行ったときに要する時間と高速パターンジェネレータ2Hが動作回数Nの動作を行ったときに要する時間との間の時間差を補正時間ΔTとして検出する補正時間検出部24と、を備え、高速パターンジェネレータ2Hは、動作回数Nおよび補正時間ΔTに基づいて動作を行っている。

(もっと読む)

パターンプログラム作成支援装置、コンピュータプログラム

【課題】高速パターン発生器と、低速パターン発生器とを備えた半導体試験装置で、希望する低速レート時間長とサイクル比とで半導体試験を行なえるようにする。

【解決手段】高速パターン発生器の分解能の設定を受け付けるパターン発生器パラメータ設定部と、作成対象のパターンプログラムの低速レート時間長と、サイクル比の設定を受け付けるプログラム条件設定部と、低速レート時間長をサイクル比で割った値未満で最も大きい分解能の倍数を切捨てレート時間長とし、値超で最も小さい分解能の倍数を切上げレート時間長とするレート時間長算出部と、低速レート時間長に対応する高速パターンのサイクルにおける切捨てレート時間長の個数と切上げレート時間長の個数とを、合計のレート時間長が低速レート時間長と等しくなるように設定する個数設定部とを備えたパターンプログラム作成支援装置。

(もっと読む)

パターンプログラム作成支援装置、パターンプログラム作成支援方法およびコンピュータプログラム

【課題】アドレス動作を含んだパターンプログラムを作成するユーザの負担を軽減させる。

【解決手段】半導体試験におけるアドレス動作を行なうアドレス範囲に対応したセルを表示し、アドレス順番の指定を受け付ける入出力部と、指定されたアドレス順番を、所定のプログラム言語で定義されたアドレス演算命令に変換するプログラム変換部とを備えたパターンプログラム作成支援装置。入出力部は、前記セルの表示に先立ち、アドレス範囲の設定を受け付けるようにしてもよい。また、変換された前記アドレス演算命令を表示して、編集を受け付けるプログラム編集部をさらに備えるようにしてもよい。

(もっと読む)

任意波形発生装置とそれを用いた半導体試験装置

【課題】新規開発中の検査対象半導体の仕様に応じて、任意波形発生装置のユーザーが複雑なテスタ言語を用いることなく仕様変更に応じた所望のデジタルデータを作成できて半導体製品の開発における任意波形発生装置のユーザーの負担を軽減でき、半導体製品を比較的短期間に開発して市場に投入できる任意波形発生装置とそれを用いた半導体試験装置を提供すること。

【解決手段】複数の波形発生チャネルの波形信号を加算して出力するように構成された任意波形発生装置において、前記複数の波形発生チャネルの波形信号は、それぞれアナログ信号で加算されることを特徴とするとともに、このように構成される任意波形発生装置を用いた半導体試験装置である。

(もっと読む)

故障検出用パターン圧縮システム、方法、及びプログラム

【課題】故障検出用パターンの冗長なステップを自動的に削除する。

【解決手段】故障検出用パターンごとの各ステップで検出される故障箇所の一覧において、同じ故障箇所の中で一番小さいステップで検出されるもの以外を削除し、故障箇所が一つも残らなかった故障検出用パターンを削除し、故障箇所が残ったステップで一番大きいものを有する故障検出用パターンを選択し、選択された故障検出用パターンを削除すると同時に残った故障検出用パターンで検出される故障箇所を削除前に戻し、選択された故障検出用パターンで検出される故障箇所を削除することを、この一覧の故障箇所全てが、選択された故障検出用パターンだけで検出されるまで繰り返し、

この一覧において、選択された故障検出用パターンだけを残し、これが選択される以前に選択された故障検出用パターンでは検出されない故障箇所のステップで一番大きなものよりも大きなステップがあれば削除する。

(もっと読む)

テスト装置およびテスト信号発生装置

【課題】集積回路をテストするテスト装置において、費用、期間を削減する。

【解決手段】テスト装置1の制御部11は、集積回路6のテストを制御するための信号を出力する。テスト信号発生部66は、制御部11から出力された信号の入力に応じて、集積回路6に入力可能なテスト信号を発生する。分岐マルチプレクサ41には、複数の集積回路6が接続される。分岐マルチプレクサ41は、テスト信号を複数の分岐テスト信号に分岐し、接続されている複数の集積回路6に対して並列に出力する。

(もっと読む)

半導体集積回路の診断テストパターン数最適化プログラム

【課題】

組込み自己試験法によるテスト機構を備えた半導体集積回路において、診断テストパターン数を増加させずに故障検出率を向上させることができるプログラムを提供する。

【解決手段】

診断テストパターンとして発生した擬似乱数の各々で新たに検出される故障数が0又は、所定の基準値以下であるかを判定するステップと、テストグループに割り当てられた診断テストパターン発生回数の最後で発生した擬似乱数で新たに検出される故障数が任意の基準値以上であるかを判定するステップとから、パス数比でテストグループに割り当てられた診断テストパターン数を、故障の検出のし易さ(難易度)に応じて再配分することで診断テストパターン数を最適化し、故障検出率を向上させる。

(もっと読む)

論理検証装置及び論理検証方法

【課題】論理検証結果の漏れを低減するための論理検証装置を提供する。

【解決手段】論理検証装置10は、検証対象回路の策定動作の第1前提記述と第1前提に基づく策定動作の第1仕様記述とを含む第1アサーション92と、検証対象回路の策定動作を検証するための第1テストパタンと、を受け付ける入力部11と、第1アサーション92を解析することにより、検証対象回路の信号の値の確定条件を示す確定ルールアサーションと、検証対象回路の信号の値の保持条件を示す保持ルールアサーションと、を抽出する抽出部12と、抽出された確定ルールアサーション及び保持ルールアサーションに基づいて、確定条件と検証対象回路の信号との関係を示すテーブル生成部13と、これに基づいて、第1アサーション92及び第1テストパタンに含まれていない検証対象回路の非策定動作を検証するための検証情報を生成する検証情報生成部14と、を備える。

(もっと読む)

半導体集積回路の試験装置、試験方法、及びプログラム

【課題】 本発明の課題は、半導体集積回路の試験装置が試験パタンデータを生成して半導体集積回路へ書き込むことを目的とする。

【解決手段】 上記課題は、半導体集積回路のメモリへの書き込みを試験するための試験パタンデータを生成するパタンデータ生成手段と、前記試験パタンデータを前記半導体集積回路の該試験パタンデータを格納する記憶領域へ書き込む書き込み手段と、を有することを特徴とする半導体集積回路の試験装置により達成される。

(もっと読む)

診断装置、診断方法、その診断方法をコンピュータに実行させることが可能なプログラム、及びそのプログラムを記録した記録媒体

【課題】 診断の分解能をさらに向上させて良好な診断結果を得ることが可能な診断装置等を提供する。

【解決手段】 診断装置1は記号挿入部3を備え、記号挿入部3は能動素子用記号挿入部5と受動素子用記号挿入部7を有する。診断装置1は発生確率付与部9と等価発生確率付与部11と切替部13を備える。診断装置1によるパーテストX故障診断フローは故障情報の収集ステージと診断の結論を出すステージで構成される。受動素子用記号挿入部7により、ディープサブミクロンLSI回路のレイアウトがしばしば多層配線を必要とし、広範囲で使用されるビアの情報が利用されるのでビアレベルでの欠陥個所を示すことが可能になり診断の分解能が大幅に向上する。発生確率付与部9により、新しい診断値を使用し、とりうる可能性のある故障の論理的組合せの発生確率を考慮するのでディープサブミクロンLSI回路の実動作がより良く反映され、診断の分解能の向上に役立つ。

(もっと読む)

テスタ用テストパタン生成方法、テスタ用テストパタン生成プログラム、及びテスタ用テストパタン生成装置

【課題】テスタによる機能テストのテスト精度を低下させずに、テスタ用テストパタンにおけるタイミングセット数を削減する。

【解決手段】本発明によるテスタ用テストパタンの生成方法は、論理設計時に生成された第1テストパタン201を、半導体集積回路で用いられる最高周波数のクロック信号20に応じたサイクルでサイクライズするステップと、第1テストパタン201におけるタイミングエッジを、タイミングエッジ直前のピリオド境界に変更して第2テストパタン301を生成するステップとを具備する。

(もっと読む)

1 - 20 / 127

[ Back to top ]