Fターム[5F003BJ12]の内容

バイポーラトランジスタ (11,930) | 複合 (843) | 他素子との組合せ (551) | ダイオード (122)

Fターム[5F003BJ12]の下位に属するFターム

ショットキーダイオード

コレクタランプ

ショットキー (15)

Fターム[5F003BJ12]に分類される特許

101 - 107 / 107

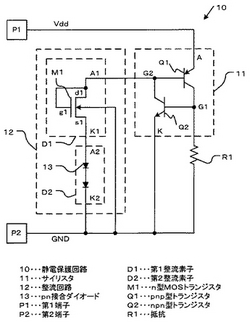

静電保護回路およびそれを用いた半導体集積装置

【課題】 サージおよびラッチアップの両方に対して十分な保護電圧を有し、集積化するのに好適な構造を備えた静電保護回路およびそれを用いた半導体集積装置を提供する。

【解決手段】 アノードAが第1端子P1に接続され、カソードKが第2端子P2に接続されたサイリスタ11と、第1の順方向電圧VF1を有する第1整流素子D1と、第1の順方向電圧VF1と異なる第2の順方向電圧VF2を有する第2整流素子D2とが順方向に直列接続され、サイリスタ11の第2ゲートG2に第1整流素子D1のアノードA1が接続され、サイリスタ11のカソードKに第2整流素子D2のカソードK2が接続された整流回路12とを具備する。

第1および第2の順方向電圧VF1、VF2の組み合わせにより、サイリスタ11のターンオン電圧を微調整する。

(もっと読む)

半導体装置

【課題】トランジスタのターンオフ時間を短くするため、トランジスタが組み込まれる外部回路で抵抗とダイオードを組み込むと、その抵抗やダイオードを組み込むスペースやその配線が回路基板などに確保される必要があり、電子機器の小形化の妨げになると共に、部品増および組立工数増などによるコストアップの原因になっている。

【解決手段】半導体基板に形成されるトランジスタのベース領域2と同時に形成されるダイオードのアノード領域4と、トランジスタのエミッタ領域3と同時に形成されるダイオードのカソード領域5とでダイオードを形成すると共に、導電体層6の一端とダイオードのアノード領域5が接続され、他の一端とダイオードのカソード領域4とが接続されている。トランジスタのベース領域2とカソード電極9との間に抵抗とダイオードを並列に接続することで、トランジスタのターンオフ時間を早くする。

(もっと読む)

トランジスタを具備したフリップチップ構造発光装置用サブマウント

【課題】 本発明はフリップチップ構造の発光装置において発光素子の搭載に用いられるトランジスタ付きサブマウントに関するものである。

【解決手段】 本発明は、フリップチップ構造の発光装置において窒化物半導体発光素子を搭載するためのサブマウントにおいて、第1導電型半導体物質から成る基板; 上記基板上の一領域に形成され第2導電型半導体物質から成る第1領域; 上記第1領域以外の領域に形成され第2導電型半導体物質から成る第2領域; 上記第1領域及び第2領域上に各々形成される第1及び第2電極; 及び、上記基板の背面に形成される導電層を含み、上記第1及び第2電極は上記窒化物半導体発光素子のn側電極及びp側電極とバンプを通して連結されることを特徴とするトランジスタを具備したサブマウントを提供する。本発明によると、フリップチップ構造の発光装置において窒化物半導体発光素子へ流入する静電気などによる高圧電流を遮断して素子の破壊を防止し、素子の信頼性を向上させる効果がある。

(もっと読む)

半導体回路

【課題】外部接続端子と接続するバイポーラトランジスタを含む被保護回路のESD耐圧を向上するようにした半導体回路の提供。

【解決手段】この発明は、被保護回路11と、この被保護回路11を静電気放電から保護するESD保護回路2とを備える。被保護回路11はバイポーラトランジスタTR1を含み、バイポーラトランジスタTRのエミッタが外部接続端子3と接続されている。バイポーラトランジスタTR1のコレクタと第1電源端子4との間に電流制限素子Zを設けている。電流制限素子Zは、第1電源端子4の電源電圧を基準に外部接続端子3に対して負のESDパルスが印加されたときに、バイポーラトランジスタTR1のエミッタ電流を制限して、そのトランジスタTR1の破壊から保護する。

(もっと読む)

半導体構造(調整可能半導体デバイス)

【課題】下方に配置された基板とは異なる極性を有する不連続な非平面状サブコレクタを含む半導体構造を形成する方法を提供する。

【解決手段】この構造は、サブコレクタの上方の活性領域(コレクタ)、活性領域の上方のベース、およびベースの上方のエミッタを含む。不連続なサブコレクタの不連続部分間の距離は、半導体構造の動作特性を調整する。調整可能な動作特性は、絶縁破壊電圧、電流利得遮断周波数、電力利得遮断周波数、通過周波数、電流密度、静電容量範囲、ノイズ注入、少数キャリヤ注入、ならびにトリガ電圧および保持電圧を含む。

(もっと読む)

コンプリメンタリ横型窒化物トランジスタ

基板の支持表面上に形成された、横方向に隣接した導電性半導体領域により構成された横方向に延びているスタックを備える半導体デバイスおよびそのデバイスを作製する方法。  (もっと読む)

(もっと読む)

高エネルギーESD構造および方法

同心リング状のESD構造(10)は、半導体材料の層(27)内に形成された第1p型領域(16)および第2p型領域(19)を含む。2つのp型領域(16,19)は、共に浮動n型埋込み層(26)に結合される。第1および第2p型領域(16,19)は、浮動n型埋込み層(26)と共にバックツーバック・ダイオード構造を形成する。1対の短絡されたn型(167,197)およびp型(166,196)の接触領域は、第1および第2領域(16,19)内にそれぞれ形成される。分離領域(17,32)は、第1および第2p型領域(16,19)間に形成される。  (もっと読む)

(もっと読む)

101 - 107 / 107

[ Back to top ]