Fターム[5F003BJ93]の内容

バイポーラトランジスタ (11,930) | 複合 (843) | 他素子との組合せ (551) | ダイオード (122) | ショットキー (15)

Fターム[5F003BJ93]に分類される特許

1 - 15 / 15

半導体装置

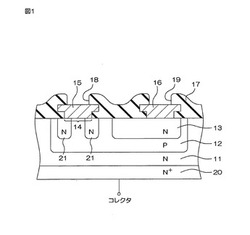

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

有機縦型トランジスタ

【課題】キャリア移動度が高く、低駆動電圧で大電流変調を可能とする有機縦型トランジスタを提供すること。

【解決手段】有機縦型トランジスタ1は、基板7と、エミッタ電極2と、第1有機半導体層3と、ベース電極4と、第2有機半導体層5と、コレクタ電極6とを備え、第1および第2有機半導体層3,5は、正孔輸送材料で形成され、各層を形成する有機半導体材料は、その分子構造に平面部分を有し、各分子の平面部分が基板7に対して略平行に配列し、その分子の形成するπ軌道が上下の分子のπ軌道と重なりを有し、分子が積層される配列方向に、エネルギー−波数(E−k)の関係を示す所定のバンド分散幅を有したエネルギーバンドを形成する。エミッタ電極2は、正孔を第1および第2有機半導体層3,5に注入する電極であり、エミッタ電極2およびコレクタ電極6は仕事関数が大きい材料、ベース電極4は仕事関数が小さい材料で形成されている。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

半導体装置

【課題】 第1導電領域(一導電型半導体層)と第2導電領域(逆導電型領域または金属層)が接合し、これらの間に逆方向電圧を印加して高い耐圧を確保する半導体装置において、耐圧を向上させる場合には、一導電型半導体層の不純物濃度を低減したり、半導体層の厚みを増加させるなどの手法を採用しており、オン抵抗が増大するなどの問題があった。

【解決手段】 第1導電領域内の第1の深さに逆導電型の複数の第1埋め込み領域を設け、第2の深さに逆導電型の複数の第2埋め込み領域を設ける。第2埋め込み領域の距離(第2の距離)を、第1埋め込み領域の距離(第1の距離)より大きくする。逆方向電圧印加時には実際の接合部が臨界電界に達する以前に、第1埋め込み領域によって第1の深さにおいて水平方向の電界がピンチオフし、耐圧を向上させることができる。同様に、第1の深さにおける電界強度が臨界電界に達する以前に第2埋め込み領域によって第2の深さにおいて水平方向の電界がピンチオフし、耐圧を増加させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波用途の半導体装置に採用する厚い絶縁膜をLOCOS法で形成する場合に、バーズビーグ増による欠陥の増大や、高温で長時間の酸化時間に伴う欠陥の増大という問題があった。これ等の問題点を考慮すると、超高周波用途の半導体装置に現状で用いることができる酸化膜の膜厚を厚くするにも限界があった。

【解決手段】半導体層に複数のトレンチを設け熱酸化により一体化して、内部に空隙部を有する絶縁領域を形成する。トレンチの深さで絶縁領域の厚みを制御でき、従来のLOCOS法以上の厚い絶縁領域を結晶欠陥等を増大することなく形成できる。絶縁領域を例えば電極パッドの下方に設けることにより、浮遊容量を低減できる。また、絶縁領域内部の空隙部によって、更に浮遊容量を低減できる。

(もっと読む)

ワイドバンドギャップデバイスのためのアバランシェ保護

本発明は、ワイドバンドギャップデバイスを電圧過渡の抑制の間の損傷から保護する方法及びデバイスである。アバランシェ耐量を向上させることは、ワイドバンドギャップデバイスのブロック接合部に1つ以上のダイオード又はPNPトランジスタを配置することにより達成される。  (もっと読む)

(もっと読む)

メサ型バイポーラトランジスタ

【課題】200℃以上の環境温度でも実用上十分な電流増幅率を確保できるバイポーラトランジスタ、わけても小型な電力用バイポーラトランジスタを提供する。

【解決手段】ベースのアクセプタ濃度勾配をコレクタ層端に比較してエミッタ層端で大きくした。また、エミッタ層およびベース層からなる第1のメサ構造と、ベース層およびコレクタ層からなる第2のメサ構造との距離(L2)を3μm以上9μm以下とした。さらに、ベース層を均一なアクセプタ濃度を有する第1のp型ベース層と、深さ方向に濃度傾斜を有する第2のp型ベース層から構成した。これらの手段により、電流増幅率を確保でき、小型化に適した高温対応電力用バイポーラトランジスタ。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

半導体装置の製造方法

【課題】P+層を形成する時にステッパーマスクを用いることなく、約2.0μmの幅を有するP+層を、約2.5μmの幅を有するP−層の外縁よりも内側に配置する

【解決手段】P−層5上にP+層7を配置する工程を含む半導体装置の製造方法において、P−層5を形成する時に用いられた酸化膜3の開口3aと同じものをP+層7を形成する時に用い、P−層5を形成するための熱処理よりも、P+層7を形成するための熱処理を弱くした。好ましくは、P−層5を形成する時に用いられた酸化膜3の開口3aに形成された新たな酸化膜3bに対してリンデポジションを行う工程を、P+層7を形成する工程の前に設けた。

(もっと読む)

ダイオード内蔵パワースイッチングデバイスとその製造方法

【課題】フライホイールダイオードを内蔵したパワースイッチングデバイスにおける、高速スイッチング性向上と、安価に製造できるデバイス構造と製造方法。

【解決手段】下面にコレクタ電極を有するN+半導体層上面に形成したN-半導体層上面から厚み方向にP型領域を櫛状に形成し、該P型領域上面をエミッタ電極に接続したショトキー金属層に接合してなる、MPS構造体のダイオードをコレクタ・エミッタ間に造り込み、MPS構造のダイオードの逆回復時間が従来のPINダイオードの6分の1に短くすることが出来た。

(もっと読む)

マイクロ波モノリシック集積回路

【課題】HBTにおける高い耐電圧特性と優れた高速特性を維持した状態で、バラクタダイオードにおける広い容量可変幅を確保する。

【解決手段】1つの共通の半絶縁性基板1上に、HBT20とバラクタダイオード21とを形成したマイクロ波モノリシック集積回路において、HBTとバラクタダイオード21とに共通するコレクタ層を、コレクタコンタクト層4側に位置する第1のコレクタ層22a、22bと、反コレクタコンタクト層側に位置する第2のコレクタ層23a、23bとで構成し、さらに、第1のコレクタ層のキャリア濃度を第2のコレクタ層のキャリア濃度より高く設定している。そして、バラクタダイオード21においては、第2のコレクタ層23b上にショットキー電極24を形成する。

(もっと読む)

金属ベーストランジスタおよびそれを用いた発振器

【課題】 テラヘルツ帯の分光ならびに透視装置を小型・低コストで実現する上で、これに用いられる発振器を小型・低コスト化することが最重要課題であった。

【解決手段】 発振器の能動素子に金属ベーストランジスタを採用し、その最大発振周波数を数THzにまで向上するために、電子の飽和速度の高いInN或いはInNを主成分とする材料をコレクタに用いた。特性を再現性よく得るために、コレクタとベースの界面にInGaNを挿入することが有用である。本発明の金属ベーストランジスタを用いてテラヘルツ帯の発振を可能とする発振器を構成することが可能である。又、この発振器を信号源あるいは局所発振器の少なくとも一つに適用した分光装置を提供する。

(もっと読む)

SiC半導体素子

【課題】 逆方向電圧が印加された場合の素子破壊の発生を低減することができるSiC半導体素子を提供する。

【解決手段】 高濃度層11は、高濃度のn型SiCからなる層であり、SiC基板を構成している。高濃度層11の表面には、低濃度のn型SiCからなる低濃度層12が形成され、低濃度層12の表面には、p型SiCからなるガードリング領域13が形成されている。低濃度層12およびガードリング領域13の上には、低濃度層12とショットキー接合を形成しているバリアメタル膜14、パッド電極15、および絶縁膜16が形成されている。高濃度層11の他方の面には、高濃度層11とオーミック接合を形成しているオーミックメタル膜17および裏面電極18が形成されている。低濃度層12において、ガードリング領域13の近傍には、低濃度層12の表面に露出するように結晶欠陥領域19aが形成されている。

(もっと読む)

半導体構造(調整可能半導体デバイス)

【課題】下方に配置された基板とは異なる極性を有する不連続な非平面状サブコレクタを含む半導体構造を形成する方法を提供する。

【解決手段】この構造は、サブコレクタの上方の活性領域(コレクタ)、活性領域の上方のベース、およびベースの上方のエミッタを含む。不連続なサブコレクタの不連続部分間の距離は、半導体構造の動作特性を調整する。調整可能な動作特性は、絶縁破壊電圧、電流利得遮断周波数、電力利得遮断周波数、通過周波数、電流密度、静電容量範囲、ノイズ注入、少数キャリヤ注入、ならびにトリガ電圧および保持電圧を含む。

(もっと読む)

1 - 15 / 15

[ Back to top ]