Fターム[5F082BA32]の内容

Fターム[5F082BA32]に分類される特許

1 - 19 / 19

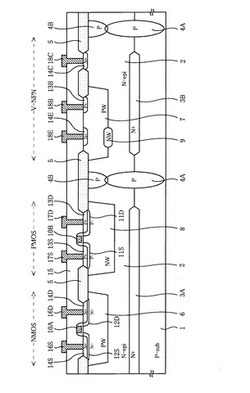

半導体装置及びその製造方法

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

半導体装置とその製造方法

【課題】 エミッタ注入効率が大きく、差動増幅回路の入力トランジスタとして利用可能で、かつBi−CMOSプロセスにおいてMOSトランジスタと同一基板上に搭載することが可能なバイポーラトランジスタの構造とその製造方法を提供する。

【解決手段】 半導体基板1上に第二導電型の深いウェル層2が形成され、深いウェル層2よりは浅い所定の深さで第一導電型の埋め込み層3が形成され、バイポーラトランジスタのエミッタ領域が、第一導電型の埋め込み層3の上に、第二導電型のウェル層4、及びMOSトランジスタのソース・ドレイン領域と同時形成される高濃度の第二導電型の不純物層15の2層構造として形成されている。

(もっと読む)

トランジスタ構造および半導体装置

【課題】パワー半導体素子として、動作時の熱暴走および熱破壊が防止でき、且つ、安全動作領域SOAが拡大されるトランジスタを提供する。

【解決手段】第1導電型のコレクタ層2と、前記コレクタ層上に島状に形成され且つ前記第1導電型と異なる第2導電型のベース層3と、前記ベース層上に少なくとも1つの島状に形成され且つ前記第1導電型のエミッタ層4a,4bと、前記ベース層と電気的に接続されベースコンタクト9を形成するベース電極と、前記エミッタ層と電気的に接続されエミッタコンタクト10を形成するエミッタ電極と、前記コレクタ層と電気的に接続されたコレクタ電極と、を有し、前記エミッタ層上に形成され且つ前記第1導電型の第1抵抗層11が、平面的に見て、前記ベースコンタクトを包囲するように形成されることを特徴とするトランジスタ構造。

(もっと読む)

半導体装置とその製造方法

【課題】 複数個の半導体素子を備えている半導体装置において、その半導体装置のサイズを小さくする技術を提供する。

【解決手段】 不純物注入工程では、半導体基板9の表面にn型半導体領域13とp型半導体領域14が隣接して出現する関係に不純物の注入範囲を管理して、不純物を半導体基板9に注入する。熱処理工程では、半導体基板9を加熱して半導体基板9に注入した不純物12、14を活性化する。トレンチ形成工程では、半導体基板9の表面に隣接して出現しているn型半導体領域13とp型半導体領域14の双方を分断して一巡するととともに半導体基板9の表面から半導体基板9の裏面に向けて不純物の注入範囲12、14を貫通する深さにまで伸びているトレンチ15を形成する。絶縁膜形成工程では、トレンチ15内に絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタと抵抗素子とを備える半導体装置の製造工程を簡素化することが可能な技術を提供する。

【解決手段】NMOSトランジスタが形成される活性領域AR4と、拡散抵抗素子が形成される活性領域AR5とを半導体層2に区画する素子分離構造3を当該半導体層2に形成する。その後、n型のソース・ドレイン領域33を活性領域AR4に形成する。そして、得られた構造に対して、その上方からマスクレスでp型不純物102pを導入して、活性領域AR5に抵抗素子として機能する不純物領域を形成する。このとき、ソース・ドレイン領域33内からはみ出すことなく、かつソース・ドレイン領域33のうちp型不純物102pが導入される領域での導電型がn型を維持するように、活性領域AR4に対してp型不純物102pが導入される。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタを用いたESD保護回路の面積効率を向上する。

【解決手段】集積回路は、回路用バイポーラトランジスタ124を含む内部回路121と、内部回路121をサージから保護するための保護用バイポーラトランジスタ120とを備え、保護用バイポーラトランジスタ120におけるエミッタとベースとは短絡されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 結晶欠陥の発生を防止することができる半導体装置及び半導体装置の製造方法を実現する。

【解決手段】 SOI基板11に形成され、トレンチ11eにより分離された複数の素子形成領域内に、バイポーラトランジスタ12及びCMOS13を形成するBiCMOSである半導体装置10において、バイポーラトランジスタ12の表面のみを覆って形成された耐酸化膜19を備えているため、CMOS13に熱酸化法によりゲート酸化膜24及びゲート保護膜26を形成する際にも、バイポーラトランジスタ12の表面を熱酸化しないようにすることができる。これによれば、高濃度のイオンが注入されたコレクタ16、エミッタ17などのイオン注入領域が、熱酸化されることがないので、結晶欠陥の発生を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】 相補型バイポーラトランジスタで、PNPトランジスタとNPNトランジスタの両方のエミッタ領域を多結晶シリコン膜から添加された不純物を同時に拡散させながら、その拡散深さを同程度で目標の浅い拡散層を形成し、しかも他の拡散層に影響を与えることなく、高特性の相補型のバイポーラトランジスタを得るための製造方法を提供する。

【解決手段】 PNPトランジスタのエミッタ領域を形成する部分の多結晶シリコン膜9にボロンイオンを注入し、イオン注入されたボロンを低温の熱処理により、多結晶シリコン膜内に拡散し、NPNトランジスタのエミッタ領域を形成する部分の多結晶シリコン膜9にリンイオンを注入し、高温で短時間の熱処理を行うことにより、多結晶シリコン膜中のボロンイオンおよびリンイオンをそれぞれPNPとNPNのトランジスタのベース領域7、8中に同時に拡散して、それぞれのエミッタ領域16、17を形成する。

(もっと読む)

半導体装置の静電破壊保護方法及び静電破壊保護装置

【課題】従来の静電破壊保護方法では、ブレークダウンさせたダイオードを経由してサージ電流を放電していたため、過電流によるダイオードの破壊を防ぐ必要があった。

【解決手段】本発明にかかる半導体装置の静電破壊保護方法は、第1、第2の端子を有する半導体装置において、半導体装置を第1、第2の端子間に印加されるサージ電流から保護する半導体装置の静電破壊保護方法であって、半導体装置は、第1の端子から第2の端子に向かって順方向電流を流すベース・エミッタ間に形成されるダイオードと、導通状態において第2の端子から第1の端子に向う方向で電流を流すNPNトランジスタ2あるいはPNPトランジスタ3とを有し、第1、第2の端子間の電位差がダイオードを降伏させる電位差となる前にNPNトランジスタ2あるいはPNPトランジスタ3のコレクタ端子とエミッタ端子とが導通状態となるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】NPNトランジスタ等のバイポーラリニア素子とIIL素子とを同一の半導体基板上に備えた半導体装置であって、高耐圧であるとともに、動作特性の優れたIIL素子を有するものを提供すること。

【解決手段】IIL素子に含まれたマルチコレクタ型NPNトランジスタTr1は、半導体基板101の裏面側から表面側へ向かう縦方向に順にN型エミッタ層Tr1E、P型ベース層Tr1B、N型コレクタ層Tr1Cを備える。マルチコレクタ型NPNトランジスタのP型ベース層Tr1Bは、エミッタ層Tr1E側で高く、かつコレクタ層Tr1C側で低くなるように傾斜した不純物濃度プロファイルを持つ。

(もっと読む)

定電流回路

【課題】定電流回路を構成するチップの面積縮小を図ることができる回路構成を提供する。

【解決手段】トランジスタ6のベース電流を流すための起動素子をツェナーダイオード7で構成する。そして、このツェナーダイオード7を構成する各拡散層20〜22をリーク電流が発生するような不純物濃度に設定する。このため、ツェナーダイオード7は、リーク電流分の電流を流し、かつ、ツェナーダイオード7の両端間に電位差(Vz×ツェナーダイオード7の個数)を発生させるため、抵抗と等価の役割を果たすことができる。このように、起動素子をツェナーダイオード7で構成することにより、起動素子を抵抗で構成する場合と比べて必要な面積を低減することが可能となる。したがって、定電流回路を構成するチップの面積縮小を図ることができる回路構成が可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造に多くの工数を必要とせず、回路特性変動を抑制することが可能である半導体装置を提供する。

【解決手段】 シリコン基板1に形成されたNPNトランジスタQ1と、シリコン基板1に形成された複数の抵抗領域8から構成され、NPNトランジスタQ1にNPNトランジスタQ1のhFEに対応したバイアス電圧を与えるための抵抗素子と、複数の抵抗領域8のうちの、抵抗素子の抵抗として機能する抵抗領域8とNPNトランジスタQ1とを接続する配線23aとを備える。

(もっと読む)

マイクロ波モノリシック集積回路

【課題】HBTにおける高い耐電圧特性と優れた高速特性を維持した状態で、バラクタダイオードにおける広い容量可変幅を確保する。

【解決手段】1つの共通の半絶縁性基板1上に、HBT20とバラクタダイオード21とを形成したマイクロ波モノリシック集積回路において、HBTとバラクタダイオード21とに共通するコレクタ層を、コレクタコンタクト層4側に位置する第1のコレクタ層22a、22bと、反コレクタコンタクト層側に位置する第2のコレクタ層23a、23bとで構成し、さらに、第1のコレクタ層のキャリア濃度を第2のコレクタ層のキャリア濃度より高く設定している。そして、バラクタダイオード21においては、第2のコレクタ層23b上にショットキー電極24を形成する。

(もっと読む)

半導体装置およびその製造方法ならびに電子装置

【課題】 熱的安定性と信頼性を両立し、さらに静電破壊耐量を向上したHBTを備えた半導体装置を提供する。

【解決手段】 化合物半導体からなる基板の主面上に、順に形成されたサブコレクタ層、コレクタ層、ベース層4およびエミッタ層5、ならびにコレクタ層4と電気的に接続されたコレクタ電極、ベース層4と電気的に接続されたベース電極、エミッタ層5上に形成され、エミッタ層5と電気的に接続されたエミッタメサ層6M、およびエミッタメサ層6Mと電気的に接続されたエミッタ電極13を備えたHBTであって、このエミッタメサ層6Mが、n型GaAs層からなる半導体層6と、半導体層6上のn+型GaAs層からなる高濃度半導体層6Bと、高濃度半導体層6B上のn型InGaAs層からなるバラスト抵抗層7とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 工程の追加をせず、かつpn接合上に形成される酸化膜などによって特性上の影響を受けることなく、安定な定電圧を得られる半導体装置及びその製造方法を提供する。

【解決手段】 一導電型の半導体層の表面に、逆導電型の第2の半導体層と、該逆導電型の第2の半導体層の外周を囲んで側面が重なり合うように、前記第2の半導体層より不純物濃度が低い逆導電型の第1の半導体層とが設けられ、前記第1の半導体層と前記第2の半導体層の表面に、一導電型の第3の半導体層と、その外側に側面を接して、前記第3の半導体層より不純物濃度が低い一導電型の第4の半導体層とが設けられ、前記第3の半導体層の底部での前記第2の半導体層とのpn接合によりツェナダイオードが形成され、前記第1の半導体層の表面に前記第2の半導体層に接続する前記ツェナダイオードの一方の端子が設けられていることを特徴とする。

(もっと読む)

半導体集積回路の製造方法および半導体集積回路

複数のバイポーラトランジスタを備えた半導体集積回路であって、複数のトランジスタ作製領域(A1,A2)において、第1導電型のコレクタ層(2)の表面側に形成されていると共にゲルマニウムを有する第2導電型のベース層(4)の表面側に、ベース層(4)よりもバンドギャップが大きい半導体材料からなる第1導電型のエミッタ層(6)が形成されていることにより複数のバイポーラトランジスタが構成されており、複数のトランジスタ作製領域(A1,A2)間において、エミッタ層(6、61)に含まれる不純物の濃度が異なっており、これによって、少なくとも2つのトランジスタ作製領域(A1,A2)がそれぞれ有するベース−エミッタ接合界面におけるゲルマニウムの濃度が異なることにより、複数のバイポーラトランジスタをオン動作させるために必要なオン電圧が異なる半導体集積回路である。この半導体集積回路によれば、バイポーラトランジスタの性能を良好に維持しつつ低消費電力化が可能になる。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]