Fターム[5F082BA33]の内容

Fターム[5F082BA33]に分類される特許

1 - 20 / 44

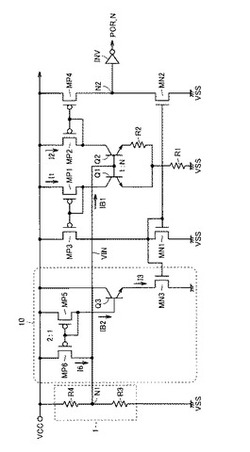

電圧検知回路

【課題】高精度で低コストの電圧検知回路を提供する。

【解決手段】パワーオンリセット回路は、分圧回路1、バイポーラトランジスタQ1,Q2、抵抗素子R1,R2、およびベース電流補償回路10を備える。分圧回路1の出力電圧VINがバンドギャップ電圧VBGの場合、バイポーラトランジスタQ1,Q2のコレクタ電流I1,I2が一致する。電圧補償回路10は、電流I1に基いてバイポーラトランジスタQ1,Q2のベース電流の和に相当する電流I6を生成し、その電流I6をバイポーラトランジスタQ1,Q2のベースに供給する。したがって、バイポーラトランジスタQ1,Q2の各々のベース電流が大きい場合でも、高い検出精度が得られる。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高周波帯域で動作する半導体装置の特性向上と製造コストの低減とを両立した半導体装置およびその製造方法を提供する。

【解決手段】同一の半絶縁性GaAs基板1上に積層された複数の半導体層を用いて複数の半導体素子が形成された半導体装置100であって、FET領域23を用いて形成されたFETと、FET領域23と隣接するHBT領域22を用いて形成されたHBTと、FET領域23とHBT領域22との間である素子分離領域24に設けられ、FET領域23とHBT領域22とを分離する分離溝25とを備え、分離溝25は、内壁面と該内壁面の端部とに接地電位を有する導電性金属層が形成されることにより、素子分離領域24を通過する素子間リーク電流を抑制する。

(もっと読む)

増幅素子およびその製造方法

【課題】ECMのインピーダンス変換および増幅を行うために、増幅集積回路素子や、J−FETが用いられている。増幅集積回路素子は、回路定数によりゲイン(Gain:利得)を適宜選択でき、一般的にはJ−FETを用いた場合と比較してゲインが高い利点があるが、回路構成が複雑でありコストも高い問題がある。一方、J−FETのみでは出力が十分に増幅されず、ゲインが低い問題がある。

【解決手段】J−FETとバイポーラトランジスタを1チップに集積化し、J−FETのソース領域とバイポーラトランジスタのベース領域を接続し、J−FETのドレイン領域とバイポーラトランジスタのコレクタ領域を接続したディスクリート素子を提供する。これにより、高入力インピーダンスで低出力インピーダンスのECM用増幅素子を実現できる。

(もっと読む)

半導体装置

【課題】従来のSOI基板を用いたIGBTは、ホリゾンタル型のバイポーラ構造を有する構造が主流であり、主電流を半導体基板面と平行に流すことで、高い耐電圧と多くの電流を採りやすい構造であったが、その電流駆動能力を高くすることができなかった。

【解決手段】本発明の半導体装置は、IGBTを構成するバイポーラトランジスタを、バーチカル型とホリゾンタル型との2つのバイポーラトランジスタで構成している。ホリゾンタル型バイポーラトランジスタの電流駆動能力に加え、バーチカル型バイポーラトランジスタの電流駆動能力も加わるため、半導体基板の薄膜化の要求下にあっても高い電流駆動能力を有することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレードオフの関係にあるHBTの特性上のメリットとHFETの特性上のメリットとを両立することが可能な半導体装置及びその製造方法を提供する。

【解決手段】Bi−HFETであって、HBTは、順次積層されたサブコレクタ層107、GaAsコレクタ層108、GaAsベース層109及びInGaPエミッタ層110を有し、サブコレクタ層107は、GaAs外部サブコレクタ領域107aと、GaAs外部サブコレクタ領域107a上に位置するGaAs内部サブコレクタ領域107bとを有し、GaAs外部サブコレクタ領域107a上には、メサ状のコレクタ部830と、コレクタ電極203とが離間して形成され、HFETは、GaAs外部サブコレクタ領域107aの一部により構成されたGaAsキャップ層105と、GaAsキャップ層105上に形成されたソース電極304及びドレイン電極305とを有する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】半導体集積回路装置の設計工数を低減する。

【解決手段】SOI基板1の半導体層において、互いに完全に電気的に分離された複数の単位バイポーラトランジスタQuを並列接続することにより、大電流容量を必要とするバイポーラトランジスタを構成する。また、所望の電流容量を与えるトランジスタは、幾何学的寸法が、実質的に同一サイズである複数の単位バイポーラトランジスタを、互いに電気的に並列接続することにより構成する。

(もっと読む)

トランジスタ構造および半導体装置

【課題】パワー半導体素子として、動作時の熱暴走および熱破壊が防止でき、且つ、安全動作領域SOAが拡大されるトランジスタを提供する。

【解決手段】第1導電型のコレクタ層2と、前記コレクタ層上に島状に形成され且つ前記第1導電型と異なる第2導電型のベース層3と、前記ベース層上に少なくとも1つの島状に形成され且つ前記第1導電型のエミッタ層4a,4bと、前記ベース層と電気的に接続されベースコンタクト9を形成するベース電極と、前記エミッタ層と電気的に接続されエミッタコンタクト10を形成するエミッタ電極と、前記コレクタ層と電気的に接続されたコレクタ電極と、を有し、前記エミッタ層上に形成され且つ前記第1導電型の第1抵抗層11が、平面的に見て、前記ベースコンタクトを包囲するように形成されることを特徴とするトランジスタ構造。

(もっと読む)

モータ駆動回路、ファンモータ、電子機器、及びノート型パーソナルコンピュータ

【課題】異常動作の発生を抑制することを可能にする。

【解決手段】モータ駆動回路は、入力電極が電源側に接続され出力電極がモータコイルの一端と接続される第1トランジスタと、入力電極がモータコイルの一端と接続され出力電極が接地側に接続される第2トランジスタと、入力電極が電源側に接続され出力電極がモータコイルの他端と接続される第3トランジスタと、入力電極がモータコイルの他端と接続され出力電極が接地側に接続される第4トランジスタと、第1及び第4トランジスタがオンの状態と第1〜第4トランジスタ全てがオフの状態とを適宜選択してモータコイルを駆動する駆動制御回路と、入力電極が電源側に接続され出力電極がモータコイルの一端と接続された第5トランジスタと、第5トランジスタがオンになると第4トランジスタをオンさせる保護回路とを備える。

(もっと読む)

電力増幅器

【課題】集積回路チップと実装基板との接続の容易性や、放熱性の良好さを維持したままで、各単位セル動作の均一性を確保し、出力段トランジスタの総合的な動作特性を改善する。

【解決手段】

コレクタ電極配線101は、平行する2つの単位セル列用コレクタ電極配線1,2が、その一方の端部で、出力用配線3によって接続されてなり、この出力端とされる一方、単位セル列用コレクタ電極配線1,2の他方の端部は、セル列間接続配線4により相互に接続されたものとなっており、これによって、各単位セルの動作の均一性の改善がなされるものとなっている。

(もっと読む)

1 - 20 / 44

[ Back to top ]