Fターム[5F082DA05]の内容

Fターム[5F082DA05]の下位に属するFターム

Fターム[5F082DA05]に分類される特許

1 - 20 / 22

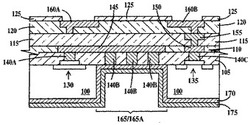

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体装置の製造方法

【課題】工程増加、マスク増加を伴うことなく、回路に影響を与えない導電パスを配置でき、精密なエッチングが可能な半導体装置の製造方法を提供すること

【解決手段】本発明にかかる半導体装置の製造方法は、半導体基板上に形成された複数の半導体素子が配線で電気的に接続されている集積回路を備える半導体装置の製造方法であって、配線と同じ接続で半導体素子に接続する導電パスを形成し、導電パスで半導体素子を電気的に接続した状態でエッチングし、導電パスと同じ接続で半導体素子に接続する配線を形成するものである。

(もっと読む)

バイポーラ型の半導体装置およびその製造方法

【課題】高い信頼性を持つ車載用高耐圧のバイポ−ラ型半導体装置を提供する。

【解決手段】面方位(111)オフアングル 3〜4°の支持基板上に活性領域をエピタキシャル成長させたエピ基板を用いて形成した高耐圧バイポ−ラ型半導体装置(以下、高耐圧BIP−IC)において、コンタクト孔底部および、接合分離層上面を除き、高耐圧BIP−IC表面を減圧熱分解CVD法により形成した薄い窒化シリコン膜(下層)と薄い酸化膜シリコン(上層)の積層膜で被覆することにより、保護膜として用いるプラズマCVDによる窒化シリコン膜(以下、プラズマ窒化シリコン膜)中の水素に起因したフィ−ルド部の寄生MOSのしきい値:フィ−ルドVtの低下を抑止し回路誤動作の防止するとともに、前記薄い窒化シリコン膜と薄い酸化膜シリコンの積層膜をコンデンサ膜の一部として用いることによりコンデンサの信頼性を向上せしめる。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタ構造を有する静電破壊保護素子のホールド電圧を従来に比して高くするとともに、当該素子のサイズを抑える技術を提供することを目的とする。

【解決手段】エピタキシャル層2の表面にベース領域(P不純物層4)が形成され、P不純物層4の表面にエミッタ領域(N+不純物層5)が形成され、エピタキシャル層2とN+不純物層6とから成るコレクタ領域が構成されている。ベース電極8とベース領域(P不純物層4)の接続部が、ベース領域(P不純物層4)のコレクタ電極10側の端部とエミッタ領域(N+不純物層5)との間に位置する。つまり、コレクタ・ベース・エミッタの順で各電極が構成されている。ベース電極8とエミッタ電極9とは不図示の配線を介して接続されている。また、エピタキシャル層2を複数の島領域に分離するためのP+分離層11が形成されている。

(もっと読む)

3次元クロスバーアレイシステム、並びに3次元クロスバーアレイ接合部に情報を書き込む方法及び3次元クロスバーアレイ接合部に格納された情報を読み出す方法

本発明の様々な実施形態は、3次元クロスバーアレイ(500,1000)を対象とする。本発明の一態様では、3次元クロスバーアレイ(1000)は、複数のクロスバーアレイ(1102〜1104)と、第1のデマルチプレクサ(1106)と、第2のデマルチプレクサ(1108)と、第3のデマルチプレクサ(1110)とを含む。各クロスバーアレイは、ナノワイヤ(702〜704)の第1の層、ナノワイヤの第1の層に重なるナノワイヤ(706〜708)の第2の層、及びナノワイヤの第2の層に重なるナノワイヤ(710〜712)の第3の層を含む。第1のデマルチプレクサは、各クロスバーアレイのナノワイヤの第1の層におけるナノワイヤをアドレス指定するように構成され、第2のデマルチプレクサは、各クロスバーアレイのナノワイヤの第2の層におけるナノワイヤをアドレス指定するように構成され、第3のデマルチプレクサは、各クロスバーアレイのナノワイヤの第3の層におけるナノワイヤに信号を供給するように構成される。 (もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の耐湿性向上を図ることができる技術を提供する。

【解決手段】半絶縁性基板であるGaAs基板40において、素子形成領域にHBT30を形成し、絶縁領域に素子分離領域47を形成する。絶縁領域に形成される素子分離領域47は、HBT30のサブコレクタ用半導体層41とコレクタ用半導体層42と同層の半導体層にヘリウムを導入することにより形成されている。外周領域において、保護膜52、55から露出するように導電層49を形成し、この導電層49を裏面電極と接続する。裏面電極にはGND電位が供給されるので、導電層49はGND電位に固定される。この導電層49は、HBT30のサブコレクタ用半導体層41とコレクタ用半導体層42と同層の半導体層により形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置

【課題】保護トランジスタを備える半導体装置において、保護トランジスタの動作均一性の向上を図ると共に、保護トランジスタの素子面積の増大を招くことなくESDサージから内部回路を保護することである。

【解決手段】半導体基板上に形成されたバイポーラトランジスタ100を備える半導体装置であって、半導体基板におけるバイポーラトランジスタ形成領域上に配置された複数の電流制御部107を備え、複数の電流制御部107の各々は、バイポーラトランジスタ100を構成するベース層102とエミッタ層103とを電気的に接続している。

(もっと読む)

個別電子コンポーネントのマトリクスを形成する方法および形成されるマトリクス

本発明は、基板(100)上にアクティブ層(101)を形成する段階および少なくとも基板(100)が出現するまで、トレンチ(102)をアクティブ層(101)内に形成することでコンポーネントを個別化する段階を含む、電子コンポーネント(111)のマトリクスを製造する方法に関する。この方法は、アクティブ層(101)上に機能材料の層(102)を蒸着する段階と、前記トレンチ(102)を充填し、電子コンポーネント(111)の上側面に薄膜(115)を形成するように、材料の層(103)上に感光性樹脂(104)を蒸着する段階と、トレンチの樹脂の部分の露光を少なくしつつ樹脂(104)を放射線に少なくとも部分的に曝露する段階と、適切に露光された部分を除去するように樹脂(104)を現像する段階と、現像段階の後、外面に現われる機能材料の層(103)の部分を除去する段階と、樹脂の残り部分を除去する段階とを含む。  (もっと読む)

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

半導体装置及びその検査方法

【課題】複数の絶縁分離トレンチの一部に欠陥がある場合でも検出が可能な半導体装置及びその検査方法を提供する。

【解決手段】基板110に形成された複数の絶縁分離トレンチ120(121〜124)により、素子領域130が多重に囲繞された半導体装置100であって、基板110は、隣接する絶縁分離トレンチ間に構成されるトレンチ間領域140を少なくとも1つ有しており、素子領域130、トレンチ間領域140(141〜143)、フィールド領域150の各領域は、絶縁分離トレンチ120の欠陥検査前の状態で、間に絶縁分離トレンチ120を2つ挟む位置関係にある領域同士が同一の電極パッドに電気的に接続されるように、各領域が2つの電極パッド160,161のいずれか一方に電気的に接続されており、絶縁分離トレンチ120の欠陥検査後の状態で、各領域がそれぞれ電気的に分離されている。

(もっと読む)

半導体装置

【課題】半導体チップに複数の半導体素子が形成されている半導体装置において、従来の半導体装置と比較して、半導体チップの面積を縮小できる半導体装置を提供する。

【解決手段】半導体チップの表面に平行な面方向において、パワー素子領域aよりも領域が狭い制御回路素子領域bがパワー素子領域aと完全に重複するように、半導体チップの内部に、絶縁分離されたパワー素子領域aを有する第1のSOI層4と、絶縁分離された制御回路素子領域bを有する第2のSOI層7とを、半導体チップの表面に垂直な方向に並んで配置させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】

全セルが均一動作せずに、一部のセルの温度上昇により生じる熱暴走による素子の破壊を抑止し、安定した高出力動作が可能なトランジスタチップを提供する。

【解決手段】

それぞれが、制御信号が入力される制御端子121と制御信号に従って電流が流れる第1及び第2端子111、131とを備える、複数のトランジスタ素子と、それぞれが、トランジスタ素子が形成された領域10と異なる領域20に形成され、第1端子の基板141への導通を与える、複数の基板導通部232と、を備え、各異なるトランジスタ素子は、異なる基板導通部232と接続され、各基板導通部232は、他の基板導通部232から分離された半導体層を備える、半導体装置。

(もっと読む)

半導体装置

【課題】 半導体装置において、反転領域対策を、既存の製造工程の条件を変えないで実現することを課題とする。

【解決手段】 N型エピタキシャル層4上にP型拡散層よりなる抵抗素子5が形成してあり、N型エピタキシャル層4上にシリコン酸化膜40が形成してあり、抵抗素子5の端から出ているアルミニウム配線8,9がシリコン酸化膜40上を延在している。シリコン酸化膜40は、N型エピタキシャル層4内に食い込んで厚みが増してある厚み付加部分42を枠状に有する。厚み付加部分42は、シリコン酸化膜40の反転電圧を上げる。厚み付加部分42は酸素イオンの注入及びアニール処理によって形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】回路領域間のノイズ伝搬を好適に抑制することのできる半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板10上のアナログ−デジタル回路領域間には、ダミー拡散層14の配置された回路分離領域が形成されている。ダミー拡散層14には、その形成基材となるpウェル12とは逆の導電型であるn導電型の不純物が導入され、またその上表面Sbは、シリコン基板10の主表面Saからシリコン基板10の内部に掘り下げられている。

(もっと読む)

化合物半導体エピタキシャルウェハ

【課題】HBT、HEMTという異種類のトランジスタを、極めて小さい接続抵抗の下で接続した構成を持つ化合物半導体エピタキシャルウェハを提供すること。

【解決手段】同一ウェハ内で、一単位のHBTエピタキシャル層(HBT構造40)の上に一単位のHEMTエピタキシャル層(HEMT構造50)を積層した構造とする。

(もっと読む)

1 - 20 / 22

[ Back to top ]