Fターム[5H430JJ04]の内容

トランジスタを用いた連続制御型電源 (9,660) | 帰還部全体 (266) | 帰還量の変更、異なる帰還の組合せ (109)

Fターム[5H430JJ04]に分類される特許

1 - 20 / 109

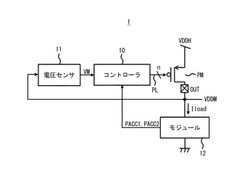

半導体集積回路

【課題】従来の半導体集積回路のレギュレータ回路では、出力電圧の制御精度を十分に高めることができない問題があった。

【解決手段】本発明の半導体集積回路は、制御端子に与えられるインピーダンス制御信号で示される制御値PLに応じて負荷電流Iloadの大きさに対する出力電圧VDDMの大きさを制御する複数の出力トランジスタPMと、出力電圧VDDMの電圧値を示す出力電圧モニタ値VMを出力する電圧モニタ回路12と、出力電圧VDDMの目標値を示す参照電圧Vrefと、出力電圧モニタ値VMと、の間の誤差値の大きさに応じて制御値PLの大きさを制御し、当該制御値PLにより複数の出力トランジスタPMいずれを導通状態とするかを制御する制御回路10と、を有し、制御回路10が負荷電流Iloadの変更を事前に通知する事前通知信号PACCに応じて、誤差値に対する制御値の変化ステップを一定期間の間大きくする。

(もっと読む)

安定化電圧電源回路

【課題】比較的簡易な回路構成で、逆電流の発生を確実に防止する。

【解決手段】基準電圧Vrefと、出力電圧VOUTに応じたフィードバック電圧の差がエラーアンプ10により検出され、エラーアンプ10の検出出力に応じて、出力段を構成するバイポーラパワートランジスタ3の動作がドライバを介して制御され、出力電圧VOUTの安定化が図られるよう構成されてなる安定化電圧電源回路において、バイポーラパワートランジスタ3のコレクタに外部から印加される入力電源電圧VINと、出力電圧VOUTの電位差を比較する比較器101が設けられ、比較器101は、入力電源電圧VINと出力電圧VOUTの電位差に応じて、入力電源電圧VIN>出力電圧VOUTが保持されるように、バイポーラパワートランジスタ3のベース電流を制御可能に構成されたものとなっている。

(もっと読む)

電圧制御回路

【課題】定電圧を出力する電圧制御回路において、簡易な構成により、電流を吸い込みながら安定した正電圧を出力する。

【解決手段】負電圧シリーズレギュレータ12を備えた電圧制御回路10において、帰還端子12Eに抵抗18を介してバイアス電圧VBを投入するバイアス電源14を設ける。また、出力端子12Dとグラウンドの間に分圧回路16を設け、分圧出力を帰還端子12Eに供給する。そして、バイアス電圧VBを、帰還端子12Eの基準電圧(電圧レベル)VADJよりも低い負電圧に定め、負の基準電圧より大きい正電圧を出力端子12Dと帰還端子12Eの間に生成させるような大きさの電流を流す。

(もっと読む)

電源回路

【課題】回路規模を増大させることなく、要求に応じた複数の電源を選択的に生成すること。

【解決手段】本発明にかかる電源回路は、出力電圧VOUTAを分圧する第1のフィードバック回路と、出力電圧VOUTBを分圧する第2のフィードバック回路と、第1及び第2のフィードバック回路から出力される分圧電圧のいずれかを切替制御信号に基づいて選択し、出力する第1の選択回路と、第1の選択回路によって選択された分圧電圧と、基準電圧と、を比較し、比較結果に応じた電圧を出力するオペアンプ1と、オペアンプ1の出力電圧に応じた出力電圧VOUTAを生成するトランジスタMN1と、オペアンプ1の出力電圧に応じた出力電圧VOUTBを生成するトランジスタMN2と、切替制御信号に基づいて選択されたトランジスタMN1、MN2のいずれかのゲートに対し、オペアンプ1の出力電圧を出力する第2の選択回路と、を備える。

(もっと読む)

半導体回路装置

【課題】

半導体回路装置に内蔵された内部回路に供給する動作電圧について、内部回路に対する動作モードの変更に伴う動作電圧の安定期間を待つことなく、動作モード変更時でも動作開始時刻を速くすることが可能な構成を有する半導体回路装置を提供する。

【解決手段】

上記の課題を解決するため、外部電源から電圧供給を受ける電源線と、回路群と、回路群の動作電圧が異なる複数の動作モードに応じた制御信号を出力する制御回路と、回路群と、電源線とに電気的に接続し、回路群に前記電源線の電圧以下の電圧を供給する電源供給回路と、を備え、動作モードの変更後において、高い動作電圧を回路群が必要とする場合、電源供給回路は、高い動作電圧より高い電圧を回路群に供給した後、制御信号に応じて、変更後の動作モードに必要な動作電圧を供給する半導体回路装置を提供する。

(もっと読む)

半導体集積回路およびそれを備えた電子機器およびその制御方法

【課題】より少ない消費電力で信号処理装置の動作モードを安定的に変更する。

【解決手段】制御回路(30)は、レギュレータ回路(10)の出力電圧(Vout)で動作する信号処理装置(20)に対する動作モードの変更要求(MODE)を受け、レギュレータ回路(10)の出力電圧(Vout)を変更し、その後、変更要求(MODE)に従って信号処理装置(20)の動作モードを変更する。

(もっと読む)

安定化電源回路

【課題】直流電圧源の電圧を安定化して出力する安定化電源回路において、入力電圧が低い場合でも安定動作できるようにし、かつ構成部品の特性ばらつきに起因する電圧ばらつきを抑え、高精度の安定化電源回路を提供する。

【解決手段】第1のPNP型トランジスタ1のエミッタを直流電圧源であるDC電源部3の正出力端子に接続するとともにベースに基準電圧部4を接続し、第3のPNP型トランジスタ8のエミッタを第1のPNP型トランジスタ1のコレクタに接続し、電圧検知部11により第3のPNP型トランジスタ8のコレクタ電圧を分圧して出力し、DC電源部3と電圧検知部11と第1のPNP型トランジスタ1のベースと基準電圧部4に電圧調整部12を接続する。この電圧調整部12は、電圧検知部11の出力電圧に応じて電圧検知部11の検知電圧が第1の所定電圧となるように出力電圧を調整するよう構成する。

(もっと読む)

定電圧回路

【課題】出力電流が微小電流から大電流まで広範囲に変化した場合でも、安定した動作を行うことができる定電圧回路を得る。

【解決手段】誤差増幅回路3の動作を安定させるために、誤差増幅回路3の入力と出力との間の位相差を補正する可変抵抗をなすNMOSトランジスタM21とコンデンサC21を有する位相補償回路4が、出力端子OUTから出力される出力電流IOUTの検出を行い、該検出した電流値の変化に対するNMOSトランジスタM21のオン抵抗の変化が所定の関係をなすように、検出した出力電流IOUTの電流値に応じてNMOSトランジスタM21のオン抵抗の抵抗値r21を変えるようにした。

(もっと読む)

電圧レギュレータ

【課題】出力電圧を低くしても、位相余裕の減少を防止できるとともに、出力の立ち上りの遅れを改善することのできる電圧レギュレータを提供する。

【解決手段】抵抗R1と抵抗R2による出力電圧VOUTの分圧点の電圧と基準電圧源1から出力される基準電圧VREFとを比較して出力電圧VOUTを一定に保つよう演算増幅器11が制御する電圧レギュレータの位相補償用抵抗Rxを、出力電圧VOUTの分圧点と基準電圧VREFと同じ値の基準電圧VREFxを出力する基準電圧源2の出力端子との間に接続する。

(もっと読む)

電圧レギュレータ回路

【課題】突入電流、及び、オーバーシュートを低減すること。

【解決手段】本発明の電圧レギュレータ回路30によれば、電源が投入されたとき、スイッチSW1は制御信号CTR1(High)に応じてオンし、スイッチSW2はオフし、差動増幅回路AMP1の第1の入力(+IN)と第2の入力(−IN)には同一の電圧として基準電圧Vrefが供給される。第1の入力(+IN)と第2の入力(−IN)に供給される電圧が同一であるとき、高位側電源電圧VDDを供給する高位側電源[VDD]から差動増幅回路AMP1を介して平滑コンデンサC1に流れる電流Iは小さな値に制限される。つまり、突入電流を低減することができる。また、本発明の電圧レギュレータ回路30によれば、差動増幅回路AMP1から出力される出力電圧Voutの上昇も緩やかとなるため、オーバーシュートを低減することができる。

(もっと読む)

定電圧回路

【課題】 突入電流のピークを通常動作時用に設定された制限電流よりも低くすることで起動時に周辺回路・装置に悪影響を与える恐れの少ない定電圧回路を提供する。

【解決手段】 パワートランジスタMptに流れる電流をカレントミラー回路13と電流検出回路14で検出し、それが予め設定された値以上になった場合、電流の大きさに応じた電流検出信号Scdを補正回路16に供給する。補正回路16において、パワートランジスタMptに供給される駆動信号Sdrvを電流検出信号Scdの大きさに応じて減少させる。起動時においては、レベル切換回路15が電流検出回路14に電流検出信号Scdのレベルを大きくさせ、補正回路16における駆動信号Sdrvの減少量を通常運転字よりも大きくさせる。

(もっと読む)

電源装置

【課題】さらに、出力電圧のオフセットのばらつきを抑制し、安定した電力供給を行うことが可能な、電源装置を実現する。

【解決手段】電源装置510は、ドレイン端子が、出力回路109に接続されているnトランジスタM103と、ドレイン端子が、nトランジスタM103のドレイン端子に接続されており、ゲート端子が、駆動電圧出力線L101に接続されているnトランジスタM104と、nトランジスタM103のゲート端子と、駆動電圧出力線L101と、の間に設けられたスイッチ103と、を備える。スイッチ103は、nトランジスタM103のゲート端子を、駆動電圧出力線L101に、接続するか否かを、電源装置510の動作状況に応じて切り替える。

(もっと読む)

定電圧回路

【課題】 回路構成の改良により帰還制御ループの位相余裕を大きくし、もって定電圧電源の安定性を向上させる。

【解決手段】 エラーアンプEAの入力側に第1のソースフォロワ回路3を追加設置し、第1位相補償回路1と第2の位相補償回路2によって帰還信号に対して位相補正を施す回路位置を、第1のソースフォロワ回路3の入力側と出力側とに分離する。このような構成とすることで、第2の位相補償回路2が帰還信号に対して位相補正をする位置のインピーダンスを第1のソースフォロワ回路3によって変化させ、第2の位相補償回路2による位相補正作用を向上させる。

(もっと読む)

電圧供給回路

【課題】同時に2つ以上の負荷回路への電圧供給を必要としない場合に、回路の小型化が可能で、電圧出力の高速な立ち上げが可能な電圧供給回路を提供する。

【解決手段】電圧供給回路において、基準電圧発生回路は、基準電圧を発生する。オペアンプ回路は、基準電圧に基づいて出力電圧を生成する。選択回路は、少なくとも2つの第1端子を有し、制御部からの制御信号に基づいて制御され、第1端子のうちいずれか1つを選択し、選択された第1端子を介して通過した出力電圧を表す通過出力電圧を生成する。第2端子は、通過出力電圧を受け、負荷回路へ出力可能である。検出回路は、通過出力電圧の大きさを検出し、検出電圧を生成する。選択回路は、制御信号に基づいて制御され、少なくとも2系統の検出電圧のうち、通過出力電圧に対応する電圧を選択し、選択された検出電圧を生成する。オペアンプ回路は、基準電圧と選択された検出電圧との差を小さくする。

(もっと読む)

レギュレータ用半導体集積回路

【課題】出力電流がリミット値に達したときに出力電流を俊敏に制限することができる電流制限回路を備えたレギュレータ用ICを提供する。

【解決手段】電圧制御用トランジスタ(M1)とその制御回路と電流制限回路とを備えたレギュレータ用ICにおいて、電圧制御用トランジスタに流れる電流に縮小比例した電流を流すモニタ用トランジスタ(M2)と、該モニタ用トランジスタと直列に接続された電流−電圧変換手段(M4)と、該電流−電圧変換手段により変換された電圧に応じた電流を流す第3トランジスタ(M5)と、前記モニタ用トランジスタに流れる電流が所定以上になった場合に電流−電圧変換手段に電流が流れ始めるように電流を制御する電流制御手段(M6)とを備え、前記第3トランジスタが誤差アンプから電流を引くことによって電圧制御用トランジスタ(M1)に流れる電流を減少させるようにした。

(もっと読む)

定電圧回路

【課題】ステップ状のフの字特性の過電流保護回路を備えた定電圧回路における、負荷罫線に交わることがないステップ状のフの字特性の実現を、可能とする。

【解決手段】出力端子からの出力が第1,第2の制限電圧になった際に、対応するNMOSトランジスタM11,10をオフにする電圧を生成してゲートに入力する制限電圧設定回路5を備える。この制限電圧設定回路5は、PMOSトランジスタM22と、ディプレッション型NMOSトランジスタM24と、M22とカレントミラー回路を構成するPMOSトランジスタM23と、ディプレッション型NMOSトランジスタM25と、このM25のドレインとM10のゲート間に接続されたインバータINV1とを備え、第1,第2の制限電圧の値を、M24に対するM25のサイズによるオフセットか、M22に対するM23のサイズによるオフセットで設定する。

(もっと読む)

昇降圧電源制御装置および昇降圧電源制御方法

【課題】 本発明は、入力電圧(VIN)が変動する場合において、入出力電圧間の電圧変換動作を最適化して不要な電圧変換動作を抑制することで低消費電力化を図ることが可能な昇降圧電源制御装置を提供することを目的とする。

【解決手段】 本発明は、入力電圧を入力し、昇圧電圧を出力する昇圧部と、昇圧電圧を入力し、昇圧電圧が第1トランジスタにおいて電圧降下することにより、出力電圧を出力する降圧部とを有する昇降圧電源制御装置である。昇圧部は、入力電圧が、出力電圧より高い第1基準電圧を下回る場合、昇圧電圧の電圧値を出力電圧の電圧値より高く出力し、入力電圧が第1基準電圧を上回る場合、昇圧電圧の電圧値を前記入力電圧の電圧値と同じにして出力する。降圧部は、入力電圧が出力電圧より低い第2基準電圧を上回る場合、第1トランジスタの非飽和領域でオン抵抗を制御する。入力電圧が第2基準電圧を下回る場合、第1トランジスタを飽和領域で使用する。

(もっと読む)

レギュレータ回路

【課題】従来のレギュレータ回路は、低い出力電圧を出力する場合に出力トランジスタの内部損失が大きくなる問題があった。

【解決手段】本発明にかかるレギュレータ回路は、第1の電源電圧Vcc1を降圧して第2の電源電圧Vcc2を生成する直流電圧変換回路11と、第1の電源電圧Vcc1に基づき動作し、出力端子OTから出力される出力電圧Voutに応じて変動する帰還電圧と第1の基準電圧Vref1とを比較して出力制御信号Verrを出力するエラーアンプ12と、ドレインに第2の電源電圧Vcc2が供給され、ソースが出力端子OTに接続され、ゲートに出力制御信号Verrを受けるN型MOSトランジスタと、を有する。

(もっと読む)

リニアレギュレータ回路及び半導体装置

【課題】出力トランジスタの特性に関わらず、PSRRの低下を抑止するレギュレータ回路を提供する。

【解決手段】リニアレギュレータ回路10は、出力トランジスタTr1に流れるトランジスタ電流Itを検出して該出力トランジスタTr1に流れるトランジスタ電流Itに相対した電流検出電圧Vkを出力する電流検出部11と、第1誤差増幅器ERR1の出力端子と出力トランジスタTr1のゲートとの間に、出力トランジスタTr1に流れるトランジスタ電流Itに相対した電流検出電圧Vkと誤差信号Sgとの電圧差に基づく駆動信号Sdを出力トランジスタTr1のゲートに出力して、出力トランジスタTr1に流れるトランジスタ電流Itを誤差信号Sgに相対した電流値にするように動作する第2誤差増幅器ERR2を介在させる。

(もっと読む)

電流制限回路及び電流制限回路の駆動方法

【課題】実際に出力する電流の最大値と電流の制限値との差をより小さくできる電流制限回路を提供する。

【解決手段】電流制限回路は、ドライバトランジスタ(M1)と、センス抵抗(Rsns)を介して入力端子(IN)に一端が接続され、他端が出力端子(OUT)に接続され、制御端子がドライバトランジスタ(M1)の制御端子に接続されたセンストランジスタ(M2)と、入力端子の電位を基準電位とするバイアス電圧(Vbais)と、センス抵抗の電圧降下とを入力し、ドライバトランジスタとセンストランジスタの制御端子に出力が接続された演算増幅回路(1)を備える。電流制限回路は、バイアス電圧の電圧値を、入力端子と出力端子の差電圧に応じて、所定のバイアス電圧以下になるように制御するバイアス電圧変更回路(10)をさらに備える。

(もっと読む)

1 - 20 / 109

[ Back to top ]