Fターム[5J022CE01]の内容

アナログ←→デジタル変換 (13,545) | タイミング調整・計数系 (1,285) | 動作タイミング調整(クロック制御) (659)

Fターム[5J022CE01]の下位に属するFターム

動作時間長・間欠動作制御 (325)

Fターム[5J022CE01]に分類される特許

1 - 20 / 334

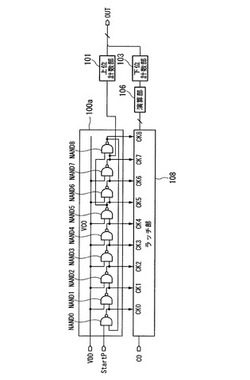

AD変換回路および撮像装置

【課題】エンコードエラーの発生を抑圧することができるAD変換回路および撮像装置を提供する。

【解決手段】VCO100aの出力信号CK0〜CK8のうち出力信号CK7が上位計数部101のカウントクロックとなる。演算部106は、出力信号CK7を基準として定義される出力信号CK0〜CK8の状態(状態0〜状態7)を検出するため、各出力信号の論理状態の変化位置を検出し、検出された変化位置に基づいて下位計数信号を生成する。演算部106がこの変化位置を検出する際の手順では、立下りエッジが略同時になる出力信号CK0と出力信号CK7の論理状態の比較は行われない。このため、エンコードエラーの発生を抑圧することができる。

(もっと読む)

タイムインタリーブ型サンプラのアレイを有する無線周波数(RF)サンプリング装置およびシナリオベースの動的資源割り当てのための方法

【課題】RFサンプリングシステムの動的資源割り当てのための方法および装置を提供すること。

【解決手段】

受信した無線周波数(RF)信号から、タイムインタリーブされた複数のサンプルを生成し、そのタイムインタリーブされた複数のサンプルを組み合わせて信号品質を生成することにより決定された信号品質測定値に基づいた、RFサンプリングシステムの動的資源割り当てのための方法および装置。

(もっと読む)

半導体装置、固体撮像装置、およびカメラシステム

【課題】隣接ビアを伝送される信号間の干渉を低減でき、ひいてはビア数の増大を抑止でき、センサを搭載したチップの面積、実装工程を低減でき、結果的にコスト削減を図ることができる半導体装置、固体撮像装置、およびカメラシステムを提供する。

【解決手段】第1チップ110と、第2チップ120と、を有し、第1チップ110と第2チップ120は貼り合わされた積層構造を有し、第1チップと第2チップ間の配線は、ビア114を通して接続され、第1チップ110は、各センサ111で発生したアナログ信号を時間離散化した信号が、対応するビアを介して第2チップに伝送され、第2チップ120は、ビアを介した第1チップから伝送された信号を第1チップでサンプリングしたタイミングとは異なるタイミングでサンプリングする機能と、量子化してデジタル信号を得る機能と、を含む。

(もっと読む)

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

タッチパネルコントローラおよびそれを用いた入力装置、電子機器

【課題】相互キャパシタ方式の入力装置の検出感度を改善し、または、センシング時間を短縮する。

【解決手段】送信回路20は、1回のセンシングごとに送信電極10に複数のパルス信号を含む送信信号S1を印加する。A/Dコンバータ44は、各パルス信号のポジティブエッジごとに、演算増幅器32の出力電圧に応じた検出電圧Vsをデジタル値に変換することにより第1データ系列DRを生成するとともに、各パルス信号のネガティブエッジごとに、検出電圧Vsをデジタル値に変換することにより第2データ系列DFを生成する。DSP102は、第1データ系列DRと第2データ系列DFそれぞれに含まれる、互いに対応するデジタル値の差分を算出し、各デジタル値の差分を積分する。

(もっと読む)

電子制御装置

【課題】マルチプレクサの切り替えによってフィルタ回路の収束時間が変化したとしても正確な出力信号を取得することができる電子制御装置を提供する。

【解決手段】電子制御装置は、複数の信号を選択的に出力信号として出力するマルチプレクサ27を備えている。また、マルチプレクサ27の後段に接続され、マルチプレクサ27が前回出力した出力信号が示す電圧値とマルチプレクサ27が今回出力した出力信号が示す電圧値との電圧差に応じた収束時間で今回の出力信号を出力するフィルタ回路28を備えている。さらに、マルチプレクサ27の切り替え制御を行ってフィルタ回路28から出力信号を取得するマイコン24を備えている。そして、マイコン24は、マルチプレクサ27の切り替えにおけるフィルタ回路28の収束時間に合わせて、マルチプレクサ27の接続先毎に異なる切り替え時間を設定する。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

信号処理装置

【課題】複数のAD変換器を用いて同一のアナログ信号をAD変換する信号処理装置において、個々のAD変換器の特性のばらつきによって生じる同一のアナログ信号のAD変換精度の低下を抑制する。

【解決手段】クロック生成部58はπ[rad]位相の異なる二つのクロックを生成し、対象信号供給部52は受信信号RSまたは0VのいずれかをAD変換部68の二つのAD変換器72、74に供給する。被補正データ生成部86は、AD変換部68が受信信号RSをAD変換した結果に基づき、読出データRDを生成する。オフセットデータ生成部76は、AD変換部68が基準電圧をAD変換した結果に基づき、AD変換器72、74毎の測定誤差を表すオフセットデータAZ1、AZ2を生成する。補正部100は、読出データRDからオフセットデータAZ1、AZ2分を除去する補正処理を実行し、サンプリングデータSDを生成する。

(もっと読む)

ADC

【課題】アナログ入力信号に対する周波数の制限を抑制したバックグランドキャリブレーションを行うADCとその補正回路を提供する。

【解決手段】アナログ入力信号をサンプリング周波数(以下fs)でサンプリングしてデジタル出力信号に変換するADCであって,アナログ入力信号をタイムインタリーブでデジタル出力信号に変換するN個のアナログデジタル変換(以下ADC)チャネルと,N個のADCチャネルがそれぞれ出力するチャネルデジタル信号を合成して前記デジタル出力信号を生成するチャネル合成器と,N個のADCチャネルの少なくとも一つの出力に設けられた適応フィルタと,デジタル出力信号に応じて前記適応フィルタの係数を生成する補正回路とを有し,補正回路は,デジタル出力信号に含まれるアナログ入力信号成分と誤差に対応するイメージ信号成分のうち,イメージ信号成分の直流成分を演算し,直流成分に基づいて当該直流成分が抑制されるように前記係数を演算する。

(もっと読む)

固体撮像装置

【課題】画素数の増大に伴うバッファの数の増大、微細化に伴うプロセスばらつきの増大により、このクロック信号のデューティ比の崩れを抑制する。

【解決手段】固体撮像装置1は、複数の画素10がアレイ状に配置された画素部20と、少なくとも一つのアナログデジタル変換部30を含む第1グループおよび第2グループを有する変換部と、直列に接続された第1のクロックバッファおよび第2のクロックバッファを有するクロック供給部とを含み、第1グループおよび第2グループのアナログデジタル変換部のそれぞれは、比較部およびカウンタ部を有し、第1のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して、第1グループのカウンタ部のそれぞれと第2のクロックバッファに出力し、第2のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して第2グループのカウンタ部のそれぞれに出力する。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

ライトセンサ

【課題】応答性を早くすることができるライトセンサを提供する。

【解決手段】センサ信号をデジタル信号に変換する制御部30に、センサ信号と所定の閾値とを比較する比較手段32と、比較手段32の比較結果に基づいてAD変換開始信号を出力する処理手段33と、センサ信号を第1デジタル信号に変換する第1AD変換手段31とを備える。そして、処理手段33に、受光素子が所定期間露光したときの所定期間経過時のセンサ信号を出力制御回路から比較手段32に入力させ、比較手段32の比較結果に基づき、センサ信号が閾値以上のときは第1AD変換手段31にAD変換開始信号を入力してセンサ信号を第1デジタル信号に変換させ、センサ信号が閾値未満のときは出力制御回路に受光素子の出力期間を延長させ、延長期間経過時のセンサ信号を比較手段32に入力させて比較手段32の比較結果に基づいた処理を行わせる。

(もっと読む)

電子制御装置

【課題】 パルス信号を出力しつつ入力信号を取得する電子制御装置において、パルス出力によって生ずる重畳ノイズが入力信号のサンプリングに及ぼす影響を回避する。

【解決手段】 電子制御装置(ECU)のマイコンは、パルス出力(a)を生成する第1タイマ、及び入力信号(b)のサンプリングタイミングを生成する第2タイマを備える。入力信号のサンプリングタイミングがパルス出力のエッジタイミングに一致すると(c)、入力信号は重畳ノイズを強く受けることとなる。そこで、第1タイマおよび第2タイマによって、入力信号のサンプリングタイミングがパルス出力のエッジタイミングに一致しないように調整する(d)。これにより、重畳ノイズが入力信号のサンプリングに及ぼす影響を回避することができる。

(もっと読む)

アナログ−デジタル変換装置及びアナログ−デジタル変換方法

【課題】 複数の受信経路から供給されるアナログ信号を一装置でデジタル化することで、受信装置の大型化を回避でき、かつ、量子化雑音の増大を抑えることが可能なアナログ−デジタル変換装置を提供する。

【解決手段】 アナログ−デジタル(A/D)変換装置は、バンド選択部、第1及び第2の切替部、A/D変換部及びチャネル選択部を具備する。バンド選択部は、複数の入力チャネルからアナログ信号を受信し、各アナログ信号から所定の帯域幅で信号を抽出する。第1の切替部は複数の入力チャネルの受信経路との接続を切り替え、複数の抽出信号を多重する。A/D変換部は、第1の切替部から出力される多重信号を、所定サンプリング周波数でデジタル信号へ変換する。第2の切替部は、複数の送信経路との接続を順次切り替え、受信経路と対応する送信経路へデジタル信号を出力する。チャネル選択部は、供給されたデジタル信号を、所定のサンプルタイミングでリサンプルする。

(もっと読む)

データ・コンバータ・システム

【課題】データ・コンバータ・システムの出力信号中のスプリアス・トーンを減少させる。

【解決手段】入力信号を特定周波数帯域に制限し、オーバー・サンンプリングすることによって、変換された入力信号がスプリアス・トーンを跨ぐ又は回避するようにする。スプリアス・トーンはフィルタで除去しても良く、これによって、従来のデータ・コンバータよりきれいなSFDRの出力信号を供給できる。例えば、インタリーブ・データ・コンバータ・システムは、インタリーブされた複数のデータ・コンバータの1つの第2ナイキスト領域に制限された入力信号をインタリーブされた信号に変換し、このインタリーブ信号を、変換された入力信号周波数を通過させる通過帯域と、スプリアス・トーンを減衰させるストップ帯域とを有するフィルタでフィルタする。

(もっと読む)

比較器及びAD変換器

【課題】高速に、かつ高精度で動作する比較器及びADC等を構築すること。

【解決手段】従来の比較器は、比較器に入力される2つの入力電圧の差が小さいほど、安定した比較結果を得るまでに時間がかかり、また、2値の出力しか得られない。安定した比較結果が得られるまでの状態を、通常メタステーブル状態と呼んでいる。本発明は、このメタステーブル状態を積極的に利用する。すなわち、メタステーブル状態を検出することで、ハイとロウの中間レベルの判定を合わせて行える。これによって、3値以上を出力する比較器が容易に実現できる。本発明の比較器は、比較器の数を減少させることができると同時に、通常では判定が終了していない状態で比較動作を終了させることが可能になるため、速度向上にも役立ち、高速、高精度のADC(アナログデジタル変換器)等の機器に応用できる。

(もっと読む)

A/D変換装置、A/D変換方法および固体撮像装置

【課題】出力分解能を犠牲にすることなく、消費電力を低減することができるA/D変換装置、A/D変換方法および固体撮像装置を提供する。

【解決手段】

アナログ入力信号に応じてパルス信号を遅延させるn(n:正の整数、n≧2)個の遅延素子が円環状に接続され、第1の時刻から第2の時刻までパルス信号を伝播させるパルス遅延回路と、第1の時刻から第2の時刻よりも短い第3の時刻までの周回数をカウントするカウンタ回路と、第3の時刻までの周回数を上位ビットラッチ値として出力する上位ビットラッチ回路と、第3の時刻の位置を第1の下位ビットラッチ値として出力し、第2の時刻の位置を第2の下位ビットラッチ値として出力する下位ビットラッチ回路と、第1の時刻から第2の時刻までの周回数の上位ビット推定値と第2の下位ビットラッチ値とに基づいて、アナログ入力信号の大きさに応じたデジタル出力値を生成するデジタル演算回路と、を備える。

(もっと読む)

撮像装置

【課題】A/D変換回路によるアナログ・デジタル変換動作に伴う消費電力を低減し、かつ、高い精度の変換結果を得ることができる撮像装置を提供する。

【解決手段】画素が行列状に複数配置された画素部と、対応する列の画素信号の大きさに応じた遅延時間でパルス信号を走行させる遅延素子が円環状に複数段連結された複数のパルス走行回路と、対応する1つの遅延素子からの遅延出力信号が入力され、入力信号を反転した第1の反転信号を出力する第1の反転回路と、第1の反転信号を反転した第2の反転信号を出力する第2の反転回路とを具備した複数のラッチ回路と、ラッチ回路による反転動作を制御するラッチ制御回路と、を備え、パルス走行期間に遅延出力信号の反転動作を禁止し、パルス走行期間が終了する前の予め定めたラッチタイミングのときに遅延出力信号の反転動作を許可し、ラッチ期間に第1の反転回路に第2の反転信号の反転動作を行わせる。

(もっと読む)

信号処理装置

【課題】2個のチップを接続する配線本数を削減しつつ、SN比の低下を抑制する。

【解決手段】第1のチップ10は、第2データD2を1ビットの第3データD3に変換するノイズシェーパー14と、第1信号配線L1を介して送信信号YPDMを送信し、第2信号配線L2を介してクロック信号YCLKを送信するPDM送信回路15とを備え、第2のチップ20は、第3データD3を6ビットのデータに変換する移動平均フィルター22と、5ビットの第5データD5を出力するクリップ回路24とDEM−DAC25とを備える。

(もっと読む)

1 - 20 / 334

[ Back to top ]