Fターム[5J055CX12]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 負荷の性質 (266) | 容量性 (44)

Fターム[5J055CX12]に分類される特許

1 - 20 / 44

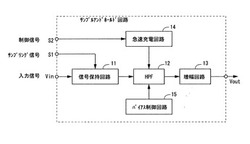

サンプルアンドホールド回路

【課題】ハイパスフィルタ回路を急速充電できるようにして、その起動時間を短くする。

【解決手段】所定のタイミング毎に入力信号を保持する信号保持回路11と、信号保持回路11の出力側に接続された第1のトランジスタQ1の出力側の第1のノードN1に現れる信号から低域成分を除去するハイパスフィルタ回路12と、起動時にのみ動作してハイパスフィルタ回路12のコンデンサC2に対して急速充電を行う急速充電回路14と、ハイパスフィルタ回路12の出力側に接続された増幅回路13と、急速充電回路14による急速充電動作の終了から通常動作に移行する前後で前記第1のノードN1のバイアス電位をほぼ一定に保持するバイアス制御回路15とを備える。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

半導体チップおよびそれを用いた画像表示装置

【課題】画像表示装置の昇圧回路の高効率化を図ることが可能な半導体チップと、それを用いた画像表示装置を提供する。

【解決手段】この携帯電話機では、昇圧回路8のトランジスタ12の前段にバッファ14を設け、バッファ14の入力ノードの寄生容量値をトランジスタ12のゲートの寄生容量値よりも小さく設定し、トランジスタ12およびバッファ14を1つの半導体チップ21に搭載する。したがって、トランジスタ12のゲートにおけるPWM信号φPのレベル変化の鈍りを抑制することができ、昇圧回路の高効率化を図ることができる。

(もっと読む)

半導体スイッチ及び充電回路

【課題】保護回路を内蔵した半導体スイッチ及び充電回路を提供する。

【解決手段】実施形態によれば、スイッチ素子と駆動回路と保護回路と制御回路とを備えた半導体スイッチが提供される。スイッチ素子は、電源線と出力線との間に接続される。駆動回路は、入力信号に応じて前記スイッチ素子をオンまたはオフに駆動する。保護回路は、前記スイッチ素子の過電流を検出したとき前記スイッチ素子の電流を上限値に制限するクランプモードと、前記スイッチ素子を交互にオンとオフとに切り替えるスイッチングモードと、を有する。制御回路は、前記スイッチ素子がオンしたとき前記保護回路を前記クランプモードに制御し、前記スイッチ素子がオンしてから規定時間経過後に前記出力線の短絡を検出したとき、または前記出力線の短絡を検出せずに前記出力線の電圧が規定値に達したとき前記保護回路をスイッチングモードに制御することを特徴とする。

(もっと読む)

容量性負荷の駆動装置、及びその駆動装置を搭載するプラズマディスプレイ装置

【課題】容量性負荷である表示パネルを高い効率で駆動するため、表示パネルに急峻な電圧を印加しながらスイッチング損失やリンギングを抑制することが可能な容量性負荷駆動装置を提供すること。

【解決手段】容量性負荷駆動装置は、負荷容量(Cp)を有する表示パネル(20)と、表示パネルに電力を供給する電力供給源(In)と、表示パネルに電力供給源からの電力の供給/遮断を行うスイッチング部(Q1X,Q2X,Q1Y,Q2Y)と、飽和可能な磁心を持つ可飽和インダクタ(LsX)とを有し、表示パネルに電力を供給するとき、表示パネルと、電力供給源と、スイッチング部と、可飽和インダクタとを、電気的に接続状態とするよう構成されている。

(もっと読む)

容量性負荷駆動回路

【課題】容量性負荷の静電容量と回路抵抗値とから決定される回路時定数が変化することによって生じる容量性負荷の充電速度または放電速度の変化を防止し、所望の駆動波形を得ることが可能な容量性負荷駆動回路を提供する。

【解決手段】容量性負荷駆動回路は、容量性負荷である複数の駆動素子と、複数のコンデンサーと、前記複数のコンデンサーに電力を供給する電源と、前記複数のコンデンサーと前記複数の駆動素子間の接続を切替える切替え手段と、前記切替え手段を制御する制御手段と、を有し、前記制御手段は、前記複数の駆動素子に対して印加される電荷容量の予測値に基づいて、前記切替え手段の接続状態を維持することを特徴とする。

(もっと読む)

容量性負荷駆動回路

【課題】パルス電圧の立ち上がり立ち下がりの急峻性を損なうことなく、容量性負荷への電圧印加位置の移動にともなう容量性負荷の充放電にともなうエネルギー損失を抑えた容量性負荷駆動回路を構成する。

【解決手段】容量性負荷駆動回路101は、正電圧Vcを発生する直流電源10、4つの出力端子V1〜V4、8つの電圧選択用スイッチ素子S1H,S1L,S2H,S2L,S3H,S3L,S4H,S4L 、及びスイッチ制御部12が備えられている。また、4つの出力端子V1〜V4のうち、二つの出力端子間毎に、インダクタL1〜L4及び電荷転送用スイッチ素子S1T〜S4Tを含む電荷転送用直列回路がそれぞれ設けられている。そしてスイッチ制御部12によって電圧選択用スイッチ素子のスイッチングが行われ、複数の出力端子のうち、電圧が切り替わる二つの出力端子間に設けられた電荷転送用スイッチ素子が、当該出力電圧が切り替わる遷移時にオンされる。

(もっと読む)

圧電アクチュエータ用のドライバ

【課題】複数の半導体デバイスを使用する電池駆動のドライバと同程度に効率的な圧電アクチュエータ用のシングルチップドライバを提供する。

【解決手段】圧電アクチュエータ用のドライバは、単一の半導体デバイスとしてパッケージされる、好ましくは単一の半導体ダイの上に形成されるパルス幅変調器33および出力増幅器34を含む。ドライバは、好ましくはプログラム可能な利得を有する出力増幅器34に電力を供給する第1の昇圧コンバータを含む。第1の昇圧コンバータのスイッチングトランジスタのゲートを駆動するための第2の増幅器は、第2の昇圧コンバータによって電力が供給される。圧電アクチュエータ22は、電池駆動の電子デバイスのキーボードまたはディスプレイに対して触覚フィードバックを提供する。

(もっと読む)

多数の容量性センサ素子の静電容量を決定するための回路装置

【課題】 n個の容量性センサ素子(SE1〜SEn)の静電容量を決定するための回路装置であって、それらのそれぞれの静電容量が作動に基づいて変化するものを提供する。

【解決手段】 この回路装置は、少なくとも一つの集電コンデンサー(CS1〜CSm)、参照電圧源(RQ)、少なくとも一つの集電コンデンサーに電気的に連結され、かつそれぞれのセンサ素子の静電容量を決定するために少なくとも一つの集電コンデンサーに存在する電圧を評価する評価装置(AE)、少なくとも一つの制御信号(SS1〜SSk)を発生するための制御装置(MC)、及び参照電圧源に及び少なくとも一つの集電コンデンサーに電気的に連結され、かつ少なくとも一つの制御信号が付与される少なくとも一つの集積回路(IC1〜ICm)を含む。この少なくとも一つの集積回路は、k個の切換スイッチ(WS1〜WSk)を含み、それぞれの切換スイッチがn個のセンサ素子の一つとそれぞれ組み合わされており、それぞれの切換スイッチの切換位置が少なくとも一つの制御信号に依存しており、それぞれの切換スイッチが、それぞれ組み合わされたセンサ素子を第一切換位置で参照電圧源に連結し、かつそれぞれの切換スイッチが電荷移動の目的のためにそれぞれ組み合わされたセンサ素子を第二切換位置で少なくとも一つの集電コンデンサーに連結する。

(もっと読む)

液晶表示装置のソースドライバー回路

【課題】 本発明は、液晶表示装置のソースドライバー集積素子でパワードロップに対する復帰時間を縮める技術を提供する。

【解決手段】本発明によってソースドライバーに適用されるガンマバッファー回路では、差動増幅部と電流ミラー部のモストランジスターらを直接連結しないでダイオード結合型モストランジスターを通じて連結した。これによって、出力端のモストランジスターのゲートの動作範囲がダイオード結合型モストランジスターのドレッシーホールド電圧程度減るようになる。これによって電源端子電圧ドロップ後復帰時間及び接地端子電圧バウンシング後に復帰時間が減って、入力トランジスターのマッチング特性が改善されて、これによってランダムオフセットが低減される。

(もっと読む)

ゲート・プルダウンを備えたMOSFET

スイッチングタイプのDC−DCパワー・コンバータのMOSFETメインスイッチ・トランジスタ(102)のドレインとゲートとの間にプルダウンMOSFET(110)が結合される。プルダウンMOSFET(110)のゲートは、キャパシタ118によってメインスイッチ・トランジスタ(102)のドレインに結合され、抵抗(120)によってメインスイッチ・トランジスタ(102)のソースに接続される。プルダウンMOSFET(110)は、メインスイッチ・トランジスタ(102)にわたる電圧降下への容量性結合によって動作され、ミラー効果によるメインスイッチ・トランジスタ(102)の意図しないターンオンを避ける又は低減するため、メインスイッチ・トランジスタ(102)のゲートをそのソース電位にまたはその近辺に保持するために用いられ得る。

(もっと読む)

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電圧が昇圧規定電圧に達し、その後は小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路100は、制御部10と発振回路20と昇圧部30とを有する。発振回路20は、予め定められた周期のパルス信号を出力する。昇圧部30は、電圧を昇圧する複数個の昇圧回路を備え、制御部10が出力する昇圧信号に応じて電荷量を出力する。制御部10におけるコンパレータ回路13は、昇圧部30から出力される電圧と、予め定められた規定電圧とを比較し、比較結果に応じて昇圧信号Cont4〜Cont1を出力し、昇圧部30からの供給電荷量を制御する。

(もっと読む)

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

ブースト回路およびそれを用いたΔΣ変調器、電子機器

【課題】ブースト回路におけるビットエラーを防止する。

【解決手段】ビットストリーム信号BSINを受け、その振幅をブーストして出力するブースト回路100が提供される。第1クロックブースタ10aは、クロック信号CKを受け、その振幅をブーストする。第2クロックブースタ10bは、反転されたクロック信号CK#を受け、その振幅をブーストする。スイッチ22は、クロックブースタ10a、10bの出力信号CK’、CK#’を受け、ハイレベルである一方を選択する。第1キャパシタC1は、スイッチ22の出力端子にカップリングされる。レベルシフタ28は、ビットストリーム信号BSINのハイレベルを、第1キャパシタC1に生ずる電圧レベルにレベルシフトする。

(もっと読む)

容量性負荷の充放電回路

【課題】ブートストラップ型の容量性負荷充放電回路における動作を安定させること。

【解決手段】容量性負荷の充放電回路は、充放電部と、蓄電素子と、基準電位設定部と、電荷放出部とを有する。充放電部は、容量性負荷の電位がアナログ信号の電位変化パターンに倣って変化するように容量性負荷に対する充放電を行う。蓄電素子は、電源部からの電流によって充電されるとともに容量性負荷に対する充電時の電流源となる。基準電位設定部は、アナログ信号の電位が閾値よりも高い場合に、蓄電素子が有する低電位側端子の電位を、第1基準電位から第1基準電位よりも高い第2基準電位に設定する。電荷放出部は、容量性負荷から充放電部を通じて流れ出た電荷を、低電位側端子を介さずに放出する。

(もっと読む)

容量性負荷の充放電回路

【課題】容量性負荷の充放電回路における省電力効果を高めること。

【解決手段】容量性負荷の充放電回路は、充放電部と、蓄電素子と、電位調整部と、経路選択部とを有する。充放電部は、容量性負荷の電位がアナログ信号の電位変化パターンに倣って変化するように容量性負荷に対する充放電を行う。蓄電素子は、電源部からの電流によって充電されるとともに容量性負荷に対する充電時の電流源となる。電位調整部は、蓄電素子が有する低電位側端子の電位を、アナログ信号の電位よりも所定量低くするように調整する。経路選択部は、容量性負荷からの電荷を電源部と蓄電素子の少なくとも一方に流す回生経路と、容量性負荷からの電荷をグランド側に流す放電経路とを、アナログ信号の電位に応じて選択する。

(もっと読む)

電気負荷駆動回路、電気負荷駆動方法

【課題】容量成分を有する電気負荷を高い電力効率で正確に駆動する。

【解決手段】所定の電圧範囲内で電圧値の漸増と漸減とを繰り返す目標電圧波形を出力し、目標電圧波形の電圧値に応じて複数の電源部を切り替えながら、電気負荷に出力する出力電圧波形を生成する。また、出力電圧波形が目標電圧波形と一致するように負帰還制御する。出力電圧波形が電気負荷の印加電圧に一致すると出力電圧波形を電気負荷に供給し、目標電圧に達すると出力電圧波形と電気負荷とを切断する。こうすれば、電気負荷の容量成分に蓄えられた電力を回収しながら、電気負荷を駆動することができる。また電源を切り替えているために、回路側での電力損失も抑制できる。加えて、目標電圧波形に従って負帰還制御を行っているため、容量成分を有する電気負荷を、適切にしかも効率よく駆動することが可能となる。

(もっと読む)

チャージポンプ回路

【課題】短時間で出力電位が昇圧規定電位に達し、小さいリップル幅を有するチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路1は、制御部10と発振回路20と昇圧部30とを具備する。発振回路20は、予め定められた一定周期のパルス信号を出力する。昇圧部30は、電位を昇圧するn(n≧1)個の昇圧回路を備え、発振回路20から出力されるパルス信号に応じて第1の電荷量を出力する。制御部10は、昇圧部30から出力される電位と、予め定められた規定電位とを比較し、昇圧部30から出力される電位が一旦規定電位より大きくなると、昇圧部30に第1の電荷量より少ない電荷量を出力させる。

(もっと読む)

電圧増幅回路および駆動回路

【課題】低電圧領域でのスルーレートを改善し、低電圧領域から高電圧領域までの全領域において一定以上の高いスルーレートを満たすことができる電圧増幅回路、およびそれを備える駆動回路を提供する。

【解決手段】増幅した電圧を、出力段に構成されているNMOSトランジスタ12のソース端子から出力する電圧増幅回路10であって、一方の端子がNMOSトランジスタ12のゲート端子に接続され、他方の端子がNMOSトランジスタ12のドレイン端子に接続されている電位ブースト用コンデンサ13を備え、NMOSトランジスタ12は、ドレイン端子が回路電源VHAに接続されるとともに、ゲート端子に上記増幅した電圧が供給される。

(もっと読む)

1 - 20 / 44

[ Back to top ]