国際特許分類[H01L29/73]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | トランジスタ型装置,すなわち,供給される制御信号に連続的に応答できるもの (2,282) | バイポーラ接合トランジスタ (1,079)

国際特許分類[H01L29/73]の下位に属する分類

縦型トランジスタ (410)

横型トランジスタ

ヘテロ接合トランジスタ (469)

国際特許分類[H01L29/73]に分類される特許

1 - 10 / 200

積層電池および積層電池システム

【課題】従来の捲回電池は、電池内部の温度の上昇を抑制することが困難であった。電池内部に冷媒を流したパイプ等を設ければ、電池寸法が大きくなる。更には、従来の電池は電池価格に大きな影響を及ぼす負極の量が多く、電池価格の低減を図ることが困難であった。

【解決手段】正極および負極を筒状外装体の軸方向に積層して、正極もしくは負極の一方の電極の外径を外装体の内径より大きくすることにより、正極もしくは負極を外装体に密に接触させることにより、電極の熱伝達の向上を図り、電池の温度上昇を抑制する。更には、負極規制とすることにより高価な水素吸蔵合金の使用量を減らして、電池価格の低減を図る。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの形成領域において半導体層の下部に絶縁層を有する基板が用いられた半導体装置において、バイポーラトランジスタの電流増幅率を向上させる。

【解決手段】バイポーラトランジスタは、半導体層1cに形成されたコレクタ5、ベース7、エミッタ9、ベース用高濃度オーミック拡散層11及びコレクタ用高濃度オーミック拡散層13、並びに半導体層1c上に形成されたゲート絶縁膜15及びゲート電極17を備えている。ベース7は、絶縁層1bに達する深さで形成され、上方から見てゲート電極17と一部重複して形成され、ゲート電極17下でコレクタ5に隣接して形成されている。ベース7は、ベース7側のゲート電極17の端部からコレクタ5側に向かってP型不純物濃度が低くなる濃度傾斜をもっている。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

タンパク質半導体の製造方法、タンパク質半導体、pn接合の製造方法、pn接合、半導体装置の製造方法、半導体装置、電子機器およびタンパク質半導体の導電型の制御方法

【課題】タンパク質半導体の導電型を容易に制御することができるタンパク質半導体の導電型の制御方法、これを利用したタンパク質半導体の製造方法およびpn接合の製造方法を提供する。

【解決手段】アミノ酸残基全体の電荷量を制御することによりタンパク質半導体の導電型を制御し、p型タンパク質半導体あるいはn型タンパク質半導体を製造し、p型タンパク質半導体とn型タンパク質半導体とを用いてpn接合を製造する。アミノ酸残基全体の電荷量の制御は、タンパク質に含まれる酸性のアミノ酸残基、塩基性のアミノ酸残基および中性のアミノ酸残基のうちの1つまたは複数個を自身の性質と異なる性質を有するアミノ酸残基に置換したり、タンパク質に含まれる酸性のアミノ酸残基、塩基性のアミノ酸残基および中性のアミノ酸残基のうちの1つまたは複数個を化学修飾したり、タンパク質の周りを囲む媒体の極性を制御したりすることにより行う。

(もっと読む)

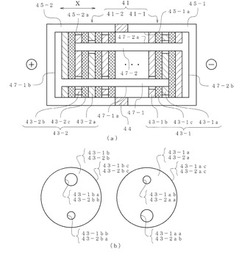

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

1 - 10 / 200

[ Back to top ]