Fターム[2G132AA11]の内容

Fターム[2G132AA11]に分類される特許

1 - 20 / 239

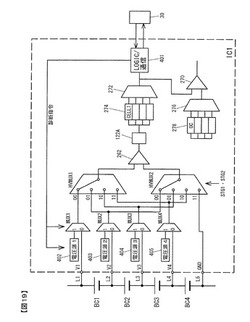

インターフェースボード

電池監視装置

【課題】信頼性の向上を図ることができる電池監視装置の提供。

【解決手段】電池監視装置は、直列接続された複数の電池セル(BC1〜BC4)の各セル電圧値を測定する電圧測定部を有する集積回路IC1と、複数の電池セルの正負両極と集積回路とを接続する複数の電圧計測ラインL1〜L5と、測定された各セル電圧値に基づいて電池セルの状態を監視する制御回路30と、を備え、集積回路は、互いに異なる擬似電圧を生成する擬似電圧生成部402〜405を有し、電圧測定部は、計測対象となる電池セルの正負両極に接続された一対の電圧計測ラインを選択する選択回路HVMUX1,HVMUX2と、選択回路により選択された一対の電圧計測ラインからの電圧を検出する検出回路262,122Aと、を有し、制御回路は、擬似電圧を選択回路に入力し、検出回路により検出された電圧値に基づいて選択回路による選択状態を診断する。

(もっと読む)

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

半導体装置、その検査方法および送信回路

【課題】光結合部の伝送マージンを確保して復調誤りを抑制し、高精度の信号伝送を可能とする半導体装置、その検査方法および送信回路を提供する。

【解決手段】半導体装置100は、アナログディジタル変換部3と、ディジタル信号に応じたパルスパターンである伝送信号を出力するパルス幅変調部5と、固定パルスである参照信号を生成する参照信号生成部7と、を備える。そして、前記伝送信号および前記参照信号のいずれかを選択する第1の制御部13と、前記伝送信号または前記参照信号に基づく駆動電流を出力する発光素子駆動部9と、前記伝送信号または前記参照信号基づく光信号を放出する発光素子15と、を備える。さらに、前記光信号を電圧信号に変換する光受信部21と、前記電圧信号を前記伝送信号または前記参照信号に基づくディジタル信号に復調する復調部25と、を備える。

(もっと読む)

アナログ/デジタル変換回路及び半導体装置

【課題】アナログ/デジタル変換器のより詳細な故障診断のための技術を提供する。

【解決手段】アナログ/デジタル変換回路(100〜108)は、入力されたアナログ信号(x、15)を所要の演算式(f(x))にしたがって診断用に演算する演算部(12)と、前記入力されたアナログ信号(x)又は前記演算部によって演算されたアナログ信号(y)のいずれかを選択する第1選択部(11)と、前記第1選択部によって選択されたアナログ信号をデジタル信号に変換する変換部(10、21、22、23)とを有する。

(もっと読む)

テスト回路

【課題】アナログデジタル変換器の微分直線性を小規模な回路構成に基づいて検査できるようにすること。

【解決手段】テスト回路は、アナログデジタル変換器から出力された第1のデジタル値を格納する第1のレジスタと、アナログデジタル変換器から出力された第2のデジタル値を格納する第2のレジスタと、第1のレジスタに格納された第1のデジタル値と第2のレジスタに格納された第2のデジタルとの差分値を算出する差分算出器と、差分値が所定の上限値と所定の下限値との間に含まれる否かを判定し、判定結果を出力する比較判定器と、を備えている。

(もっと読む)

最適化されたJTAGインターフェイス

【課題】

集積回路内のJTAGタップドメインにアクセスするのに最適化されたJTAGインターフェイスが使用される。限定はしないが、シリアル通信関連集積回路テスト、エミュレーション、デバッグ、および/またはトレース操作等の多様なシリアル通信操作に対してインターフェイスを使用することができる。

【解決手段】

TDI入力端子、TCK入力端子、TMS入力端子、およびTDO出力端子を有し、TDO出力端子は集積回路の外部アクセス可能なデータ入出力ピンに接続されているIEEE 1149.1タップドメインと、集積回路の外部アクセス可能なデータ入出力ピンに接続されたシリアル入力端子、TDI入力端子に接続された第1のパラレル出力端子、およびTMS入力端子に接続された第2のパラレル出力端子を有するシリアル入力パラレル出力回路とを含む、集積回路。

(もっと読む)

アナログデジタル変換回路、アナログデジタル変換回路の検査方法、撮像装置、撮像装置を有する撮像システム、撮像装置の検査方法

【課題】複数のメモリ間でのショート故障の有無を検査できる構成を有するADCおよびその検査方法、ADCを有する撮像装置、撮像装置を有する撮像システムを提供する。

【解決手段】複数のメモリと複数の比較器とを含んで構成される回路部を複数有し、アナログ信号をデジタル信号に変換するアナログデジタル変換回路であって、複数の回路部の一部に含まれるメモリと複数の回路部の別の一部に含まれるメモリとで異なるデジタル信号を保持するようにテスト信号を供給するテスト信号供給部と、出力比較部と、転送部を有することを特徴とするアナログデジタル変換回路である。

(もっと読む)

電子回路

【課題】高い精度で所定の検査を行うことができる電子回路を提供する。

【解決手段】本実施の形態に係る電子回路1は、図1(a)に示すように、主に、主回路2への電圧Vccの供給を切り替えるスイッチ素子としてのp型トランジスタ3と、p型トランジスタ3を駆動する第1の駆動信号を出力する駆動部4と、入力側が駆動部4に電気的に接続され、出力側がp型トランジスタ3に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて第2の駆動信号を出力する第1のインバータ部5と、入力側が駆動部4に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて検査のための検査信号を出力する第2のインバータ部6と、第2のインバータ部6の出力側に電気的に接続され、検査信号を出力する第1のパッドとしての検査パッド7と、を備えて概略構成されている。

(もっと読む)

試験装置

【課題】高速多値信号を試験可能な試験装置を提供する。

【解決手段】パターン発生器PGは、I/O端子PIOに入力される被試験信号S1と比較すべきしきい値電圧Vthを指定する制御データS11を発生するとともに、被試験信号S1としきい値電圧Vthの比較結果の期待値を示す期待値データEXP2を発生する。しきい値電圧発生器10は、制御データS11に応じた電圧レベルを有するしきい値電圧Vthを、第1タイミング信号St1が指定する設定タイミングtVごとに生成する。レベルコンパレータCpは、被試験信号S1の電圧レベルをそれと対応するしきい値電圧Vthと比較する。タイミングコンパレータTCは、レベルコンパレータCpの出力S3を、第2タイミング信号St2が指定するストローブタイミングでラッチし、比較信号S4を生成する。タイミング調節部50は第1タイミング信号St1の位相を調節する。

(もっと読む)

半導体集積回路およびその試験方法

【課題】 半導体試験装置を利用して、短い所要時間でD級増幅器の出力パルスの周波数に関する判定を行うことが可能な半導体集積回路を提供する。

【解決手段】 半導体集積回路1は、D級増幅器100と、セレクタ140と、カウンタ150とを有する。カウンタ150は、セレクタ140によって選択された出力信号OUTPまたはOUTMをモニタ対象パルスとし、リセット信号RSTの解除後、所定個数のモニタ対象パルスをカウントしたときに出力端子からカウント終了信号COを出力する。従って、リセット信号RSTの解除から所定時間経過した後の所定期間内にカウント終了信号COが出力されるか否かを判定することにより、D級増幅器100の出力信号の周波数が適正範囲内にあるか否かを判定することができる。

(もっと読む)

半導体チップ及び半導体チップの検査方法

【目的】高周波数信号を扱う通信回路が構築されている半導体チップを高精度に且つ安価な検査装置で検査することが可能な半導体チップ及び半導体チップの検査方法を提供することを目的とする。

【構成】通信回路を担う複数の機能ブロックが構築されている半導体チップ内に、検査対象とする1の機能ブロックにテスト用周波数信号を供給するテスト信号供給回路と、上記機能ブロックが生成した信号の信号強度を検出して当該信号強度を示す強度信号を外部出力する外部出力回路と、を構築する。

(もっと読む)

表示装置の駆動回路及びそのテスト制御方法

【課題】テスト時に使用するプローブ数が増加する。

【解決手段】表示装置の第1、第2のデータ線をそれぞれ駆動する表示装置駆動回路であって、前記表示装置に表示する第1、第2の表示データとをそれぞれ格納し、第1、第2の信号とをそれぞれ出力する第1、第2のデータレジスタと、前記第1、第2の信号に応じて、第1、第2のアナログ信号をそれぞれ出力する第1、第2のDAコンバータと、前記第1、第2のアナログ信号とに応じて、前記第1、第2のデータ線を駆動する出力端子対と、テスト時に、外部テスト回路からのテスト制御信号に応じて、前記出力端子対の一方に対して、前記第1の表示データに基づく第1のテスト出力と前記第2の表示データに基づく第2のテスト出力とを選択的に出力するスイッチ回路と、前記スイッチ回路を制御する制御回路と、を有する表示装置駆動回路。

(もっと読む)

半導体装置及びその検査方法

【課題】 テスタの高機能化や多ピン化、及び、テスト処理能力の低下を招くことなく、液晶ドライバが生成する階調電圧値の検査を行うことができる半導体装置、及びその検査方法を提供する。

【解決手段】

被テストデバイスである半導体装置30は、液晶ドライバ20のほか、テスト制御回路31、階調ばらつき判定回路33、及び、出力切替スイッチ34を備え、被テストデバイスである半導体装置30自身が、テスト用制御信号、及び、テスト用クロック信号に基づき、テスト用の階調電圧を生成するとともに、生成した階調電圧値が外部の半導体試験装置(テスタ)32から供給される基準電圧値に対してばらつきが許容範囲に収まっているか否かを階調ばらつき判定回路33が判定し、その判定結果を半導体試験装置32に出力する。

(もっと読む)

逐次比較型ADコンバータおよびその検査方法

【課題】ADコンバータの変換時間および検査時間を削減する。

【解決手段】

本発明にかかる逐次比較型ADコンバータ10は、アナログ入力をサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13から出力された電位と基準電位とを逐次比較する比較器14と、比較器14による比較結果を記憶する逐次比較レジスタ15と、逐次比較レジスタから出力された比較結果のうち上位ビットの値を記憶するSAR上位ビットレジスタ17と、逐次比較レジスタ15から出力された比較結果の下位ビットの値に基づいて、比較器14における次回以降の逐次比較を全ビットについて行うか、または下位ビットについてのみ行うかを設定するスキップフラグ設定回路18と、を備える。

(もっと読む)

半導体集積回路

【課題】内蔵された回路の状態を確認する機能を備えた半導体集積回路を更に小型化することができる技術を提供

【解決手段】半導体集積回路1では、コアLSI11と周辺LSI12との間の内部配線WIが異常であると判定回路15が判定すると、判定回路15は、リングオシレータ16Aを発振させることを指示する情報(第1発振指示情報)をリングオシレータ制御部17へ出力する。そしてリングオシレータ制御部17が第1発振指示情報を取得すると、リングオシレータ制御部17が、発振周波数f1で発振するように構成されたリングオシレータ16Aを発振させる。そして、半導体集積回路1内で発生している磁界を近磁界プローブで測定し、発振周波数f1で大きさが変動する磁界を検出した場合に、リングオシレータ16Aが動作していると判断することができる。

(もっと読む)

半導体装置のテスト方法

【課題】テストコストの低減を実現可能な半導体装置のテスト方法を提供する。

【解決手段】例えば、ループバック配線LNp1,LNn1,LNp2,LNn2を持つテスト用基板TBD上に被テストデバイスDUTを搭載し、DUTの差動送信端子TXp,TXnからの信号をループバック配線を介して差動受信端子RXp,RXnに戻すことでテストを行う。ループバック配線上には振幅制御回路ブロックVACTLBK1が設けられ、VACTLBK1は、可変利得アンプ回路AMP1等を用いてLNp1,LNn1から入力された信号の電圧振幅レベルを振幅設定信号VASETに基づくレベルに変換してLNp2,LNn2に出力する。これによって、例えば受信電圧振幅レベルのテスト仕様が異なるDUTでTBDを共通に使用すること等が可能になる。

(もっと読む)

半導体装置

【課題】電圧生成回路を備えた半導体装置において、電圧生成回路の電荷供給能力が十分でない場合であってもチャージシェアを引き起こすことなく、電圧生成回路の出力電圧を従来よりも高精度に検出できるようにする。

【解決手段】半導体装置1は、電圧生成回路11と、第1のスイッチSW2と、充電回路20とを備える。電圧生成回路11は、電圧を生成して出力し、生成する電圧の大きさを調整する機能を有する。第1のスイッチSW2は、オン状態のときに互いに導通する第1および第2の導通端子を有し、第1の導通端子が電圧生成回路11の出力ノードと配線を介して接続される。充電回路20は、第1のスイッチSW2の第2の導通端子に接続された配線を充電する。

(もっと読む)

高周波モジュール

【課題】高周波ICが設計通りの特性で動作するかどうかをモジュールの完成後であっても、検査できる高周波モジュールを提供する。

【解決手段】高周波モジュール10は、電極パターンが形成された複数の誘電体層を有する積層体と、スイッチ素子11に印加された負電圧を出力するテスト端子PTを有し、積層体の表面に実装されたスイッチ素子11とが一体成型されている。積層体には、裏面に信号を外部へ出力する外部接続用のテスト外部端子PTestが設けられている。積層体には、テスト端子PTとテスト外部端子PTestとを電気的に接続する電圧伝送経路を有している。

(もっと読む)

1 - 20 / 239

[ Back to top ]