Fターム[2G132AG01]の内容

電子回路の試験 (32,879) | 信号の印加に関するもの (2,293) | 試験信号の発生 (1,325)

Fターム[2G132AG01]の下位に属するFターム

メモリ内容の読出しによる発生 (290)

演算による発生 (48)

読出したデータを加工して出力 (62)

ランダム信号の発生 (60)

1サイクル中に多数の信号を発生 (7)

Fターム[2G132AG01]に分類される特許

1 - 20 / 858

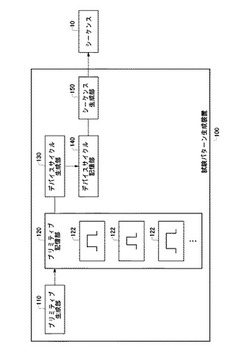

試験パターン生成装置、試験プログラム生成装置、生成方法、プログラム、および試験装置

【課題】試験装置のハードウェア仕様および試験装置用のプログラム言語に詳しくないユーザでも、試験パターンを容易に作成させる装置を提供する。

【解決手段】複数の端子を有する被試験デバイスとの間で通信する試験パターンを生成する試験パターン生成装置であって、基本サイクル中に複数の端子のそれぞれとの間で通信する信号パターンを示すサイクルプリミティブをユーザの指示に基づき生成するプリミティブ生成部と、ユーザの指示に基づき複数のサイクルプリミティブを配列して、複数の基本サイクル分の信号パターンを示すデバイスサイクルを生成するデバイスサイクル生成部と、ユーザの指示に基づき複数のデバイスサイクルを配列して、被試験デバイスに供給する試験パターンのシーケンスを生成するシーケンス生成部と、を備える試験パターン生成装置を提供する。

(もっと読む)

電池監視装置

【課題】信頼性の向上を図ることができる電池監視装置の提供。

【解決手段】電池監視装置は、直列接続された複数の電池セル(BC1〜BC4)の各セル電圧値を測定する電圧測定部を有する集積回路IC1と、複数の電池セルの正負両極と集積回路とを接続する複数の電圧計測ラインL1〜L5と、測定された各セル電圧値に基づいて電池セルの状態を監視する制御回路30と、を備え、集積回路は、互いに異なる擬似電圧を生成する擬似電圧生成部402〜405を有し、電圧測定部は、計測対象となる電池セルの正負両極に接続された一対の電圧計測ラインを選択する選択回路HVMUX1,HVMUX2と、選択回路により選択された一対の電圧計測ラインからの電圧を検出する検出回路262,122Aと、を有し、制御回路は、擬似電圧を選択回路に入力し、検出回路により検出された電圧値に基づいて選択回路による選択状態を診断する。

(もっと読む)

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

スキャン・チェーン用動的クロック領域バイパス

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

試験装置

【課題】電源電圧変動を制御可能な試験装置を提供する。

【解決手段】試験装置2は、被試験デバイス(DUT)1を試験する。メイン電源10は、DUT1の電源端子P1に供給すべき電力信号VDDを生成する。メイン電源10の出力端子P4とDUT1の電源端子P1の間の電源ライン上には、可変電源経路部30が設けられる。可変電源経路部30は、その電気的特性が可変に構成される。制御部32は、可変電源経路部30の電気的特性を制御する。

(もっと読む)

半導体集積回路の検査方法および半導体集積回路

【課題】半導体集積回路のクロックに一定周波数のクロックのみを供給しつつ半導体集積回路の内部クロックを動的に変化させて半導体集積回路のランダム・ロジックを検査する。

【解決手段】複数の組み合わせ回路と当該複数の組み合わせ回路のスキャンテストを行うためのスキャンチェーンを構成する複数のスキャンフリップフロップとを有する半導体集積回路、の検査方法を、クロック生成装置から前記半導体集積回路に一定周波数の第1クロックを入力する入力工程と、前記半導体集積回路の内蔵する分周器が前記第1クロックを分周して第2クロックを生成する分周工程と、前記複数のスキャンフリップフロップに入力するクロックを、前記第1クロックと前記第2クロックとの間で動的に切り替えつつ前記半導体集積回路を検査する検査工程と、により構成する。

(もっと読む)

スキャンチェーン検査装置及び検査方法

【課題】 スキャンチェーンの検査を好適に行うことが可能なスキャンチェーン検査装置及び検査方法を提供する。

【解決手段】 半導体装置10のスキャンチェーンに検査信号を供給する検査信号供給部18と、スキャンチェーンの各レジスタでの検査信号の信号レベルの時間変化を測定するレジスタ測定部20と、測定部20による測定結果に基づいて各レジスタにレジスタ番号を付与するレジスタ番号解析部51を有する検査解析装置50とによってスキャンチェーン検査装置1Aを構成する。供給部18は、信号長nが異なるm種類の検査信号列を供給する。解析部51は、信号長nの検査信号列を用いた測定結果からスキャンチェーンの複数のレジスタをn個のグループに分けるグループ分けをm種類の検査信号列のそれぞれについて行い、その結果に基づいて各レジスタにレジスタ番号を付与する。

(もっと読む)

電源装置およびそれを用いた試験システム

【課題】電源電圧の変動を抑制する。

【解決手段】メイン電源は、DUT1の電源端子P1の電位を所定の目標値に近づくように帰還制御する。制御端子PCNTには、補償電源が生成すべき補償電流の目標波形REFを指示する電流制御信号SCNTが入力される。電流検出回路22は、インダクタL1に流れる電流ILに応じた検出信号VCSを生成する。パルス変調器24は、検出信号VCSを電流制御信号SCNTに応じた目標波形REFと比較し、比較結果に応じてレベルが変化するパルス信号Spを生成する。ドライバ26は、パルス信号Spにもとづいて、第1スイッチSW1および第2スイッチSW2を相補的にスイッチングする。

(もっと読む)

半導体装置

【課題】半導体チップの面積を縮小することが可能な半導体装置を提供する。

【解決手段】半導体チップを有する半導体装置では、半導体チップに設けられた内部回路のテストを行うテスト回路と、そのテストが行われている間は内部回路を駆動せず、テストが行われた後に内部回路を駆動する駆動回路とを有し、内部回路に接続された信号線が、テスト回路と駆動回路とで共用される。

(もっと読む)

擬似障害発生方法と装置

【課題】電子回路装置に対する擬似障害発生を容易化し、試験・評価等の作業を効率化する装置、方法の提供。

【解決手段】

電子回路装置(100)を構成する回路基板(105)上のIC(104)のON/OFF端子に接続部103を介して接続する制御部102が、ケーブルコネクタ部(101)を介してPC(110)の制御により、IC(104)のON/OFF端子に動作中の第1の値とは異なる第2の値を設定することで擬似障害を発生させる。

(もっと読む)

半導体集積回路及びそのテスト方法

【課題】プローブ針を接触させる外部端子の数を抑制してDCテストを行うことが可能な半導体集積回路を提供すること

【解決手段】本発明にかかる半導体集積回路は、入出力端子P1を介して外部にデータを出力する出力バッファ21と、外部から入出力端子P1を介してデータが入力される入力バッファ22と、入出力端子P1と入力バッファ22の入力との間の信号線上のノードN1と第1入力端子T1との間に設けられたスイッチ26と、外部から第2入力端子T2に供給される第2基準電位とノードN1の電位とを比較して比較結果を出力する比較部23と、入力バッファ22から出力されるデータと比較部23の比較結果との何れかを選択しテスト結果として出力する選択部52と、を備える。

(もっと読む)

差動伝送半導体装置

【課題】正確な性能測定を容易にした差動伝送半導体装置を提供する。

【解決手段】差動対入力信号に応答してステップ信号を各々が生成する複数の入力コンパレータと、当該ステップ信号を伝送する伝送回路と、当該伝送回路によって伝送されたステップ信号に応答して差動対出力信号を各々が生成する複数の出力アンプと、を含み、供給されるテスト指令に応じて当該出力アンプの差動対出力信号を択一的に取り込んで、これに含まれるクロスポイントの発生タイミングを示す検査出力信号を生成する。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング調整方法

【課題】複数の被試験デバイスに対して電源供給部から電源の供給を行って試験を行うときに、同時スイッチングノイズの影響を抑制することを目的とする。

【解決手段】本発明の半導体試験装置1は、複数のDUT3に電源を供給するデバイスパワーサプライ5を備える半導体試験装置1であって、DUT3の試験を行うピンエレクトロニクスカード2のドライバ12およびコンパレータ13とDUT3との間の伝送経路15の伝播遅延Tpdを校正するデータをタイミング校正データとして記憶するタイミング校正データ記憶部21と、DUT3を複数のグループに分割して、当該グループごとに異なる遅延量をタイミング校正データに加算する遅延量加算部25と、を備えたことを特徴としている。

(もっと読む)

半導体検査方法および半導体検査装置

【課題】レーザパルス光の照射に応じて半導体デバイスにて発生する電磁波パルスの強度を非接触状態で向上させる技術を提供すること。

【解決手段】半導体デバイスを検査する半導体検査装置100である。半導体検査装置100は、半導体デバイスが形成されている基板1に対してレーザパルス光2を出射するレーザパルス光源14と、レーザパルス光2が照射される照射位置10に対して逆方向バイアスをかけるための逆バイアス用電磁波パルス4を照射する電磁波パルス照射部18と、

レーザパルス光2の照射に応じて照射位置10から放射される電磁波パルス3を検出する検出部17とを備えている。

(もっと読む)

任意波形発生装置のチャンネル校正方法

【課題】任意波形発生装置の校正方法を改善する。

【解決手段】Sパラメータを用いて任意波形発生装置を校正する。任意波形発生装置が有するチャンネルとしては、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルでも良い。差動信号を生成する場合でも良く、2チャンネルを1対として、複数のチャンネル対を校正できる。このとき、各チャンネルは、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルで1つのチャンネルを構成する場合でも良い。

(もっと読む)

任意波形発生装置のインターリーブ・チャンネル校正方法

【課題】任意波形発生装置の校正方法を改善する。

【解決手段】Sパラメータを用いて任意波形発生装置を校正する。任意波形発生装置が有するチャンネルとしては、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルでも良い。差動信号を生成する場合でも良く、2チャンネルを1対として、複数のチャンネル対を校正できる。このとき、各チャンネルは、単一の非インタリーブ・チャンネルでも良いし、インターリーブされた複数チャンネルで1つのチャンネルを構成する場合でも良い。

(もっと読む)

電源瞬断試験装置

【課題】電源電圧の瞬断、瞬オンに対する自動車用電子機器の動作限界を定量的に調査する手段を提供する。

【解決手段】被試験機に印加する通常の電源電圧である+Bおよび被試験機のメモリーホールドなどのための常時印加の電圧であるAccの瞬断について、様々なパターンを再現するために当該時間、電圧についてもプログラムを用いて少しつづ徐々に変化させて被試験機に印加し、これに基づく被試験機の応答を監視して別に定めた短い時間ごとに出力論理の正否を確認することにより、自動車用に最近多く用いられるデジタル機器独特のプログラムによる思いも寄らない誤動作の発生を確認でき、さらに誤動作発生時の誤動作モードをきちんと捕らえて適切な設計対応を取ることができる。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

1 - 20 / 858

[ Back to top ]