Fターム[4M104FF13]の内容

Fターム[4M104FF13]の下位に属するFターム

Fターム[4M104FF13]に分類される特許

141 - 160 / 2,637

機能膜形成方法、配線基板の製造方法および配線基板

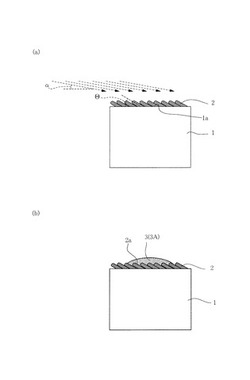

【課題】液体に対し金属膜の表面の濡れ性を改質し、金属表面と液体との接触角を増加させて液体の濡れ広がりを抑制し、信頼性の高い機能膜を低コストで実現すること。

【解決手段】基材1の平板面1aに金属膜2を形成する(金属膜形成工程)。次いで、金属膜2の表面2aに機能材料を含有する液体3を付与し、液体3を固化させて機能膜3Aを形成する(機能膜形成工程)。金属膜形成工程では、平板面1aに対する成膜入射角αが5°以上15°以下となる条件で平板面1aに金属を真空蒸着し、金属膜2を平板面1aに対して20°以上45°以下に傾斜する柱状結晶構造に形成する。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

半導体装置

【課題】本発明は、金属膜の端部の応力により金属膜の端部直下の表面電極がダメージを受けることを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、基板24と、該基板24の上に、アルミを含む材料で形成された表面電極26と、該表面電極26の上に、はんだ付け可能な材料で形成された金属膜28と、該表面電極26の上の部分と、該金属膜28の端部に重なる重畳部分30aとが一体的に形成されて該金属膜28の端部を固定する端部固定膜30と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面の金属汚染を十分除去することにより、製造された炭化珪素半導体素子の初期特性を改善する。また、金属汚染を低減し、半導体装置の長期信頼性を向上する方法を提供する。

【解決手段】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面を酸化するステップと、該ステップにより炭化珪素表面に形成された二酸化シリコンを主成分とする膜を除去するステップとからなる炭化珪素表面の金属汚染除去工程を適用する。

(もっと読む)

半導体装置

【課題】冷却効率を向上させることができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、裏面に複数の凹部16を有するシリコン基板11と、この基板11の表面上に形成された半導体層12と、半導体層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、ドレイン電極13とソース電極14との間の半導体層12上に形成されたゲート電極15と、複数の凹部16の内部を含むシリコン基板11の裏面全体に形成された裏面金属17と、を具備する。

(もっと読む)

SiC半導体デバイス及びその製造方法

【課題】SiC半導体デバイスにおいて、裏面電極の剥離を十分に抑制することができる製造方法と、裏面電極の剥離が防止された新規な裏面電極構造を有するSiC半導体デバイスを提供する。

【解決手段】SiC半導体上へチタン及びニッケルを含む層を形成して、加熱によりチタンカーバイドを含むニッケルシリサイド層を形成させ、析出した炭素層を逆スパッタにより除去することにより、後工程でニッケルシリサイド上に形成される金属層の電極が剥離することを抑制する。炭素層を除去する前のニッケルシリサイド表面の、析出した炭素の量とチタンカーバイドの炭素量の関係が、所定の条件のときに、さらに剥離防止の効果を向上させることができる。

(もっと読む)

電界効果型トランジスタ

【課題】ゲート電極のドレイン端の電界を緩和し、ゲート絶縁膜の破損を低減する。

【解決手段】窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップエネルギーが大きい窒化物半導体で形成された電子供給層112と、チャネル層108の上方に形成されたソース電極116およびドレイン電極118と、チャネル層108の上方に形成されたゲート電極120と、チャネル層108の上方に形成され、チャネル層108からホールを引き抜くホール引抜部126と、ゲート電極120およびホール引抜部126を、電気的に接続する接続部124と、を備える電界効果型トランジスタ100。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

電極およびそれを含む電子素子

【課題】優秀な導電性及び大きい仕事関数を有する電極及びそれを含んだ電子素子を提供する。

【解決手段】グラフェン含有層と、前記グラフェン含有層上に形成される仕事関数傾斜層と、を含み、前記仕事関数傾斜層は、前記グラフェン含有層と接触する第1面、及び前記第1面に対向する第2面を有する単一層であり、前記仕事関数傾斜層の仕事関数は、前記第1面から前記第2面に向かう方向に沿って漸進的に増大する電極。

(もっと読む)

半導体装置

【課題】本発明は、SiC半導体からなるSBDを有し、歩留まりの高い半導体装置を提供する。

【解決手段】第1及び第2のダイパットが互いに離間して配置されたパッケージと、第1のダイパット上に搭載された、シリコンカーバイトからなる半導体層を有し、ショットキー接合とpn接合が併設されたショットキーバリアダイオードと、ショットキーバリアダイオードと並列接続されて第2のダイパット上に搭載された、シリコンからなる半導体層を有するpn接合ダイオードとを備え、ショットキーバリアダイオードにおいてpn接合を構成する高濃度不純物領域とショットキー接合を構成するショットキー電極とが直接に接している。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素ショットキーダイオードの製造において、ダイオードの順方向特性、特に障壁高さφBを安定させて、リーク電流のばらつきを低減させることが可能な半導体装置を提供する。

【解決手段】エピタキシャル層2上に乾式熱酸化によりシリコン酸化膜OX1を形成し、SiC基板1の裏面にオーミック電極3を形成し、その後、SiC基板1をアニールしてオーミック電極3とSiC基板1の裏面との間にオーミック接合を形成し、シリコン酸化膜OX1を除去した後、エピタキシャル層2上にショットキー電極4を形成する。その後、シンターを行い、ショットキー電極4とエピタキシャル層との間にショットキー接合を形成する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

窒化物半導体発光素子の製造方法

【課題】工程数が少なく生産性を向上する窒化物半導体発光素子の製造方法を提供する。

【解決手段】まず、パッド電極層形成工程S11で、窒化物半導体発光素子構造上に、n側パッド電極およびp側パッド電極となるパッド電極層を形成し、レジストパターン形成工程S12で、パッド電極層上に、n側パッド電極およびp側パッド電極を形成する領域を被覆するレジストパターンを形成する。次に、パッド電極層エッチング工程S13で、このレジストパターンをマスクとして、パッド電極層をエッチングしてn側パッド電極およびp側パッド電極を形成する。続いて、このレジストパターンを除去せずに、保護層形成工程S14で、窒化物半導体発光素子構造の表面およびレジストパターン上に絶縁性の保護層を形成した後に、レジストパターン除去工程S15で、レジストパターンを除去する。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、480℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が1〜5μmであることを特徴とする半導体電極構造。

(a)Alマトリックスの最大粒径が1μm以下

(b)ヒロック密度が1×109個/m2未満

(c)電気抵抗率が10μΩcm以下

(もっと読む)

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、2次元電子ガス除去領域260Bが、ドレイン電極211の長手方向の一方の端211Aから短手方向に伸ばした仮想線M71よりも長手方向外方に位置すると共にソース電極212の一端部212Aに対して短手方向に隣接する領域の下のGaN系積層体205に形成されている。また、2次元電子ガス除去領域260Aは、2次元電子ガス除去領域260Bの長手方向外方に隣接すると共にソース電極212の一端部212Aからソース電極接続部214に沿って短手方向に延在している。2次元電子ガス除去領域260A,260Bの存在によって、スイッチング時の動的な電界変動によってソース電極212の端部212Aからドレイン電極211の端部211Aへ向かって電子流が集中することを回避できる。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、ドレイン電極12の長手方向の端12A,12Bから長手方向と直交する短手方向に伸ばした仮想線M1,M2よりも長手方向外方に位置すると共にソース電極11に隣接する領域の下のGaN系積層体5、およびドレイン電極12の長手方向の端12A,12Bに長手方向外側に隣接する領域の下のGaN系積層体5に2次元電子ガスが存在しない2次元電子ガス除去領域31が形成されている。2次元電子ガス除去領域31の存在によって、スイッチング時の動的な電界変動によってソース電極11の端部からドレイン電極12の端部へ向かって電子流が集中することを回避できる。

(もっと読む)

141 - 160 / 2,637

[ Back to top ]