Fターム[5E336GG19]の内容

プリント板への電気部品等の実装構造 (16,219) | 目的又は効果 (2,617) | 部品調整に関するもの (15)

Fターム[5E336GG19]に分類される特許

1 - 15 / 15

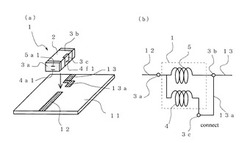

ノイズ対策電子部品の回路基板への実装構造

【課題】 実装箇所に応じたノイズ対策電子部品を複数用意する必要が無くなり、ノイズ対策の検討を容易迅速に行うことが可能なノイズ対策電子部品の実装構造を提供する。

【解決手段】 インダクタ1の実装する部品側面を底面にして第1の接続状態にすることで、第2のコイル4の他端の引出電極4f1が第3の外部電極3cおよび短絡用配線パターン13aを介して他方の外部電極3bに接続される。このため、コイル4,5は、各一端が一方の外部電極3aに共通接続され、各他端が他方の外部電極3bに共通接続されて、並列接続される。従って、インダクタ1の抵抗成分は小さくなる。一方、インダクタ1の実装する部品側面を異ならせて天面にし、第2の接続状態にすることで、第3の外部電極3cは電気的に浮き、第2のコイル4の他端も浮いた状態になる。このため、インダクタ1のインピーダンスは第1のコイル5が有するものとなって高くなる。

(もっと読む)

配線基板およびその製造方法

【課題】 小型化が容易であり、電子部品の複数の電極のそれぞれに対応した静電容量のコンデンサを接続させることも容易な配線基板、およびその製造方法を提供する。

【解決手段】 厚み方向に貫通する貫通孔3を有する絶縁基板1と、貫通孔3の内側面に被着された接地導体層4と、接地導体層4の表面に接合時に流動性を有する導電性接合材を固化させてなる接合層5を介して被着された導体層からなる第1電極6と、貫通孔3内の第1電極6の内側に第1電極6との間に誘電体層7を介して配置された柱状の導体からなる第2電極8とを備える配線基板である。コンデンサ素子を搭載するスペースが不要であるため小型化が容易であり、誘電体層7の厚さの調整等により、電子部品の複数の電極に対応した静電容量を有する複数のコンデンサを絶縁基板1に配置することも容易である。

(もっと読む)

電子部品の実装構造

【課題】電子部品の端子脚の基板から下方への突出長さの調節やスタンドオフの高さ調節を容易にできる、電子部品の実装構造を提供する。

【解決手段】電子部品10は、支持脚部15として相互に高さの異なる複数組のスタンドオフ突起15aが対設され、複数組のスタンドオフ突起15aのうち一部の組のスタンドオフ突起15aのみの先端が基板20の上面21に当接して支持されている。

(もっと読む)

部品内蔵プリント基板

【課題】部品端子間寸法が異なる部品が挿入実装されるとともに場所により厚さを変えなくても良い部品内蔵プリント基板を提供する。

【解決手段】部品内蔵プリント基板は、貫通穴および表面に配線を有する基板材、上記貫通穴に挿入されるとともに一対の端子を有する部品、および上記端子と基板表面の配線とを接続するとともに金属ペーストを硬化する接続部材を備える。また、別の部品内蔵プリント基板は、貫通穴および上記貫通穴の周りを取り囲むように設けられる配線を有する基板材、上記貫通穴に挿入されるとともに一対の端子を有する部品、および上記端子と上記貫通穴の周りの配線とを接続するとともに金属ペーストを硬化した接続部材を備える。

(もっと読む)

回路基板

【課題】

液晶ドライバLSIをガラス基板に直接ACF等を用いて実装する際、加熱による歪が残留することで完成品の表示部にムラが残る。これを抑制する。

【解決手段】

上記課題を解決するために、半導体部品は第1の熱膨張率を有するとともに、他の半導体部品と信号を授受するための第1の誘導結合部を備えるようにし、プリント配線板は、前記半導体と異なる第2の熱膨張率を有するとともに、第1の誘導結合部との間で信号を授受するための第2の誘導結合部を備え、本発明の回路基板は、前記第1の誘導結合部と前記第2の誘導結合部が対向配置されて、前記半導体部品を前記プリント配線板に固定材により固定し、前記半導体部品間で信号が授受されるようにした。

(もっと読む)

プリント基板

【課題】 本発明はプリント基板に係り、半導体素子のリード位置の変更があった場合に、パターン変更やリード加工することなく半導体素子を実装可能なプリント基板を提供することを目的とする。

【解決手段】 請求項1に係る発明は、半導体素子の複数のリード端子に合わせてスルーホールを形成したプリント基板に於て、前記スルーホールを長孔状に形成し、該スルーホールに、半導体素子のリード位置の変更に対応可能なスペーサを装着することを特徴とする。そして、請求項2に係る発明は、半導体素子の複数のリード端子に合わせてスルーホールを形成したプリント基板に於て、前記スルーホールをリード端子よりも大径な円形状に形成し、該スルーホールに、半導体素子のリード位置の変更に対応可能なスペーサを装着することを特徴とする。

(もっと読む)

部品内蔵実装基板

【課題】高速・高密度電子機器で特に信号品質の確保が必要なCPU−メモリ間のアドレス線において、小型化と高周波特性確保の両立が実現できる部品内蔵実装基板を提供する。

【解決手段】絶縁基板100の表面上に、CPU101と、チップ部品としての並列終端抵抗105と、メモリ102とが搭載されている。絶縁基板100の内部には、CPU101の直下に第1のデカップリングキャパシタ106aが内蔵され、メモリ102の直下に第2のデカップリングキャパシタ106bが内蔵されている。並列終端抵抗105の直下には、膜部品としての直列終端抵抗103b及び信号品質補償用キャパシタ104bがその面を絶縁基板100の表面に平行にして内蔵されており、両者間に第3のデカップリングキャパシタ106cが内蔵されている。

(もっと読む)

電子制御装置

【課題】部品点数が少なく、組立工程が少なくて生産効率が高く、設計自由度が高い電子制御装置を提供する。

【解決手段】電子回路部と、前記電子回路部と電気的に接続され、プレスフィット部を有するターミナルとを、前記ターミナルの一部が露出するように封止材で覆って成る電子回路封入部材と、内層パターンが設けられた樹脂基板とを備え、前記樹脂基板は、前記ターミナルのプレスフィット部が圧入される第1のスルーホールと、外部負荷に接続される第2のスルーホールとを有し、前記第1のスルーホールと第2のスルーホールとを前記内層パターンによって接続した。

(もっと読む)

部品実装方法と実装基板

【課題】小型化された基板の両面に容易に電子部品を実装することができる電子部品実装方法を提供する。

【解決手段】本発明に係る部品実装方法は、熱硬化により被貼付部材の表面の凹凸を吸収して貼付面の裏面が平面状に形成されるシート状封止材20を基板1の第1の面に実装された第1の電子部品10と共に第1の面に貼付して熱硬化させるステップと、シート状封止材20の貼付面の裏面に形成された平面を支持面として、基板1の第2の面にフレキシブルプリント基板30を実装するステップとを有する。

(もっと読む)

絶対角度検出装置

【課題】高分解能にして組立が容易な絶対角度検出装置を提供する。

【解決手段】ステータ部材1と、ステータ部材1に回転可能に支承されているロータ部材2と、ロータ部材2に一体的に取り付けられたコード板3と、コード板3に形成された信号検出用のコードパターン列3aと、ステータ部材1内に備えられたプリント基板5と、プリント基板5に実装された複数個の検出素子6とを有し、当該検出素子6がコードパターン列3aの配列方向に沿って所定の間隔で配置された絶対角度検出装置において、リード貫通孔5aが開設されたプリント基板5と当該プリント基板5上に実装される複数個の検出素子6の本体部6aとの間に、位置決め孔11が開設されたシート状の位置規制部材10を介設する。

(もっと読む)

多層配線基板及びその製造方法

【課題】 ゲインの微調整が可能で、歪み特性の優れた多層配線基板及びその製造方法を得る。

【解決手段】 実装状態で開口部が下向きとなるダウンキャビティ17を有するセラミック積層基板7と、ダウンキャビティ17内に搭載された二つの低ノイズ増幅器2と、セラミック積層基板7の上面7aに搭載された弾性表面波フィルタ3などを備えた多層配線基板。二つの低ノイズ増幅器2のそれぞれのエミッタ−グランド間に、低ノイズ増幅器2のそれぞれの周波数に対応する微小な整合用インダクタSL1,SL2が挿入されている。整合用インダクタSL1,SL2は同一層に形成され、セラミック積層基板7のキャビティ17を囲む壁部に配置されている。

(もっと読む)

デジタル信号処理基板

【課題】各種電子機器に使用されるデジタル信号処理基板に関し、デジタルノイズ対策により小型薄型化と低価格化が困難という課題を解決し、デジタルノイズ低減を図って小型薄型化と低価格化を実現するデジタル信号処理基板を提供することを目的とする。

【解決手段】クロック動作用の素子が接続されたLSI16と、このLSI16に電力を供給する電源入力ライン18と、この電源入力ライン18とアース間に接続されたデカップリングコンデンサを少なくとも有したデジタル信号処理基板において、デカップリングコンデンサとして、ESRが25mΩ(100kHz)以下、かつ、ESLが800pH(500MHz)以下の固体電解コンデンサ19を用いた構成により、デジタルノイズの発生を大きく低減できるため、従来のようにデジタルノイズ低減のためのコンデンサを大量に接続する必要がなくなり、小型薄型化と低価格化を同時に実現できる。

(もっと読む)

プリント基板の接続構造

【課題】電子デバイスの電源ピンの近傍にバイパスコンデンサを実装することが可能であるとともに、コストアップや開発期間の増加を防止し、信頼性、量産性を向上する。

【解決手段】プリント基板1の表面側に配置した半導体2の一対の電源ピン2aをプリント基板1のスルーホール部1a及びプリント基板1の裏側に配置した補助基板3のスルーホール部3aに挿通して半田付けし、補助基板3上の電源ピン2a間にバイパスコンデンサ7を接続する。

(もっと読む)

プリント配線板

【課題】IC/LSIの動作安定、ノイズ抑制、実装面積等において最適なバイパスコンデンサの構成決定の手法を提供する。

【解決手段】各電源端子に対し、バイパスコンデンサをC1,C2,C3の3つを配置し、C1は用意できる最大の容量値のものに決定し、又、IC/LSIの電源端子から見たIC/LSIの内部のインピーダンス特性において極小点となる共振周波数と、IC/LSIの電源端子から見た、概略バイパスコンデンサの定数とバイパスコンデンサの自己インダクタンスと電源ピンからバイパスコンデンサまでの配線によって概略決まるプリント配線板上の給電回路のインピーダンス特性における共振周波数を一致させるようにC2,C3容量値を確定することで、試行錯誤的な給電回路の最適化作業の負荷を低減させる。

(もっと読む)

高速信号用コネクタ付きBGA型LSIとプリント基板との接続構造

【課題】 熱膨張による破壊を防止した高速信号用コネクタ付きBGA型LSIとプリント基板との接続構造を提供する。

【解決手段】 コネクタ付きBGA型LSI300とプリント基板500とを電気的に接続させると共に、コネクタ付きBGA型LSI300をプリント基板500に押圧させながらコネクタ付きBGA型LSI300がリジットケーブル101の長手方向に微動できる押圧接続手段102、110を設けることにより、リジットケーブル101が熱膨張収縮してコネクタ付きBGA型LSI300がプリント基板500上を微動すると、導電フィルム110にずれが生じて導電フィルム110内の導電ワイヤ201がそのずれに追従するので、コネクタ付きBGA型LSI300とプリント基板500との電気的接続が維持される。

(もっと読む)

1 - 15 / 15

[ Back to top ]