Fターム[5F003BP41]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | 熱処理、アニール (155)

Fターム[5F003BP41]の下位に属するFターム

非酸化性雰囲気中 (13)

局部的アニール(レーザー、電子線) (3)

単結晶化 (2)

Fターム[5F003BP41]に分類される特許

1 - 20 / 137

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

半導体装置およびその製造方法

【課題】ヘテロ構造のpn接合において、電子が妨げられることなく注入されるようにする。

【解決手段】Gaを含む窒化物半導体からなるn型の窒化物半導体層101と、窒化物半導体層101に接合して形成されたp型のシリコンからなるp型シリコン層102とを少なくとも備える。窒化物半導体層101とp型シリコン層102とは、接合界面103により接合している。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】InP系の微細構造デバイスをより効果的に冷却できるようにする。

【解決手段】主表面を(001)面としたInPからなる基板101の上にInGaAsからなるバッファ層102を形成し、バッファ層102の上に接して配置されたInPの層を含んでバッファ層102の上に形成されたデバイス103を形成し、デバイス103の周囲のバッファ層102を露出させた状態でデバイス103を覆う保護層104を形成し、露出したバッファ層102の上に金を堆積して金層105を形成し、次に、バッファ層102の表面に接触している金層105よりデバイス103の下部のバッファ層102に金を拡散させる。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有する半導体装置の製造方法を提供する。

【解決手段】電極層の上に希土類金属シリサイド膜とアモルファスシリコン膜とを形成し、希土類金属シリサイド膜とアモルファスシリコン膜とをマイクロ波を用いて加熱することにより、希土類金属シリサイド膜の結晶構造に応じた結晶配向を持つように、アモルファスシリコン膜を結晶化させる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

低周波雑音の低い微細化素子の製造法とそれを適用した集積回路製品

【課題】MOS集積回路のP型ウェーハ基板やバイポーラ集積回路のNPNトランジスタのベース領域など、N型不純物を添加する以前の下地となるP型領域形成時の特に270〜150℃の範囲の冷却には問題があり、それらの問題を解決し低周波雑音を低減し、平坦性の良い微細化PN接合界面を提供する。

【解決手段】1つ目は下地となるP型領域内の歪エネルギーを最小の状態で固定化することで、2つ目は問題となる素子の近傍に線状欠陥領域を設け、素子の重要な接合部中に発生している格子間シリコンを欠陥のIG能力で吸着せしめる。前者はMOS集積回路の場合は全ての熱処理工程の最初にP型基板を150℃16時間以上、160℃8時間以上等の条件でアニールしておく。このようにすることでP型基板に直接形成するNMOSのチャンネル雑音を低減することが出来る。

(もっと読む)

SiC結晶成長層の製造方法およびバイポーラ型半導体素子

【課題】層厚さが厚くてもSiC結晶中にある炭素空孔を低減できるSiC結晶成長層の製造方法を提供する。

【解決手段】SiC結晶成長層としてのドリフト層23を成長させる工程内に、シリコン原料ガスであるシランと炭素原料ガスであるプロパンのうちのプロパンのみを結晶成長表面に供給する第2の期間を設けている。このことで、結晶成長表面の炭素の過飽和度を上げ、成長途中の表面に過剰な格子間炭素を発生させる。これにより、成長後のSiC結晶成長層としてのドリフト層23の表面から離れている比較的深い箇所での炭素空孔を減少させることができる。

(もっと読む)

半導体基板の製造方法

【課題】イオン注入後のアニール後に生じる残留欠陥を除去することができ、その後シリコンエピタキシャル層を形成しても積層欠陥を生じない、高品質な半導体基板の製造方法を提供する。

【解決手段】半導体基板の製造方法であって、少なくとも、シリコン単結晶基板に選択的にイオン注入を行う工程と、該イオン注入後に、前記シリコン単結晶基板の結晶性を回復させる回復熱処理と前記注入イオンを拡散させる拡散熱処理を行う熱処理工程と、該熱処理後に、前記イオン注入工程によって前記シリコン単結晶基板の表面層に形成されたアモルファス層の全部を取り込む厚さの熱酸化膜を形成する熱酸化膜形成工程と、該形成された熱酸化膜を除去する工程と、該熱酸化膜を除去した表面上にエピタキシャル層を形成する工程と、を有することを特徴とする半導体基板の製造方法。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

バイポーラ・トランジスタ構造およびその製造方法

【課題】エミツタ・ベース間の接合界面特性の最適化により、性能が改善されたバイポーラ・トランジスタ構造そのおよび製造方法を提供する。

【解決手段】バイポーラ・トランジスタは、(1)半導体基板内に少なくとも部分的に位置決めされたコレクタ領域15と、(2)コレクタ領域に接触するベース領域16と、(3)ベース領域に接触するエミッタ領域16Aとを含む。エミッタ領域とベース領域の界面は、酸素不純物と、フッ素不純物および炭素不純物から成るグループから選ばれた少なくとも1つの不純物とを含む損傷領域16Aをエミツタ開口のベースを含む層16に形成することにより、バイポーラ・トランジスタの性能を改善する。それらの不純物は、ベース領域を構成するベース材料のプラズマ・エッチング処理または代わりに無水アンモニアおよびフッ化水素処理が後に続く熱処理によって界面に導入することができる。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタにおいて、耐圧改善のためにコレクタ濃度を低くした際のトランジスタとしての性能低下を抑制する。

【解決手段】バイポーラトランジスタ100は、コレクタ層3上に、エピタキシャル成長されたヘテロ接合の真性ベース層50を有する。真性ベース層50は、分離層4に囲まれたコレクタ層3上に配置され、コレクタ層3の表面部に、N型不純物層30が形成されている。N型不純物層30の不純物濃度は、N型不純物層30の下方におけるコレクタ層3の不純物濃度よりも高い。N型不純物層30と真性ベース層50との間に、N型不純物層30及び真性ベース層50よりも不純物濃度が低いエピタキシャル成長層が形成されている。

(もっと読む)

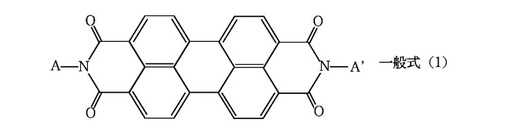

トランジスタ素子

【課題】エミッタ電極−コレクタ電極間において、オフ電流が小さく、かつ、低電圧で大電流変調が可能であるオン/オフ比に優れたトランジスタ素子を提供すること。

【解決手段】エミッタ電極とコレクタ電極との間に、有機半導体層とシート状のベース電極とが設けられているトランジスタ素子において、該有機半導体層が、下記一般式(1)で表される化合物を含んでいるトランジスタ素子。 (もっと読む)

(もっと読む)

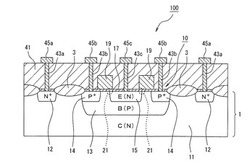

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

1 - 20 / 137

[ Back to top ]