Fターム[5F033QQ00]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095)

Fターム[5F033QQ00]の下位に属するFターム

露光 (971)

エッチング (29,543)

リフトオフ (276)

研磨 (4,337)

エネルギービームの照射 (929)

不純物導入、イオン注入 (1,611)

選択導電化、絶縁化によるパターン形成 (22)

合金化処理(熱処理を含む) (771)

熱処理 (5,181)

冷却(自然冷却は除く) (23)

酸化処理 (296)

窒化処理 (195)

清浄化 (1,803)

空気、大気に晒さない連続処理 (330)

外力を加えて形状を変化させるもの (66)

Fターム[5F033QQ00]に分類される特許

1 - 20 / 741

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

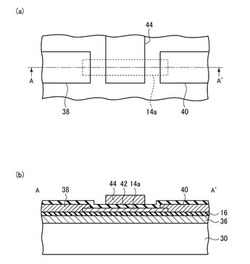

コンタクトホールの形成方法および電気光学装置の製造方法

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 実施形態は、層間配線抵抗が低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、基板と、前記基板上に第1の触媒金属膜と、前記第1の触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと、前記コンタクトホール底部に前記グラフェンと電気的に導通する導電膜と、導電膜上に水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した第2の触媒金属膜と、前記第2の触媒金属膜上にカーボンナノチューブとを備えることを特徴とする。

(もっと読む)

膜の形成方法および形成装置

【課題】プラスチック基板上に塗布印刷を用いて所望の特性を有する膜を形成することができる膜の形成方法および形成装置を提供する。

【解決手段】プラスチック基板上に塗布組成物を塗布した塗布膜からなるパターンが形成された部材を作製する工程1、部材に超音波を照射して塗布膜の乾燥および/または改質を行う工程2を備え、溶液状態の塗布膜に化学作用を及ぼして、デバイスに用いられる配線膜、電極膜、絶縁膜などの所定の膜を形成する。

(もっと読む)

多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法

【課題】上部配線層と下部配線層とを、微細なコンタクトホールを介して接続する多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法を提供する。

【解決手段】基板10上に形成された第1の導電層20と、層間絶縁層30と、第2の導電層70とを有し、前記層間絶縁層に形成されたコンタクトホール40を介して前記第1の導電層と前記第2の導電層とが電気的に接続された構造を有する多層配線基板において、

前記層間絶縁層は、前記コンタクトホールを含まない第1の領域50と、前記コンタクトホールを含み、該第1の領域よりも表面エネルギーが高く形成された第2の領域60とを有し、

前記第1の導電層の前記コンタクトホール内の領域は、前記第2の領域よりも表面エネルギーが高く、

前記第2の導電層は、前記層間絶縁層の前記第2の領域に接触して堆積形成され、前記コンタクトホールを介して前記第1の導電層と接続されている。

(もっと読む)

有機シリケート材料からの炭素の除去方法

【課題】有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去すること。

【解決手段】本明細書中に記載されているのは、酸化剤等の、しかし酸化剤に限られない薬品を用いてOSG膜を処理する工程、OSG膜紫外線を含むエネルギー源に曝す工程、またはOSG膜を薬品で処理する工程およびOSG膜をエネルギー源に曝す工程により、有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去するための方法である。

(もっと読む)

半導体装置の製造方法

【課題】SiCOH膜からなる層間絶縁膜に形成された埋め込み用の凹部に銅材を埋め込んで導電路を形成するにあたり、導電路の抵抗を低くすること。

【解決手段】SiCOH膜にプラズマにより凹部を形成すると表面が疎水性になる。このSiCOH膜に水素ガスのリモートプラズマを供給し、Hラジカル及びHイオンにより凹部の表面を親水性に改質する。またプラズマに代えて過酸化水素水を供給してもよく、この場合表面にOH基が形成される。次いで例えばRu3(CO)12ガスとCOガスとを用いてCVDによりRu膜4を成膜し、その後銅材5を埋め込み、CMP処理をして上層側の配線構造を形成する。また改質にあたって、グリム、DMEDAなどを用いてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

厚膜レジストの現像方法、及び半導体デバイスの製造方法

【課題】生産性を低下させることなく、基板の外周部にレジスト残渣が発生することを抑制可能な厚膜レジストの現像方法、及び半導体デバイスの製造方法を提供する。

【解決手段】回路素子層の上面に、厚膜レジストを形成する工程と、厚膜レジストを露光する工程と、露光後に、30〜50rpmの範囲内の一定の回転速度で炭化珪素基板を回転させながら、厚膜レジストの上方から現像液を供給することで、厚膜レジストの上面に現像液よりなるパドルを形成し、該パドルにより厚膜レジストを現像して、厚膜レジストに回路素子層の上面を露出する開口部を形成する工程と、を有する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】2枚の基板の貼り合わせによって電極間接合がなされた構成において、電極材料の拡散を防止しつつも貼り合わせ強度が確保され、これによって信頼性の向上が図られた三次元構造の半導体装置を提供する。

【解決手段】第1電極33、および第1電極33の拡散防止材料で構成され第1電極33の周囲を覆う第1絶縁膜35を含むと共に、第1電極33と第1絶縁膜35とで貼合せ面41が構成された第1基板2と、第1基板2に貼り合わせて設けられ、第1電極33に接合された第2電極67、および第2電極67の拡散防止材料で構成され第2電極67の周囲を覆う第2絶縁膜69を含むと共に、第2電極67と第2絶縁膜69とで第1基板2に対する貼合せ面71が構成された第2基板7とを備えた。

(もっと読む)

半導体装置、及びその製造方法

【課題】多孔質低誘電率絶縁膜が用いられていても、絶縁破壊耐性に優れた配線構造の半導体装置を提供する。

【解決手段】CMP処理工程を経て配線膜が構成される半導体装置の製造方法であって、CMP処理によって汚染された多孔質低誘電率絶縁膜に対して、酸処理、アニール処理、あるいは汚染個所の清浄化処理工程を施し、前記多孔質低誘電率絶縁膜表面の有機成分量、水分量、銅、ナトリウム、カリウム等の残存量を規定値以下に低減する。

(もっと読む)

導電体パターンの形成方法

【課題】フォトリソグラフィでは形成が困難な超微細な導電体パターンを形成しうる導電体パターンの形成方法を提供する。

【解決手段】 基体上に、第1の比抵抗を有する金属酸化物膜を形成し、金属酸化物膜に電極を接触又は所定の距離まで近づけ、この状態で電極と金属酸化物膜との間に第1の電圧を印加することにより、金属酸化物膜の比抵抗を局所的に変化させ、金属酸化物膜の表面側に、第1の比抵抗よりも高い第2の比抵抗を有する高抵抗領域を形成し、金属酸化物膜に電極を接触又は所定の距離まで近づけ、この状態で電極と金属酸化物膜との間に第2の電圧を印加することにより、金属酸化物膜の比抵抗を局所的に変化させ、高抵抗領域の表面側に、第2の比抵抗よりも低い第3の比抵抗を有する導電体パターンを形成する。

(もっと読む)

導電膜パターンの形成方法

【課題】信頼性の高い導電膜パターンの製造方法を提供する。

【解決手段】本発明に係る導電膜パターンの製造方法は、基板10上に導電膜21を成膜し、導電膜21の表面に対して他の層を積層する前に、酸素をプラズマ化したプラズマアッシング処理を施し、表面処理した導電膜21上に、当該導電膜21をパターン形成するためのマスクパターン30を形成する。次いで、マスクパターン30を用いて導電膜21をウェットエッチングによりパターン形成する。基板10は、半導体基板であることが好ましい。導電膜パターンは、例えば、配線、電極パッド等である。

(もっと読む)

1 - 20 / 741

[ Back to top ]