Fターム[5F082DA09]の内容

Fターム[5F082DA09]の下位に属するFターム

多結晶 (97)

Fターム[5F082DA09]に分類される特許

21 - 40 / 84

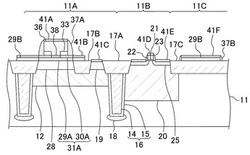

半導体装置の製造方法

【課題】シリサイド化の工程をMOSトランジスタ及びHBTと別けることなく、抵抗値のばらつきが小さいヒューズ素子を形成する半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、MOSトランジスタ形成領域11Bにゲート電極22及びソースドレイン領域25を形成する工程と、MOSトランジスタ形成領域11Bを除いて、半導体基板11の上にシリコン及びシリコン以外のIV族元素を含む混晶膜と、シリコン膜とが順次積層された積層膜31A、31Bを形成する工程と、シリコン膜30Bの露出部分、ゲート電極22の上部及びソースドレイン領域25の上部をシリサイド化する工程とを備えている。

(もっと読む)

駆動素子アレイ及びその製造方法並びに表示装置

【課題】大電流を含む変調電流で発光素子を低電圧駆動させることができるとともに、製造コストの点でも有利な駆動素子アレイを提供する。

【解決手段】パッシブマトリクス方式で電流駆動する発光素子21と、その発光素子21への電流供給を制御するカラム選択用トランジスタ31A及びライン選択用トランジスタ31Bとを有する駆動素子アレイ10であって、そのカラム選択用トランジスタ31Aとライン選択用トランジスタ31Bを、発光素子21と同一の基板19上に形成された縦型有機トランジスタであるように構成して上記課題を解決した。この縦型有機トランジスタ31A,31Bは、電流変調を容易に行うことができ、特に大面積の表示装置に用いる場合には大電流を発光素子列に供給することができる。さらに、縦型有機トランジスタ31A,31Bには、光吸収層又は光反射層を施す等の遮光処理がなされていることが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく高速バイポーラトランジスタと高耐圧バイポーラトランジスタを同一半導体基板上に形成し、高耐圧バイポーラトランジスタを使用する回路の歪特性を低減できる半導体装置の製造方法の提供。

【解決手段】半導体基板101上に、コレクタの一部となる埋込み領域102を、第1、第2のバイポーラトランジスタの形成領域に同一工程で形成し、エピタキシャル層104を形成し、第1の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の全体に形成し、第2の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の1箇所に埋込み領域を形成しない領域を有して形成する。第2の縦型バイポーラトランジスタの埋込み領域を形成しない領域では、周囲からの不純物の拡散により、縦方向の拡散拡がり量が連続的に狭くなり、埋込み領域を形成しない領域が形成される。

(もっと読む)

半導体装置の製造方法

【課題】抵抗が増加するのを抑制するとともに、高速応答性(高周波特性)が低下するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、p型シリコン基板1上にイオン注入による欠陥の増加を抑制する窒化膜30を形成する第1工程と、窒化膜30上からイオンを注入し、p型シリコン基板1表面にソース領域12およびドレイン領域13などの素子活性領域を形成する第2工程と、窒化膜30を除去する第3工程と、素子活性領域の界面準位の上昇を抑制する第1酸化膜5を素子活性領域上に形成する第4工程とを含む半導体装置の製造方法であって、窒化膜30は、第1酸化膜5よりも欠陥の増加を抑制でき、第1酸化膜5は、窒化膜30よりも界面準位の上昇を抑制できることを特徴とする。

(もっと読む)

複合半導体装置

【課題】同一の半導体層上に、半導体素子とセンサ素子とが形成され、半導体素子の温度が、高い応答速度でセンサ素子により検出される複合半導体装置を提供すること。

【解決手段】同一の半導体層上に、FRDとSBDとが並存するように形成した複合半導体装置は、

FRD11が、N型の第1半導体層1と、第1半導体層1上に島状に形成され、且つ、第1半導体層1とPN接合が形成されるP型の第2半導体層2と、第2半導体層2上に形成され第2半導体層2と電気的に接続される第1電極5と、で構成され、

SBD12が、第1半導体層1と、第1半導体層1上に形成され、且つ、第1半導体層1との間にショットキー接合が形成される第2電極6と、で構成され、

第2電極6、又は、第2電極6と接触する伝熱板が、平面的に見て第1電極5と重なるように延伸して形成されている。

(もっと読む)

バイポーラ型の半導体装置およびその製造方法

【課題】高い信頼性を持つ車載用高耐圧のバイポ−ラ型半導体装置を提供する。

【解決手段】面方位(111)オフアングル 3〜4°の支持基板上に活性領域をエピタキシャル成長させたエピ基板を用いて形成した高耐圧バイポ−ラ型半導体装置(以下、高耐圧BIP−IC)において、コンタクト孔底部および、接合分離層上面を除き、高耐圧BIP−IC表面を減圧熱分解CVD法により形成した薄い窒化シリコン膜(下層)と薄い酸化膜シリコン(上層)の積層膜で被覆することにより、保護膜として用いるプラズマCVDによる窒化シリコン膜(以下、プラズマ窒化シリコン膜)中の水素に起因したフィ−ルド部の寄生MOSのしきい値:フィ−ルドVtの低下を抑止し回路誤動作の防止するとともに、前記薄い窒化シリコン膜と薄い酸化膜シリコンの積層膜をコンデンサ膜の一部として用いることによりコンデンサの信頼性を向上せしめる。

(もっと読む)

半導体プロセスおよび集積回路

【課題】バイポーラおよびMOS、受動素子を含む集積回路の製造方法において、MOS、受動素子を絶縁膜で覆った後に、バイポーラのベース以降の工程を行うことを特徴とする半導体装置を提供する。

【解決手段】基板にバイポーラ・トランジスタの能動領域及びMOS素子の能動領域41を形成し、能動領域の周りに水平面において絶縁領域81を形成し、MOS素子の能動領域上にMOSゲート領域111、112を形成し、MOSゲート領域及びトランジスタの能動領域41上に絶縁材料層141を形成し、絶縁層141の残りの部分がバイポーラ・トランジスタの能動領域を部分的に覆うように、絶縁層141に開口143を形成することにより、トランジスタの能動領域内にベース領域を画定する。絶縁層141は、MOSゲート領域上に残り、後続の製造工程の間MOSゲート領域を密閉及び保護する。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

センサチップ

【課題】静電気等による帯電から回路素子を保護し、回路素子の特性不良を防止できると共に、安価に製造することのできるセンサチップを提供する。

【解決手段】センサ素子31と該センサ素子31の制御回路32とが同じ半導体基板10に形成されてなるセンサチップ100であって、制御回路32が、半導体基板10においてPN接合分離された複数の回路素子32a,32bを有してなり、複数の回路素子32a,32bのうち、少なくとも1個の回路素子上に、該回路素子を取り囲む導電膜21,22が形成され、該導電膜21,22が、所定の電位V1,V2に固定されてなるセンサチップ100とする。

(もっと読む)

半導体装置およびその製造方法

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置の品質評価方法および製造方法

【課題】最終製品での電気特性検査において半導体装置の歩留まりが低下するのを抑制することが可能な半導体装置の品質評価方法を提供する。

【解決手段】この半導体装置(安定化電源用IC)の品質評価方法は、n型エピタキシャル層13およびアノードショットキー電極層27からなるショットキーバリアダイオードの電気特性を測定する工程と、アノードショットキー電極層27と同時に形成され、半導体層(n+型エミッタ拡散層17、p+型ベース拡散層15b、n+型コレクタ補償拡散層18およびp+型ベース拡散層19a〜19d)にそれぞれオーミック接触されるオーミック電極層(エミッタオーミック電極層23、ベースオーミック電極層24、コレクタオーミック電極層25および抵抗オーミック電極層26a〜26d)の品質を、ショットキーバリアダイオードの電気特性により評価する工程とを備えている。

(もっと読む)

合併したバイポーラ回路およびCMOS回路とその製造法

【課題】高特性の合併したバイポーラ回路とCMOS回路とをCMOS処理工程だけのコストで製造する方法および回路を提供する。

【解決手段】BiCMOS集積回路を製造する方法は、バイポーラ・トランジスタのベース領域211とNチヤンネルMOSトランジスタのP形ウエル212とを1つの注入段階で作成する段階と、バイポーラ・トランジスタのコレクタ接触体ウエル213とPチヤンネルMOSトランジスタのN形ウエル208とを1つの注入段階で作成する段階とを有する。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの電極形成時に、MOSトランジスタを覆う層間絶縁膜上のポリシリコン膜のエッチング残りの発生を低減可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)バイポーラトランジスタ5とMOSトランジスタ6a、6bとが形成された半導体基板51を覆うように層間絶縁膜65を形成する工程と、(b)層間絶縁膜65を平坦化する工程と、(c)層間絶縁膜66におけるバイポーラトランジスタ5の電極70用の開口部68を形成する工程と、(d)層間絶縁膜66及び開口部68を覆うようにポリシリコン膜69を形成する工程と、(e)層間絶縁膜66上のポリシリコン膜69をエッチバックして、開口部68内に電極70を形成する工程とを具備する。

(もっと読む)

垂直型電流制御型シリコン・オン・インシュレータ(SOI)デバイス及びそれを形成する方法

【課題】 CMOS集積回路(IC)のための静電放電(ESD)保護デバイスとして用いるのに適した電流制御シリコン・オン・インシュレータ(SOI)デバイスを提供すること。

【解決手段】 垂直型シリコン制御整流器(SCR)、垂直型バイポーラ・トランジスタ、垂直型キャパシタ、抵抗器及び/又は垂直型ピンチ抵抗器のようなデバイスを有するシリコン・オン・インシュレータ(SOI)集積回路(IC)チップ、及びそれらのデバイスを作製する方法である。デバイスは、SOI表面層及び絶縁体層を通って基板に達するシード孔内に形成される。例えばN−型埋め込み拡散部が、基板内のシード孔を通って形成される。ドープされたエピタキシャル層が、埋め込み拡散部上に形成され、このドープされたエピタキシャル層は、例えばP−型層及びN−型層などの多数のドープ層を含むことができる。ドープされたエピタキシャル層上に、例えばP−型のポリシリコンを形成することができる。コンタクト・ライナ内に、埋め込み拡散部へのコンタクトが形成される。

(もっと読む)

3次元クロスバーアレイシステム、並びに3次元クロスバーアレイ接合部に情報を書き込む方法及び3次元クロスバーアレイ接合部に格納された情報を読み出す方法

本発明の様々な実施形態は、3次元クロスバーアレイ(500,1000)を対象とする。本発明の一態様では、3次元クロスバーアレイ(1000)は、複数のクロスバーアレイ(1102〜1104)と、第1のデマルチプレクサ(1106)と、第2のデマルチプレクサ(1108)と、第3のデマルチプレクサ(1110)とを含む。各クロスバーアレイは、ナノワイヤ(702〜704)の第1の層、ナノワイヤの第1の層に重なるナノワイヤ(706〜708)の第2の層、及びナノワイヤの第2の層に重なるナノワイヤ(710〜712)の第3の層を含む。第1のデマルチプレクサは、各クロスバーアレイのナノワイヤの第1の層におけるナノワイヤをアドレス指定するように構成され、第2のデマルチプレクサは、各クロスバーアレイのナノワイヤの第2の層におけるナノワイヤをアドレス指定するように構成され、第3のデマルチプレクサは、各クロスバーアレイのナノワイヤの第3の層におけるナノワイヤに信号を供給するように構成される。 (もっと読む)

第二のポリ層の形成後に二重ポリバイポーラトランジスタの2つのレベルをドーピングするプロセス

【課題】

単結晶半導体材料よりエミッタドーパントに対して少なくとも1桁大きい材料の層の速い横方向拡散特性を用いる減少されたマスクの組とインプラントの複雑さを有する(高周波数応用)相補的バイポーラトランジスタ構造の製造プロセスを提供する。

【解決手段】

別のベースとエミッタポリ層がドープされずに形成される。それからあるデバイスのエミッタポリと他のデバイスのベースポリのエッジとはドーパントマスクを介して露出され、同時にドープされる。エミッタドーパントはエミッタポリの表面内に直接入り、ここでそれはベース上に位置し、それと接触している。ベース接触ドーパントは外因性ベースを形成するために高い拡散係数を有する材料の層を含むベースポリのエッジ内に入り、その層を通り抜けて迅速に横方向に拡散し、それからコレクタ材料(例えばアイランド)表面内に下方に拡散する。第二のマスクは第二のデバイスのエミッタと第一のデバイスのベースポリのエッジを露出するようパターン化され、それからドープされる。

(もっと読む)

BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタ

【課題】BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタを提供する。

【解決手段】隆起した外因性自己整合型ベースを有する高性能バイポーラ・トランジスタが、CMOSデバイスを含むBiCMOS構造と統合される。パッド層を形成して、先在するCMOSデバイスのソースおよびドレインに対して真性ベース層の高さを隆起させることにより、かつ選択的エピタキシを介して外因性ベースを形成することにより、表面の凹凸の影響は、外因性ベースのリソグラフィによるパターン形成時に最小になる。また、バイポーラ構造の製作の間に、化学機械研磨プロセスを使用しないことにより、プロセス統合の複雑さが軽減される。内側のスペーサまたは外側のスペーサが、エミッタからベースを分離するために形成されうる。パッド層、真性ベース層、および外因性ベース層は、一致した外側の側壁表面を有するメサ構造を形成する。

(もっと読む)

ホットエレクトロントランジスタおよびそれを含む半導体装置

【課題】期待される高周波特性を得ること、ならびに後続の回路で必要とされる駆動電流を得ることが可能なホットエレクトロントランジスタを提供する。

【解決手段】このホットエレクトロントランジスタ100は、コレクタ層3と、ベース層5と、エミッタ層7と、コレクタ層3とベース層5との間に形成されたコレクタバリア層4と、ベース層5とエミッタ層7との間に形成されたエミッタバリア層6とを備えている。そして、エミッタバリア層6とエミッタ層7との間のエネルギー障壁は実質的に存在しないとともに、コレクタバリア層4のエネルギー障壁の高さはエミッタバリア層6のエネルギー障壁の高さよりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、分離領域を構成するP型の埋込拡散層の横方向拡散幅が広がる等により、分離領域の形成領域が狭め難いという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板6上にエピタキシャル層7が形成されている。基板6及びエピタキシャル層7には、分離領域1、2、3が形成され、複数の素子形成領域に区分されている。分離領域1は、P型の埋込拡散層8、9及びP型の拡散層10が連結し、形成されている。そして、P型の埋込拡散層8とP型の拡散層10との間にP型の埋込拡散層9が配置されることで、P型の埋込拡散層8の横方向拡散幅W1が狭められる。この構造により、分離領域1の形成領域が狭められる。

(もっと読む)

半導体装置およびその製造方法

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

21 - 40 / 84

[ Back to top ]