Fターム[5F082EA45]の内容

Fターム[5F082EA45]の下位に属するFターム

局部的アニール

Fターム[5F082EA45]に分類される特許

1 - 20 / 21

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

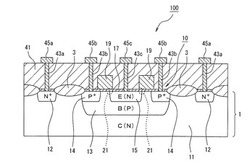

半導体装置の製造方法及び半導体集積回路装置

【課題】本発明は、簡素な工程で、デバイスの特性を均一化することができる半導体装置の製造方法及び半導体集積回路装置を提供することを目的とする。

【解決手段】半導体基板40の表面の所定領域41に、LOCOS酸化膜70を形成するLOCOS酸化膜形成工程と、

該LOCOS酸化膜70と前記半導体基板40の表面の境界を覆うように、ポリシリコン膜90を形成するポリシリコン形成工程と、

該ポリシリコン膜90をマスクとして、前記半導体基板40の表面にイオンの打ち込みを行い、前記半導体基板40の表面に、不純物領域60を形成するイオン打ち込み工程と、を含むことを特徴とする。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】単結晶Siの基板と、基板の上に形成され、開口領域を有する絶縁層と、開口領域の基板上にエピタキシャル成長されたGe層と、Ge層の上にエピタキシャル成長されたGaAs層と、を備え、Ge層は、超高真空の減圧状態にできるCVD反応室に基板を導入し、原料ガスを熱分解できる第1温度で第1のエピタキシャル成長を実施し、第1温度より高い第2温度で第2のエピタキシャル成長を実施し、第1および第2のエピタキシャル成長を実施したエピタキシャル層をGeの融点に達しない第3温度で第1のアニールを実施し、第3温度より低い第4温度で第2のアニールを実施して形成された半導体基板を提供する。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、低温下で結晶性の良好な単結晶および多結晶を提供することを目的とする。また、本発明は、固相成長法を用い、信頼性の高い半導体装置を提供することを目的とする。

【解決手段】

本発明では、非晶質半導体薄膜を基板あるいは絶縁膜上に堆積するにあたり、特に、その膜を構成する主元素からなる非晶質膜の平均原子間隔分布が、単結晶の平均原子間隔分布にほぼ一致するように形成し、これに再結晶化エネルギーを付与し固相成長を行い単結晶半導体薄膜3を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の中の不純物領域を熱拡散する際に、その横方向拡散を抑制して半導体集積回路の微細化を実現する。

【解決手段】絶縁膜2上に第2のホトレジスト5を形成する。第2のホトレジスト5は、P型の不純物領域4の両側に、P型の不純物領域4に部分的にオーバーラップする領域に第2の開口部K2を有するように形成される。第2のホトレジスト5をマスクとして、絶縁膜2をエッチングし、更にその下の半導体基板1の表面をエッチングすることで、P型の不純物領域4を部分的に除去する。そして、第2のホトレジスト5をマスクとして、P型の不純物領域4が除去された半導体基板1の表面に、リン(P+)をイオン注入して、P型の不純物領域4に隣接したN型の不純物領域6を形成する。その後、第2のホトレジスト5を除去した後に、P型の不純物領域4及びN型の不純物領域6の熱拡散を行う。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタと抵抗素子とを備える半導体装置の製造工程を簡素化することが可能な技術を提供する。

【解決手段】NMOSトランジスタが形成される活性領域AR4と、拡散抵抗素子が形成される活性領域AR5とを半導体層2に区画する素子分離構造3を当該半導体層2に形成する。その後、n型のソース・ドレイン領域33を活性領域AR4に形成する。そして、得られた構造に対して、その上方からマスクレスでp型不純物102pを導入して、活性領域AR5に抵抗素子として機能する不純物領域を形成する。このとき、ソース・ドレイン領域33内からはみ出すことなく、かつソース・ドレイン領域33のうちp型不純物102pが導入される領域での導電型がn型を維持するように、活性領域AR4に対してp型不純物102pが導入される。

(もっと読む)

半導体装置の製造方法

【課題】高精度のセルフアライメント構造を形成して半導体層に拡散層を形成する不純物元素のイオン注入を行うことにより、特性の向上を図る半導体装置を製造する半導体装置の製造方法を提供する。

【解決手段】各拡散層形成領域7〜9を相互に位置決めするイオン注入制御開口部13〜14を形成する工程を施した後に、各拡散層毎にイオン注入開口部29,30を形成するイオン注入マスク層形成工程と、各イオン注入開口部から不純物元素をイオン注入して各拡散層を形成する拡散層形成工程を実施する。イオン注入制御開口部が各拡散層形成工程におけるセルフアライメント構造を構成して各拡散層が形成される。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタを用いたESD保護回路の面積効率を向上する。

【解決手段】集積回路は、回路用バイポーラトランジスタ124を含む内部回路121と、内部回路121をサージから保護するための保護用バイポーラトランジスタ120とを備え、保護用バイポーラトランジスタ120におけるエミッタとベースとは短絡されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 結晶欠陥の発生を防止することができる半導体装置及び半導体装置の製造方法を実現する。

【解決手段】 SOI基板11に形成され、トレンチ11eにより分離された複数の素子形成領域内に、バイポーラトランジスタ12及びCMOS13を形成するBiCMOSである半導体装置10において、バイポーラトランジスタ12の表面のみを覆って形成された耐酸化膜19を備えているため、CMOS13に熱酸化法によりゲート酸化膜24及びゲート保護膜26を形成する際にも、バイポーラトランジスタ12の表面を熱酸化しないようにすることができる。これによれば、高濃度のイオンが注入されたコレクタ16、エミッタ17などのイオン注入領域が、熱酸化されることがないので、結晶欠陥の発生を防止することができる。

(もっと読む)

半導体装置

【課題】正孔の移動を十分に抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置(npn型のバイポーラトランジスタ100)は、n型コレクタ層2と、p+拡散層4、SiGe層5およびp型シリコン膜6からなるベース層と、n型エミッタ層8と、n型コレクタ層2とn型エミッタ層8との間に形成され、電子または正孔のいずれか一方に対する電位障壁としての効果を有する電荷移動防止膜7とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 相補型バイポーラトランジスタで、PNPトランジスタとNPNトランジスタの両方のエミッタ領域を多結晶シリコン膜から添加された不純物を同時に拡散させながら、その拡散深さを同程度で目標の浅い拡散層を形成し、しかも他の拡散層に影響を与えることなく、高特性の相補型のバイポーラトランジスタを得るための製造方法を提供する。

【解決手段】 PNPトランジスタのエミッタ領域を形成する部分の多結晶シリコン膜9にボロンイオンを注入し、イオン注入されたボロンを低温の熱処理により、多結晶シリコン膜内に拡散し、NPNトランジスタのエミッタ領域を形成する部分の多結晶シリコン膜9にリンイオンを注入し、高温で短時間の熱処理を行うことにより、多結晶シリコン膜中のボロンイオンおよびリンイオンをそれぞれPNPとNPNのトランジスタのベース領域7、8中に同時に拡散して、それぞれのエミッタ領域16、17を形成する。

(もっと読む)

薄膜半導体装置、ラテラルバイポーラ薄膜トランジスタ、ハイブリッド薄膜トランジスタ、MOS薄膜トランジス、及び薄膜トランジスタの製造方法

【課題】ガラス基板上にMOSトランジスタと、バイポーラトランジスタを同時に集積できる素子構造および製法を提供する。

【解決手段】絶縁基板(101)上に形成された半導体薄膜(105)に形成されたエミッタ(102)、ベース(103)、およびコレクタ(104)を有するラテラルバイポーラトランジスタ(100)において、半導体薄膜(105)が所定の方向に結晶化された半導体薄膜であるラテラルバイポーラトランジスタ。また、絶縁基板上に形成された半導体薄膜に形成されたMOS−バイポーラハイブリッドトランジスタ(200)において、半導体薄膜(205)は所定の方向に結晶化された半導体薄膜であるMOS−バイポーラハイブリッドトランジスタ。

(もっと読む)

バイポーラ接合トランジスタおよびその形成方法

【課題】バイポーラ接合トランジスタ(BJT)を提供すること。

【解決手段】各BJTのコレクタ領域は、半導体基板表面内に配置され、第1のシャロー・トレンチ・アイソレーション(STI)領域に隣接している。第2のSTI領域が形成され、この第2のSTI領域は、第1のSTI領域とコレクタ領域との間に延在し、約90°以下のアンダーカット角度で活性ベース領域の一部をアンダーカットする。例えば、第2のSTI領域は、約90°未満のアンダーカット角度のほぼ三角形の断面を有していても、約90°のアンダーカット角度のほぼ長方形の断面を有していてもよい。このような第2のSTI領域は、コレクタ領域の上側表面内に形成される多孔質表面部を使用して製作することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子の耐圧特性と制御用半導体素子のデバイスサイズの縮小化とを実現することが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上にN型のエピタキシャル層4が形成されている。基板3とエピタキシャル層4には、N型の埋込拡散層9がP型の埋込拡散層6上に形成されている。この構造により、P型の埋込拡散層6の這い上がりが抑制され、パワー用半導体素子の耐圧特性を維持しつつ、エピタキシャル層4の厚みを薄くすることができる。そして、制御用半導体素子のデバイスサイズを縮小化することができる。

(もっと読む)

半導体装置

【課題】 半導体装置において、反転領域対策を、既存の製造工程の条件を変えないで実現することを課題とする。

【解決手段】 N型エピタキシャル層4上にP型拡散層よりなる抵抗素子5が形成してあり、N型エピタキシャル層4上にシリコン酸化膜40が形成してあり、抵抗素子5の端から出ているアルミニウム配線8,9がシリコン酸化膜40上を延在している。シリコン酸化膜40は、N型エピタキシャル層4内に食い込んで厚みが増してある厚み付加部分42を枠状に有する。厚み付加部分42は、シリコン酸化膜40の反転電圧を上げる。厚み付加部分42は酸素イオンの注入及びアニール処理によって形成される。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの電流増幅率hFEに影響を与えることなく、ツェナーダイオードのツェナー電圧Vzのみを高精度に調整することのできる、低コストの製造方法を提供する。

【解決手段】バイポーラトランジスタT2とツェナーダイオードD2が同一半導体基10上に形成されてなる半導体装置100の製造方法であって、バイポーラトランジスタT2を構成するp導電型およびn導電型の拡散領域とツェナーダイオードD2を構成するp導電型およびn導電型の拡散領域を、それぞれ、同じ拡散工程K2,K3を用いて形成すると共に、熱処理工程L1において、拡散工程K2,K3終了後の半導体基板10を、窒素雰囲気中、500℃以上、900℃以下の温度範囲で熱処理する。

(もっと読む)

1 - 20 / 21

[ Back to top ]