Fターム[5J022CF08]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | スイッチング回路 (649) | マルチプレクサ (274)

Fターム[5J022CF08]に分類される特許

1 - 20 / 274

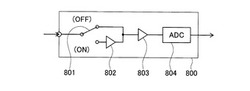

信号切替回路およびA/D変換装置

レベル調整装置、およびレベル調整のためのプログラム

【課題】ユーザに負担をかけることなく、容易にアナログ音響信号の音質劣化を抑制することが可能なレベル調整装置を提供すること。

【解決手段】入力ポートはアナログ入力ブロック800を有し、アナログ入力ブロック800は、迂回スイッチ801、固定ゲインにて信号レベルの減衰を行うパッド802、可変ゲインにて信号レベルを増幅又は減衰して調整するアンプ803を備える。迂回スイッチ801はパッド802とアンプ803により信号レベルが調整されるパッドオン状態とアンプ803のみで信号レベルが調整されるパッドオフ状態を切り替えられる。信号レベルの調整の後に、パッドオン状態で、かつパッドのオン・オフの何れの状態でもゲインの調整が可能な重複範囲ROVの範囲内である入力ポートを抽出し、該当する入力ポートのアナログ入力ブロック800に対して、パッドオフ状態への切り替え調整処理を行う。

(もっと読む)

タイムインタリーブ型サンプラのアレイを有する無線周波数(RF)サンプリング装置およびシナリオベースの動的資源割り当てのための方法

【課題】RFサンプリングシステムの動的資源割り当てのための方法および装置を提供すること。

【解決手段】

受信した無線周波数(RF)信号から、タイムインタリーブされた複数のサンプルを生成し、そのタイムインタリーブされた複数のサンプルを組み合わせて信号品質を生成することにより決定された信号品質測定値に基づいた、RFサンプリングシステムの動的資源割り当てのための方法および装置。

(もっと読む)

二次電池の状態検知装置、二次電池の状態検知装置のための故障診断方法

【課題】故障診断用の電圧が変動した場合でも、精度良くADコンバータの故障診断を実施する二次電池の状態検知装置を提供する。

【解決手段】二次電池の状態検知のために検出されたアナログ値をデジタル値に変換する複数のADコンバータ(18−20)を備えた二次電池の状態検知装置において、前記複数のADコンバータの故障診断時に、故障診断用電圧を同時に前記複数のADコンバータへ入力するための故障診断用電源(15)と、前記複数のADコンバータの出力値を相互に比較して故障の判定を行う演算部(16)と、を備えた。

(もっと読む)

アナログ入力回路またはアナログ/ディジタル変換装置

【課題】制御電源のON、OFFの状態に関係なく、また外部に放電用機材が無くてもフィルタ回路、フライングキャパシタ回路内コンデンサの放電を短時間で可能にするためのアナログ入力回路またはアナログ/ディジタル変換装置を提供する。

【解決手段】縦列接続されたフィルタ回路とフライングキャパシタ回路を複数組備え、複数組のフライングキャパシタ回路の後段を増幅器の入力端子に共通に接続し、増幅器の後段にアナログ/ディジタル変換器を備えるとともに、外部制御電源に接続された基板上に構成されたアナログ/ディジタル変換装置において、フィルタ回路とフライングキャパシタ回路は、並列コンデンサとこれに並列に接続された抵抗と常閉接点の直列回路とを備えており、常閉接点は、制御電源の端子間に接続され、制御用接点を介して励磁される補助リレーにより駆動されているアナログ/ディジタル変換装置。

(もっと読む)

アナログデジタル変換装置及び信号処理システム

【課題】アナログデジタル変換装置のサイズを縮小し、且つ、インタリーブ間のミスマッチに起因する誤差の補正に必要な処理量を低減する。

【解決手段】本発明の実施形態のアナログデジタル変換装置は、アナログ入力信号をデジタル出力信号に変換する。アナログデジタル変換装置は、アナログデジタル変換ユニット12と、疑似エイリアス信号生成部114と、利得制御部116と、エイリアス信号補正部118と、を備える。アナログデジタル変換ユニット12は、アナログ入力信号を、複数のデジタル信号に変換する。疑似エイリアス信号生成部114は、複数のデジタル信号を合成した合成信号に含まれるエイリアス信号成分を模擬する疑似エイリアス信号を生成する。利得制御部116は、疑似エイリアス信号を用いて、デジタル出力信号の利得を制御する利得制御信号を生成する。エイリアス信号補正部118は、利得制御信号を用いて、エイリアス信号成分を補正する。

(もっと読む)

アナログ‐デジタル変換器及びアナログ信号をデジタル信号に変換する方法

【課題】製造ばらつきによる誤動作が少ないAD変換器を提供することを目的とする。

【解決手段】本発明に係るAD変換器1は、アナログ入力信号を所定の分解能を有するデジタル信号に変換するサイクリック型のアナログデジタル変換器であって、入力される第1アナログ信号の大きさとしきい値とを比較して該比較結果を示すデジタル値を出力する比較部13と、第1アナログ信号を1よりも大きく2よりも小さいβ倍に増幅するとともに比較部の比較結果に応じて所定の演算を実行して第2アナログ信号を出力するMDAC部14とを備えるデジタル近似部10と、MSBを演算するときはアナログ入力信号を、又MSBを演算するとき以外は第2アナログ信号を第1アナログ信号として出力するマルチプレクサ20と、βの値を推定するβ推定部30と、比較部が出力するデジタル値を順次取り込んでデジタル信号として出力するデジタル信号出力部40とを有する。

(もっと読む)

AD変換回路および撮像装置

【課題】カウントした計数値の誤差の発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ104から出力される上位用カウントクロックに基づいてカウントを行って第2の上位計数値を取得する。変更部103は、上位カウンタ101のカウントクロックの切換えの際に、カウントクロックの論理状態を所定の状態に変更する。

(もっと読む)

逐次比較型AD変換器及びその制御方法

【課題】SubDACの出力端子につながる4端子コンパレータのトランジスタのゲート容量が所望の容量比となるように制御して補正し、高精度化を可能とする逐次比較型AD変換器を提供する。

【解決手段】探索範囲を設定するデジタル値DSRを受け、対応する電圧を出力するMainDAC102,103と、探索範囲を設定するための制御信号を受け、対応する電圧を出力するSubDAC101と、MainDAC102,103とSubDAC101からの電圧の比較を行う4端子コンパレータ105,107、MainDAC+(102)と、MainDAC−(103)の出力電圧を比較するコンパレータ106と、切替制御信号に基づきSubDAC101の出力A1,B1,D1,E1又はコモン電圧VCMに切り替えるセレクタ104と、セレクタ104に切替制御信号を与える逐次比較レジスタロジック108を備える。

(もっと読む)

電子制御装置

【課題】マルチプレクサの切り替えによってフィルタ回路の収束時間が変化したとしても正確な出力信号を取得することができる電子制御装置を提供する。

【解決手段】電子制御装置は、複数の信号を選択的に出力信号として出力するマルチプレクサ27を備えている。また、マルチプレクサ27の後段に接続され、マルチプレクサ27が前回出力した出力信号が示す電圧値とマルチプレクサ27が今回出力した出力信号が示す電圧値との電圧差に応じた収束時間で今回の出力信号を出力するフィルタ回路28を備えている。さらに、マルチプレクサ27の切り替え制御を行ってフィルタ回路28から出力信号を取得するマイコン24を備えている。そして、マイコン24は、マルチプレクサ27の切り替えにおけるフィルタ回路28の収束時間に合わせて、マルチプレクサ27の接続先毎に異なる切り替え時間を設定する。

(もっと読む)

信号処理装置

【課題】複数のAD変換器を用いて同一のアナログ信号をAD変換する信号処理装置において、個々のAD変換器の特性のばらつきによって生じる同一のアナログ信号のAD変換精度の低下を抑制する。

【解決手段】クロック生成部58はπ[rad]位相の異なる二つのクロックを生成し、対象信号供給部52は受信信号RSまたは0VのいずれかをAD変換部68の二つのAD変換器72、74に供給する。被補正データ生成部86は、AD変換部68が受信信号RSをAD変換した結果に基づき、読出データRDを生成する。オフセットデータ生成部76は、AD変換部68が基準電圧をAD変換した結果に基づき、AD変換器72、74毎の測定誤差を表すオフセットデータAZ1、AZ2を生成する。補正部100は、読出データRDからオフセットデータAZ1、AZ2分を除去する補正処理を実行し、サンプリングデータSDを生成する。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

AD変換装置およびDC−DC変換装置

【課題】基準となる二つのアナログ信号を必要とせずに、単相差動変換を含むAD変換装置におけるDCオフセットをキャンセルする。

【解決手段】本発明の一態様としてのAD変換装置は、参照電圧信号を受ける第1端子と、前記参照電圧信号を単相差動変換して第1差動信号を得る単相差動変換回路と、前記参照電圧信号に基づき、前記第1差動信号をAD変換して第1デジタル信号を得るAD変換器と、前記第1デジタル信号と、所定コードを表すデジタル信号との差分であるDCオフセットを検出するデジタル回路と、入力信号を受ける第2端子と、を備え、前記単相差動変換回路は、前記入力信号を単相差動変換して第2差動信号を取得し、前記AD変換器は、前記参照電圧信号に基づき、前記第2差動信号をAD変換して第2デジタル信号を取得し、前記デジタル回路は、前記第2デジタル信号から前記DCオフセットを減算してい第3デジタル信号とし、前記第3デジタル信号を出力する。

(もっと読む)

アナログ/デジタル変換回路及び半導体装置

【課題】アナログ/デジタル変換器のより詳細な故障診断のための技術を提供する。

【解決手段】アナログ/デジタル変換回路(100〜108)は、入力されたアナログ信号(x、15)を所要の演算式(f(x))にしたがって診断用に演算する演算部(12)と、前記入力されたアナログ信号(x)又は前記演算部によって演算されたアナログ信号(y)のいずれかを選択する第1選択部(11)と、前記第1選択部によって選択されたアナログ信号をデジタル信号に変換する変換部(10、21、22、23)とを有する。

(もっと読む)

逐次比較型AD変換方法および装置

【課題】システム全体でのオフセット補償とダイナミックレンジの確保を可能とするAD変換装置を提供する。

【解決手段】ブリッジセンサB1から非測定検出信号が入力するとき、第1のサイクルにおいて、高利得差動増幅器2の基準電圧VCOMとして初期値をセットして、逐次比較型AD変換本体部3でAD変換データを求める。・・・。第m(mは3以上の正の整数)のサイクルにおいて、第m−1のサイクルで得られたAD変換データの最上位ビットに応じて、AD変換データが零値に近づくように、基準電圧VCOMとして、第m−1の電圧を所定電圧だけ上昇又は下降させた第mの電圧をセットする。センサB1から実測定検出信号が入力するとき、基準電圧VCOMとして第mの電圧をセットしてAD変換データを求める。

(もっと読む)

アナログ−デジタル変換装置及びアナログ−デジタル変換方法

【課題】 複数の受信経路から供給されるアナログ信号を一装置でデジタル化することで、受信装置の大型化を回避でき、かつ、量子化雑音の増大を抑えることが可能なアナログ−デジタル変換装置を提供する。

【解決手段】 アナログ−デジタル(A/D)変換装置は、バンド選択部、第1及び第2の切替部、A/D変換部及びチャネル選択部を具備する。バンド選択部は、複数の入力チャネルからアナログ信号を受信し、各アナログ信号から所定の帯域幅で信号を抽出する。第1の切替部は複数の入力チャネルの受信経路との接続を切り替え、複数の抽出信号を多重する。A/D変換部は、第1の切替部から出力される多重信号を、所定サンプリング周波数でデジタル信号へ変換する。第2の切替部は、複数の送信経路との接続を順次切り替え、受信経路と対応する送信経路へデジタル信号を出力する。チャネル選択部は、供給されたデジタル信号を、所定のサンプルタイミングでリサンプルする。

(もっと読む)

信号入力回路の診断方法および装置

【課題】入力信号の電圧と基準電圧を選択してデジタル値に変換し、このデジタル値から故障箇所を特定する信号入力回路の診断装置では、診断項目を増やすと構成が複雑になり、かつ異常箇所を特定できなかった。本発明は簡単な構成で異常箇所を特定できる診断装置を提供することを目的にする。

【解決手段】マルチプレクサを用いて入力信号電圧、基準電圧、基準電圧を極性反転した電圧、同じ信号の差電圧を測定し、これらの電圧値から異常を診断するようにした。簡単な構成で種々の異常を検出でき、また故障箇所を特定できる。

(もっと読む)

データ・コンバータ・システム

【課題】データ・コンバータ・システムの出力信号中のスプリアス・トーンを減少させる。

【解決手段】入力信号を特定周波数帯域に制限し、オーバー・サンンプリングすることによって、変換された入力信号がスプリアス・トーンを跨ぐ又は回避するようにする。スプリアス・トーンはフィルタで除去しても良く、これによって、従来のデータ・コンバータよりきれいなSFDRの出力信号を供給できる。例えば、インタリーブ・データ・コンバータ・システムは、インタリーブされた複数のデータ・コンバータの1つの第2ナイキスト領域に制限された入力信号をインタリーブされた信号に変換し、このインタリーブ信号を、変換された入力信号周波数を通過させる通過帯域と、スプリアス・トーンを減衰させるストップ帯域とを有するフィルタでフィルタする。

(もっと読む)

フラッシュアナログ−デジタルコンバータ、方法及びシステム

【課題】動作中にバックグラウンドにおいてオフセット補償のための較正を行うことができるフラッシュアナログ−デジタルコンバータ(ADC)等を提供する。

【解決手段】フラッシュADCのコンパレータは、バックグラウンドにおいて、コンパレータをフィードバックループへ切り替え、コンパレータの現在の基準レベルを決定し、コンパレータの基準レベルを目標基準電圧へと調整するようコンパレータに結合されている基準キャパシタを充電することによって、較正される。

(もっと読む)

アナログデジタル変換器および信号処理システム

【課題】面積の増大を防止でき、かつサンプリングされるコース用ADCとファイン用ADC間のアナログ信号に誤差が生じることを抑止できるAD変換器および信号処理システムを提供する。

【解決手段】アナログ入力信号をNビットのデジタル信号に変換する際に、上位mビットのデジタル信号に変換するコース(Coarse)AD変換器と、コースAD変換器の変換結果に基づきアナログ入力信号の下位nビット(n=N-m)のデジタル信号に変換するファイン(Fine)AD変換器と、アナログ入力信号をサンプリングし、コース用参照電圧との比較電圧をコースAD変換器に供給し、ファインAD変換器の変換結果に応じたファイン用参照電圧との比較電圧を上記ファインAD変換器に供給するTH回路と、を含み、TH回路は、アナログ入力信号、コース用参照電圧、ファイン用参照電圧の選択的入力経路でサンプリング容量を共有する。

(もっと読む)

1 - 20 / 274

[ Back to top ]