Fターム[5J032AA00]の内容

論理回路 (717) | 素子 (216)

Fターム[5J032AA00]の下位に属するFターム

マルチ端子Tr(TTL入力部、I2L駆動部を除く) (1)

ダイオード (80)

コンデンサ(容量) (40)

その他 (52)

nPnトランジスタとPnPトランジスタの組合せ(I2Lを除く) (7)

FETとバイポーラTrの組合せ (17)

Fターム[5J032AA00]に分類される特許

1 - 19 / 19

半導体スイッチ回路

【課題】高いESD保護耐圧を確保しつつ、ESD保護素子の静電容量を極力小さくし、しかも、集積化の際における占有サイズを小さくする。

【解決手段】ESD保護回路103は、共通端子41とグランドとの間に設けられており、共通端子41側から順に、ESD保護スイッチ素子としての複数の直列接続された電界効果トランジスタ31−1〜31−4と、逆接続された一組のESD保護素子としてのダイオード32−1,32−2が直列接続されると共に、電界効果トランジスタ31−1〜31−4は、ゲートが相互に接続されてグランドに接続されており、ESD保護素子のダイオード32−1,32−2による静電容量を低減し、高いESD保護耐圧の確保が可能となっている。

(もっと読む)

誘導雷が原因の過電圧の抑制

直流電圧フリーかつ差動の、EIA−485/EIA−422準拠の、TTPプロトコルに従った信号伝送を備えたフィールドバスのバスライン(102)へのバス接続ユニット(101)のための結合回路であって、バス接続ユニット(101)の送信/受信コンポーネント(104)の両方の入力部/出力部(108、109)が信号発信装置(103)の第一のコイルと、およびバスライン(102)の両方の極が信号発信装置第二のコイルと、接続されており、第一のコイルが中心タップ(107)を備え、この中心タップ(107)がバス接続ユニット(101)のローカル規準ポテンシャルとコンデンサー(105)とを接続しており、このコンデンサーの容量が少なくとも発信装置(103)の寄生容量(110)の100倍である結合回路。 (もっと読む)

半導体集積回路

【課題】デジタル回路とアナログ回路とを混載して成る半導体集積回路において、前記デジタル回路によってメモリなどの外部負荷を駆動するにあたって、グランドバウンスによるアナログ回路への影響を抑えつつ、前記外部負荷がデジタル回路からの矩形波パルスを受信するにあたって、ON/OFF(「1」/「0」)判定のマージンを最大にする。

【解決手段】外部負荷3を駆動するメインドライバ回路7を、複数段のインバータINV1〜INV3を備える多段階電圧制御型のプリドライバ回路6を介して駆動するようにし、そのインバータINV1〜INV3の使用段数を切換え回路12で切換えられるようにする。そして、雑音検出回路13によって検出されるグランドバウンスのレベルが、小さいときにはインバータINV3のみを使用して前記矩形波パルスの鈍りを小さくし、大きいときにはインバータINV1〜INV3を使用して、グランドバウンスを抑える。

(もっと読む)

フリップフロップ、半導体集積回路、半導体デバイスおよびブレードサーバ

【課題】

回路オーバヘッドが小さく、かつ、ソフトエラーへの耐性が高い、高ソフトエラー耐性のフリップフロップおよび、それを用いた半導体集積回路を提供する

【解決手段】

ソフトエラーに対する耐性の異なる複数のラッチ回路と、前記複数のラッチ回路にクロックを供給するクロック分配部と、を備えたフリップフロップであって、前記複数のラッチ回路は、第一のラッチ回路と、前記第一のラッチ回路よりもソフトエラーに対する耐性の低い第二のラッチ回路の少なくとも2つのラッチ回路であることを特徴とするフリップフロップ。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】電源電圧を変更することなく、広い温度範囲でリーク電流を抑えて動作する半導体装置を提供する。

【解決手段】しきい値電圧が第1電圧である第1トランジスタを含む高VT部7と、しきい値電圧が第1電圧よりも低い第2電圧である第2トランジスタを含む低VT部8と、温度を測定し、温度が所定の温度より高い高温状態であるか、温度が所定の温度よりも低い低温状態であるかを判定し、高温状態を示す信号又は低温状態を示す信号を出力する温度検知部6と、高温状態を示す信号、又は低温状態を示す信号を受信し、高温状態を示す信号に基づいて高VT部7を動作させ、低温状態を示す信号に基づいて低VT部8を動作させる制御を行う制御部9とを具備する。

(もっと読む)

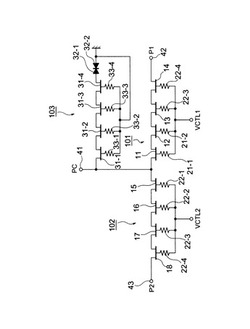

高周波スイッチ回路

【課題】高周波スイッチ回路を介して伝達される高周波信号の2次高調波歪を低減するとともに、静電気放電破壊耐性を確保する。

【解決手段】高周波スイッチ回路は、受信用の受信側トランスファ回路(11)と、送信用の送信側トランスファ回路(12)と、受信端子(1)への高周波信号の漏洩を防止する受信側シャント回路(13a)と、送信端子(2)への高周波信号の漏洩を防止する送信側シャント回路(14a)とを備える。受信側トランスファ回路を構成するSOI構造のMOSFET(101−104)として、蓄積型で動作するトランジスタを用いる。また、アンテナ端子(3)に対して、送信側シャント回路と同一のトランジスタ構成を有するESD保護回路(15)を接続する。

(もっと読む)

入力インタフェース回路、集積回路装置および電子機器

【課題】信号入力端子に静電気ノイズが印加された場合に、そのノイズの内部回路への伝達を未然に、かつ確実に防止することができる入力インタフェース回路を提供すること。

【解決手段】ノイズを検出するノイズ検出回路(200)と、ノイズが検出されたときに第1のスイッチ回路(SW1)をオフしてノイズ伝達を遮断する機能をもつノイズキャンセラ(300)と、を設ける。第1のスイッチ回路(SW1)がオフしているときは、第2のスイッチ回路(SW2)がオンして、直前の電圧をラッチする。ノイズ検出回路200に含まれるノイズ検出用トランジスタは、Nウエルの電位を適応的に最適化することができるフローティングNウエルトランジスタによって構成される。

(もっと読む)

I/O回路

【課題】 接地側のNMOSドライバを小さな面積で、かつ、接地側のNMOSドライバの活性化の遷移時間を短くし、接地側のNMOSドライバのゲート電圧をより確実に接地電位にするI/O回路を提供すること

【解決手段】 I/O回路1は、ドレインがパッドに接続される第1NMOSドライバ10と、第1NMOSドライバ10と異なるアクティブ領域に配置され、ドレインが第1NMOSドライバ10のソースに接続され、ソースが接地電位に接続される第2NMOSドライバ11と、内部電源電位のレベルを電源電位のレベルに変換するレベルコンバータと、ドレインがレベルコンバータの一方の出力端子に接続され、ソースが接地電位に接続され、ゲートがレベルコンバータの他方の出力端子に接続される第1NMOSトランジスタ26と、を備えており、第1NMOSトランジスタ26のドレインが第2NMOS11ドライバのゲートに接続されている。

(もっと読む)

バッファ回路及びその制御方法

【課題】出力スイッチング素子をオフ状態からオン状態に切り替えるタイミングを制御し、出力特性が不安定になることを抑制することができるバッファ回路及びその制御方法を提供する。

【解決手段】出力スイッチング素子M1、M2を駆動する駆動部20と、出力スイッチング素子M1、M2の制御端子の電圧値が、閾値電圧値を超過したことを検出する検出部30と、駆動部20に接続され、検出部30の検出結果に応じて、出力スイッチング素子M1、M2の駆動能力を変更する補助駆動部40と、を備える。

(もっと読む)

半導体集積回路装置

【課題】放射線に対する耐性を強化する。

【解決手段】PチャネルトランジスタP1はソースおよびバックゲートを電源に接続し、ゲートを入力端子INに接続し、ドレインを出力端子OUTに接続する。また、NチャネルトランジスタN1はソースおよびバックゲートを接地し、ゲートを入力端子INに接続し、ドレインを出力端子OUTに接続する。ダイオードD1はカソードを電源に接続し、アノードを出力端子OUTに接続する。ダイオードD2はカソードを出力端子OUTに接続し、アノードを接地する。インバータ回路が形成される基板の垂直方向から見て、ダイオードD1のp+拡散層32の領域の投影面がNチャネルトランジスタN1のn+拡散層24の領域の投影面を含み、ダイオードD2のn+拡散層41の領域の投影面がPチャネルトランジスタP1のp+拡散層14の領域の投影面を含むように配置する。

(もっと読む)

ラッチ回路

【課題】

本発明の課題は、論理回路が占める面積の増大が少なく、かつ、回路の反応速度の低下がないように、ソフトエラー耐性の強化を図ったラッチ回路を提供することにある。

【解決手段】

上記の課題を解決するため、反転回路から構成されており、2以上の入力端子を有するフィードバック回路と、フィードバック回路の入力端子に、クロックに同期して、入力信号又は入力信号と同相の信号を入力する入力回路と、を備え、フィードバック回路は、2以上の入力端子に、同時に入力信号又は前記入力信号と同相の信号が入力されたときのみ、入力端子に予め決められた増幅段数で正帰還がかかる構成となっていることを特徴とするラッチ回路を提供する。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】ゲート酸化膜の経時劣化が懸念されるデカップリング容量セルや修正用セルに対して用いるTDDB抑制回路の使用個数を削減し、チップ面積の増大を抑制する。

【解決手段】ソースが第1の電源配線に接続された第1のトランジスタQP1とソースが第2の電源配線に接続された第2のトランジスタQN2からなり、第1のトランジスタのドレインが第2のトランジスタのゲートに、第2のトランジスタのドレインが第1のトランジスタのゲートに接続されたTDDB抑制回路1と、ソースおよびドレインが第1の電源配線に接続され、ゲートがTDDB抑制回路1における第2のトランジスタのドレインに接続された第3のトランジスタQP3からなるデカップリング容量回路2と、TDDB抑制回路1の第1のトランジスタのドレインと第2のトランジスタのドレインにそれぞれ接続された第1および第2の出力端子OUT1,OUT2とを備える。

(もっと読む)

入出力バッファ

【課題】動作電源の供給時/非供給時に関わらず、外部から入力される電圧信号に対して回路を保護することのできる入出力バッファを提供すること。

【解決手段】入出力バッファは、外部から入力される電圧信号EBを高電位電源VDEに対応する適切な電位に変換して基準電源VD0を生成する電源作成回路16を備える。電源作成回路16は、ダイオード接続されたトランジスタPt11〜Pt15を備え、それらトランジスタPt11〜Pt15のバックゲートは高電位電源VDE及び低電位電源VSS以外の電位を持つノードに接続されている。これにより、高電位電源VDEの供給時/非供給時に関わらず、外部からの電圧信号EBの入力時には各トランジスタPt11〜Pt15のゲート−バックゲート間に高電圧が印加されることが防止される

(もっと読む)

タイミングコントローラチップ

【課題】電気的過剰ストレス(EOS)に対する耐久性を向上させることで、組立ラインでの不良な歩留まりを大幅に減少させ、且つ製造コストを低下させるタイミングコントローラチップを提供する。

【解決手段】本発明のタイミングコントローラチップは、第1の抵抗器と、第2の抵抗器と、第1の静電気放電(ESD)保護回路と、第2の静電気放電(ESD)保護回路と、演算増幅器と、を備えている。前記第1および第2の抵抗器は、それぞれ前記タイミングコントローラチップの第1および第2の低電圧差動信号(LVDS)入力ピンに電気的に接続されている。前記第1および第2の静電気放電(ESD)保護回路は、それぞれ第1および第2の抵抗器に電気的に接続されている。さらに、前記増幅演算器は、前記第1の抵抗器と前記第1のESD保護回路とに電気的に接続された非反転入力端子と、前記第2の抵抗器と前記第2のESD保護回路とに電気的に接続された反転入力端子とを有している。

(もっと読む)

プログラム可能な装置のための静電放電(ESD)保護機器

【課題】プログラム可能な装置用の静電放電(ESD)保護機器を提供する。

【解決手段】このESD保護機器は、ESDイベントによって誘発された障害からプログラム可能な装置を守るために、パッドからパワーシステムまでの電気経路に沿って高インピーダンスを提供し、また、通常の読み取り動作と書き込み動作の最中に、インピーダンスを故意に低減することができる。

(もっと読む)

異電源間インターフェースおよび半導体集積回路

【課題】ESD保護回路の占有面積を削減する。

【解決手段】複数の信号それぞれのデータを第1のコア電源E1の系統に属するパワーダウン領域10から第2のコア電源E2の系統に属するバックアップ領域20に転送する異電源間インターフェースであり、上記複数の信号それぞれのデータからなるパラレルデータをシリアルデータに変換するコマンドレジスタ101,アドレスレジスタ102,ライトデータレジスタ103,受信バッファ106と、上記シリアルデータの信号txをパワーダウン領域10側から1本の信号線に送信する送信バッファ106と、上記送信されたシリアルデータを上記信号線からバックアップ領域20側で受信する受信バッファ204と、上記受信されたシリアルデータをパラレルデータに戻すコマンドレジスタ201,アドレスレジスタ202,ライトデータレジスタ203,受信バッファ204とを備える。

(もっと読む)

半導体装置及びその冗長救済方法

【課題】 大規模化した半導体装置の歩留向上および信頼性向上が容易に図れるようにすること。

【解決手段】 制御回路108からの制御信号S(i)によって電流測定タイミングになると、各分割論理回路ブロック1051〜r−1の静止電源電流値が測定される。そして制御回路108は、分割論理回路ブロック1051〜r−1の静止電源電流値と基準値とを比較して、静止電源電流が基準値を超える場合、判定信号(i)をLoレベルに設定する一方、静止電源電流が基準値を超えないときは判定信号(i)をHiレベルに設定する。そして、判定信号(i)がLoレベルである不良ブロックを冗長回路ブロック105rと置換するように、セレクタ1062〜r,1071〜r−1に切替え制御信号R(1)〜R(r)を出力し、入出力バスの接続を切り替え、その不良ブロックへの電源供給も停止する。

(もっと読む)

ESD保護回路

【課題】 半導体装置をESD(サージ)からゲート絶縁膜を保護する保護機能を備えた半導体装置のための保護装置を提供する。

【解決手段】 分割されたGNDライン及び電源ラインを有するESD保護回路内における出力トランジスタ(6a、6b)のVCC端子13側又はGND端子12側の電極とゲート電極との間に、保護トランジスタを接続し、さらに、該保護トランジスタ(30a、30b)のゲート電極側に遅延回路(31a、31b)及び抵抗(32a、32b)を設けることにより、負方向の電圧が出力トランジスタ(6a、6b)に印加された場合であっても、出力トランジスタ(6a、6b)のゲート電極に電圧を印加し、ドレイン電流を放電し、ゲート絶縁膜の破壊を防止できる。

(もっと読む)

半導体回路

【課題】 耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】 一のpMOSトランジスタ11に、少なくとも1つの他のpMOSトランジスタ12又は少なくとも1つの他のpMOSトランジスタを備えた並列回路を直列に接続するとともに、pMOSトランジスタ11及び他のpMOSトランジスタ12のゲートに共通の信号が入力される第1の回路ブロック1、及び/又は、一のnMOSトランジスタ21に、少なくとも1つの他のnMOSトランジスタ22又は少なくとも1つの他のnMOSトランジスタを備えた並列回路を直列に接続するとともに、nMOSトランジスタ21及び他のnMOSトランジスタ22のゲートに共通の信号が入力される第2の回路ブロック2を備える半導体回路。

(もっと読む)

1 - 19 / 19

[ Back to top ]